From www.gearrice.com

smartphone autonomy will soar in 2023, here's why GEARRICE Arm Cortex Xpsr This ensures that attempts to. On an implementation that includes the dsp extension, the apsr.ge bits. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm core registers describes the flags. The flags are unknown on reset. Although there are restrictions on viewing and. The important bits are the top five: Arm Cortex Xpsr.

From www.youtube.com

Current Program Status Register CPSR of ARM processor ARM7 LPC2148 Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The important bits are the top five: Although there are restrictions on viewing and. This ensures that attempts to. The flags are unknown on reset. Arm core registers describes the flags. On an implementation that includes the dsp extension, the apsr.ge bits. Arm Cortex Xpsr.

From microcontrollerslab.com

Sequence of Interrupt Processing Steps ARM CortexM Microcontrollers Arm Cortex Xpsr The flags are unknown on reset. Although there are restrictions on viewing and. Arm core registers describes the flags. This ensures that attempts to. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm Cortex Xpsr.

From www.anandtech.com

Cortex A720 Middle Core, Big on Efficiency Arm Unveils 2023 Mobile Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. This ensures that attempts to. Arm core registers describes the flags. On an implementation that includes the dsp extension, the apsr.ge bits. The important bits are the top five: The flags are unknown on reset. Although there are restrictions on viewing and. Arm Cortex Xpsr.

From blog.csdn.net

汇编语言笔记ARM架构基本寄存器_xpsrCSDN博客 Arm Cortex Xpsr This ensures that attempts to. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. The flags are unknown on reset. The important bits are the top five: Although there are restrictions on viewing and. Arm core registers describes the flags. Arm Cortex Xpsr.

From www.youtube.com

10. Assembler ARM Cortex M SUBS CMP BNE BEQ xPSR CODE & EQU [ES Arm Cortex Xpsr The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. The flags are unknown on reset. This ensures that attempts to. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Although there are restrictions on viewing and. Arm core registers describes the flags. Arm Cortex Xpsr.

From xlwayjiyw.cocolog-nifty.com

ARM CortexM3システム開発ガイド CQ出版社 価格 小川新年の迎のブログ Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The important bits are the top five: Arm core registers describes the flags. On an implementation that includes the dsp extension, the apsr.ge bits. The flags are unknown on reset. Although there are restrictions on viewing and. This ensures that attempts to. Arm Cortex Xpsr.

From www.anandtech.com

Arm Cortex X4 Fastest Arm Core Ever Built Arm Unveils 2023 Mobile Arm Cortex Xpsr The important bits are the top five: 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. Although there are restrictions on viewing and. This ensures that attempts to. Arm core registers describes the flags. The flags are unknown on reset. Arm Cortex Xpsr.

From community.arm.com

Arm CortexM processors in DSP applications. Why not? Architectures Arm Cortex Xpsr Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm core registers describes the flags. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. The flags are unknown on reset. Arm Cortex Xpsr.

From uk.rs-online.com

STMicroelectronics STM32H563ZIT6, 32bit ARM Cortex M33 Microcontroller Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm core registers describes the flags. The flags are unknown on reset. Although there are restrictions on viewing and. This ensures that attempts to. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. Arm Cortex Xpsr.

From b.hatena.ne.jp

[B! CPU] Arm CortexA34 is a 64bit Only LowPower Core CNX Software Arm Cortex Xpsr Arm core registers describes the flags. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. This ensures that attempts to. The flags are unknown on reset. On an implementation that includes the dsp extension, the apsr.ge bits. The important bits are the top five: Although there are restrictions on viewing and. Arm Cortex Xpsr.

From blog.csdn.net

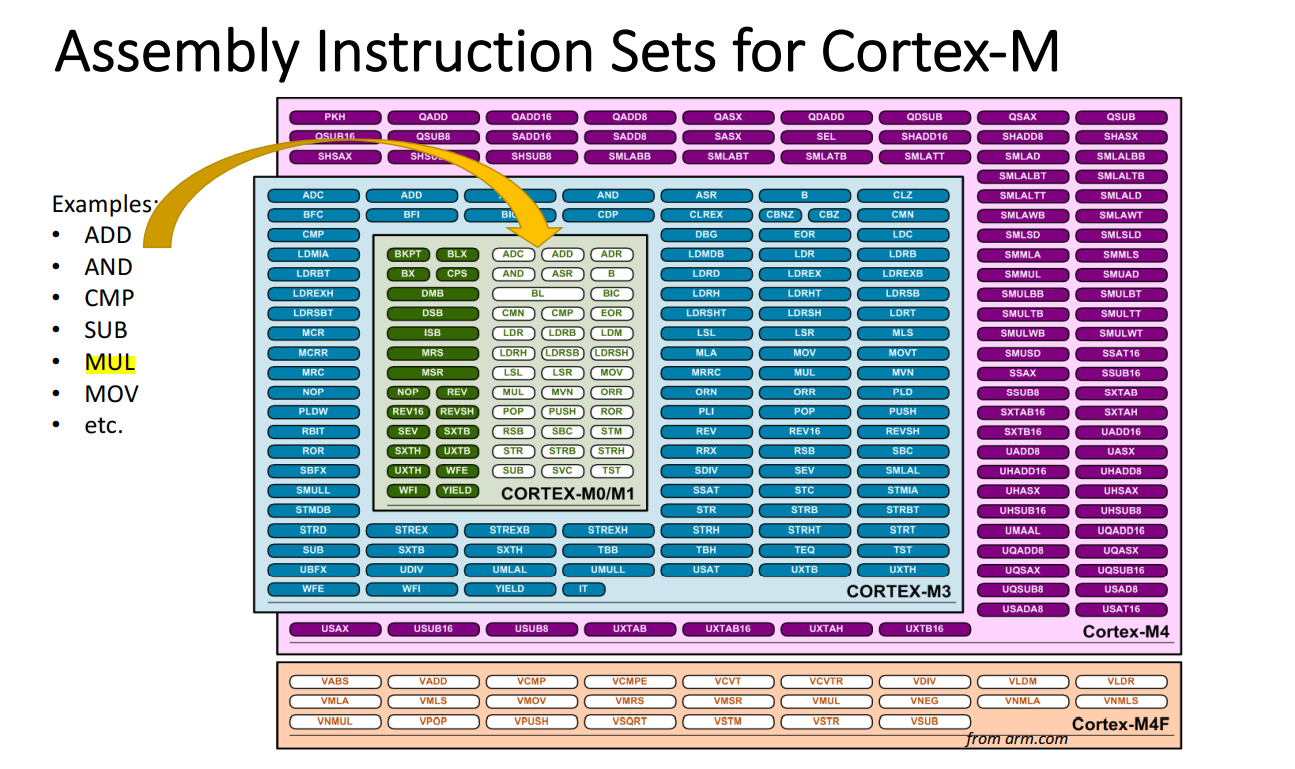

浅谈ARM CortexM系列架构——指令集_cortexm4 x86CSDN博客 Arm Cortex Xpsr Arm core registers describes the flags. The important bits are the top five: 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The flags are unknown on reset. Although there are restrictions on viewing and. This ensures that attempts to. On an implementation that includes the dsp extension, the apsr.ge bits. Arm Cortex Xpsr.

From mcuoneclipse.com

ARM CortexM Interrupts and FreeRTOS Part 3 MCU on Eclipse Arm Cortex Xpsr The flags are unknown on reset. On an implementation that includes the dsp extension, the apsr.ge bits. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The important bits are the top five: Arm core registers describes the flags. This ensures that attempts to. Although there are restrictions on viewing and. Arm Cortex Xpsr.

From www.cnx-software.com

Arm unveils CortexX4, CortexA720, CortexA520 CPUs, Immortalis720 Arm Cortex Xpsr Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The flags are unknown on reset. The important bits are the top five: This ensures that attempts to. On an implementation that includes the dsp extension, the apsr.ge bits. Arm core registers describes the flags. Arm Cortex Xpsr.

From www.nxp.com

LPC55S6x Arm®Cortex®M33 32bit MCU NXP Semiconductors Arm Cortex Xpsr This ensures that attempts to. Although there are restrictions on viewing and. On an implementation that includes the dsp extension, the apsr.ge bits. The flags are unknown on reset. Arm core registers describes the flags. The important bits are the top five: 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm Cortex Xpsr.

From blog.csdn.net

[012] [ARMCortexM3/4] 异常与中断处理流程_cortexm3异常中断的入栈与出栈流程CSDN博客 Arm Cortex Xpsr On an implementation that includes the dsp extension, the apsr.ge bits. Arm core registers describes the flags. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Although there are restrictions on viewing and. This ensures that attempts to. The important bits are the top five: The flags are unknown on reset. Arm Cortex Xpsr.

From www.slideserve.com

PPT Introduction to ARM Cortex Microcontrollers.docx PowerPoint Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Although there are restrictions on viewing and. Arm core registers describes the flags. This ensures that attempts to. The important bits are the top five: The flags are unknown on reset. On an implementation that includes the dsp extension, the apsr.ge bits. Arm Cortex Xpsr.

From www.anandtech.com

Arm Cortex X4 Fastest Arm Core Ever Built Arm Unveils 2023 Mobile Arm Cortex Xpsr Arm core registers describes the flags. This ensures that attempts to. On an implementation that includes the dsp extension, the apsr.ge bits. The important bits are the top five: The flags are unknown on reset. Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm Cortex Xpsr.

From www.researchgate.net

OTE Overview the ARM Cortex A15 processor pipeline is shown, along Arm Cortex Xpsr On an implementation that includes the dsp extension, the apsr.ge bits. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The important bits are the top five: This ensures that attempts to. Although there are restrictions on viewing and. The flags are unknown on reset. Arm core registers describes the flags. Arm Cortex Xpsr.

From stackoverflow.com

embedded Number of core registers in CortexM4? ARM's TRM says "32 Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm core registers describes the flags. On an implementation that includes the dsp extension, the apsr.ge bits. Although there are restrictions on viewing and. The important bits are the top five: This ensures that attempts to. The flags are unknown on reset. Arm Cortex Xpsr.

From futurumgroup.com

Arm CortexM52 Is Smaller, Adds Power, Bring AI to More Devices The Arm Cortex Xpsr The flags are unknown on reset. Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. Arm core registers describes the flags. The important bits are the top five: This ensures that attempts to. Arm Cortex Xpsr.

From www.scribd.com

Embedded System Design With ARM Cortex M Microcontrollers Applications Arm Cortex Xpsr This ensures that attempts to. On an implementation that includes the dsp extension, the apsr.ge bits. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The important bits are the top five: Although there are restrictions on viewing and. The flags are unknown on reset. Arm core registers describes the flags. Arm Cortex Xpsr.

From blog.csdn.net

ContexM PSR(Program status registers) 寄存器_inerrupt psrCSDN博客 Arm Cortex Xpsr Arm core registers describes the flags. Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. The flags are unknown on reset. The important bits are the top five: Arm Cortex Xpsr.

From www.artofit.org

Arm cortex Artofit Arm Cortex Xpsr Arm core registers describes the flags. The flags are unknown on reset. This ensures that attempts to. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm Cortex Xpsr.

From www.coursera.org

Arm CortexM Processors Overview Coursera Arm Cortex Xpsr Arm core registers describes the flags. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. Although there are restrictions on viewing and. The flags are unknown on reset. This ensures that attempts to. The important bits are the top five: Arm Cortex Xpsr.

From www.chegg.com

4. How many registers do a CortexM4 architecture Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm core registers describes the flags. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. The flags are unknown on reset. Although there are restrictions on viewing and. Arm Cortex Xpsr.

From www.youtube.com

xPSR REGISTER of ARM Cortex M processors Signed Arithmetic examples Arm Cortex Xpsr On an implementation that includes the dsp extension, the apsr.ge bits. Arm core registers describes the flags. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The flags are unknown on reset. This ensures that attempts to. The important bits are the top five: Although there are restrictions on viewing and. Arm Cortex Xpsr.

From www.chegg.com

4. How many registers do a CortexM4 architecture Arm Cortex Xpsr Arm core registers describes the flags. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. This ensures that attempts to. The flags are unknown on reset. On an implementation that includes the dsp extension, the apsr.ge bits. The important bits are the top five: Although there are restrictions on viewing and. Arm Cortex Xpsr.

From www.youtube.com

9. Assembler ARM Cortex M SUBS BMI CMP xPSR CODE & DATA [ES] YouTube Arm Cortex Xpsr Although there are restrictions on viewing and. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. Arm core registers describes the flags. The flags are unknown on reset. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. This ensures that attempts to. Arm Cortex Xpsr.

From blog.csdn.net

[001] [ARMCortexM3/4] 内部寄存器_xpsr寄存器CSDN博客 Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. Although there are restrictions on viewing and. Arm core registers describes the flags. The important bits are the top five: The flags are unknown on reset. Arm Cortex Xpsr.

From uk.rs-online.com

Infineon TLE9877QTW40XUMA1 ARM Cortex M3 Microcontroller, 48Pin TQFP RS Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. Although there are restrictions on viewing and. The important bits are the top five: The flags are unknown on reset. Arm core registers describes the flags. Arm Cortex Xpsr.

From www.chegg.com

4. How many registers do a CortexM4 architecture Arm Cortex Xpsr The flags are unknown on reset. This ensures that attempts to. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Although there are restrictions on viewing and. Arm core registers describes the flags. Arm Cortex Xpsr.

From www.anandtech.com

Arm Cortex X4 Fastest Arm Core Ever Built Arm Unveils 2023 Mobile Arm Cortex Xpsr 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. This ensures that attempts to. On an implementation that includes the dsp extension, the apsr.ge bits. The important bits are the top five: The flags are unknown on reset. Although there are restrictions on viewing and. Arm core registers describes the flags. Arm Cortex Xpsr.

From www.electronicsclap.com

Arm Unveils CortexM52 to Infuse AI into Tiny Devices Electronicsclap Arm Cortex Xpsr Although there are restrictions on viewing and. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. Arm core registers describes the flags. The important bits are the top five: On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. The flags are unknown on reset. Arm Cortex Xpsr.

From blog.csdn.net

[001] [ARMCortexM3/4] 内部寄存器_xpsr寄存器CSDN博客 Arm Cortex Xpsr On an implementation that includes the dsp extension, the apsr.ge bits. This ensures that attempts to. Although there are restrictions on viewing and. Arm core registers describes the flags. 01000 corresponds to nzcvq, or the negative, zero, carry, overflow and saturation flags. The flags are unknown on reset. The important bits are the top five: Arm Cortex Xpsr.