How To Divide Clock Frequency By 3 . Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. If you have any doubts in digitalelectronics , please feel to comment , i. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Frequency divided by 3 is explained by using wave form.

from www.mdpi.com

Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. If you have any doubts in digitalelectronics , please feel to comment , i. Frequency divided by 3 is explained by using wave form.

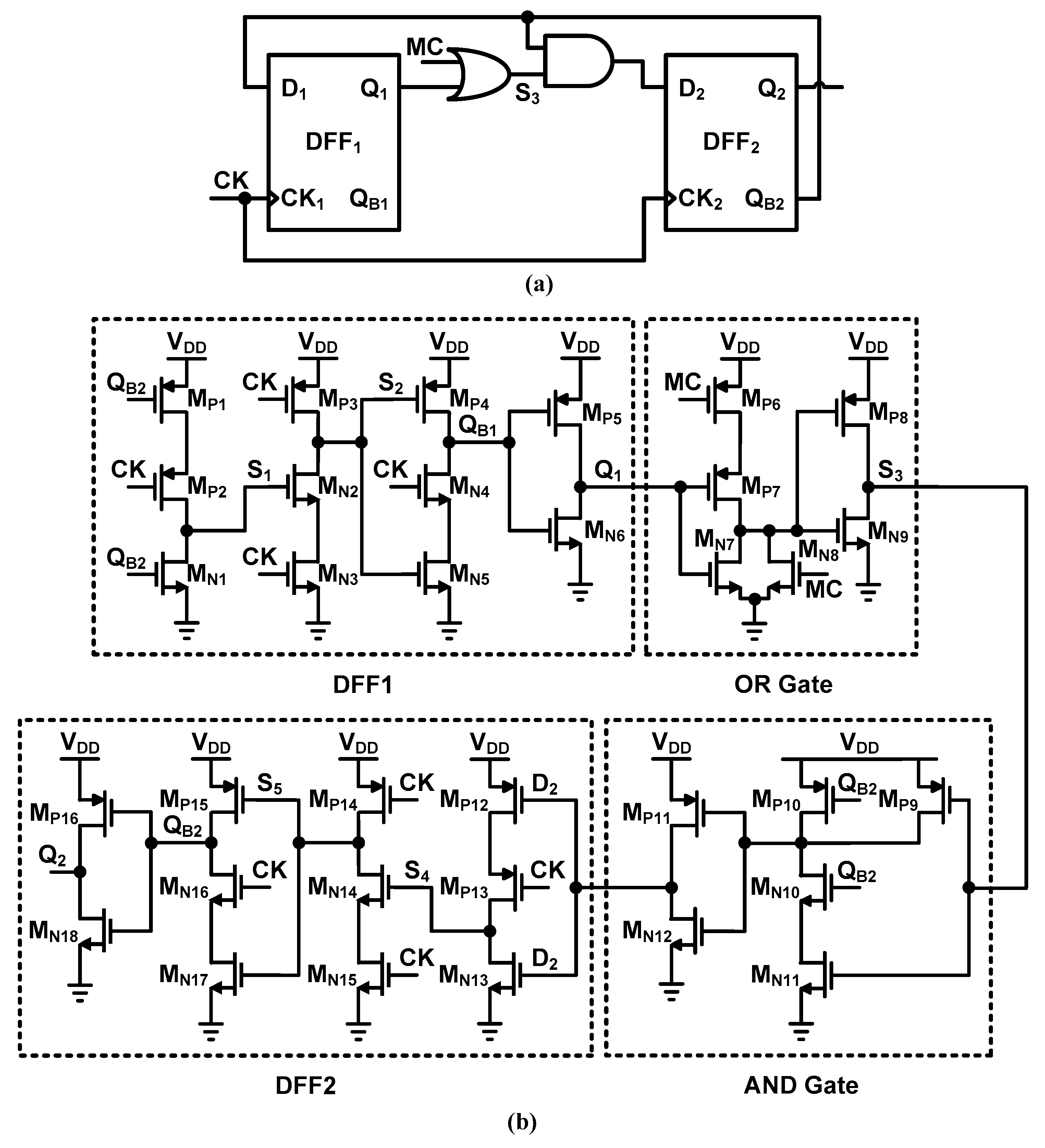

Electronics Free FullText HighSpeed WideRange TrueSinglePhase

How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3.

From www.youtube.com

Electronics clock frequency divide by 5 vhdl (2 Solutions!!) YouTube How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. If you. How To Divide Clock Frequency By 3.

From www.slideserve.com

PPT Lecture 22 PLLs and DLLs PowerPoint Presentation, free download How To Divide Clock Frequency By 3 The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Frequency divided by 3 is explained by using wave form. Using the technique, we add. How To Divide Clock Frequency By 3.

From www.circuits-diy.com

Frequency Divider Circuit How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Frequency divided by 3 is explained by using wave form. If you have any doubts in digitalelectronics , please feel to comment. How To Divide Clock Frequency By 3.

From www.chegg.com

Solved Create a divideby5 counter with a 50 duty cycle. How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Frequency divided by 3 is explained by using wave form. The standard way to get a divide by 3 with a different. How To Divide Clock Frequency By 3.

From www.solutionspile.com

[Solved] pls help with the multisim 4.2.1.1 Example 1 Freq How To Divide Clock Frequency By 3 Frequency divided by 3 is explained by using wave form. If you have any doubts in digitalelectronics , please feel to comment , i. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Using the technique, we add a gate on the clock to get differential clock and clock. How To Divide Clock Frequency By 3.

From mcalogic.blogspot.com

Frequency Divider How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to. How To Divide Clock Frequency By 3.

From www.mdpi.com

Electronics Free FullText HighSpeed WideRange TrueSinglePhase How To Divide Clock Frequency By 3 Frequency divided by 3 is explained by using wave form. If you have any doubts in digitalelectronics , please feel to comment , i. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. The standard way to get a divide by 3 with a different duty cycle is simply. How To Divide Clock Frequency By 3.

From www.youtube.com

25 Verilog Clock Divider YouTube How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Frequency. How To Divide Clock Frequency By 3.

From www.youtube.com

Clock divide by 3 YouTube How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.). How To Divide Clock Frequency By 3.

From digilent.com

Project 8 Blinking LEDs and a Clock Divider Digilent Reference How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Frequency divided by 3 is explained by using wave form. Using the technique, we add. How To Divide Clock Frequency By 3.

From www.theorycircuit.com

Frequency Divider Circuit How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.). How To Divide Clock Frequency By 3.

From www.youtube.com

Divide clock frequency by 3 with 50 duty cycle by using a Karnaugh Map How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that. How To Divide Clock Frequency By 3.

From www.vrogue.co

Frequency Divider Circuit Using 555 And 4017 Using 55 vrogue.co How To Divide Clock Frequency By 3 The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Using the technique, we add a gate on the clock to get differential clock and. How To Divide Clock Frequency By 3.

From pgandhi189.blogspot.com

VLSI verification blogs Design of frequency divider using modulo How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Frequency divided by 3 is explained by using wave form. Learn how to design frequency dividers that divide the frequency of. How To Divide Clock Frequency By 3.

From dqydj.com

Clock Manipulation Divide Frequencies with Digital Logic DQYDJ How To Divide Clock Frequency By 3 The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Using the technique, we add a gate on the clock to get differential clock and. How To Divide Clock Frequency By 3.

From itecnotes.com

Electrical Frequency and Period of a JK flipflop circuit Valuable How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. The standard. How To Divide Clock Frequency By 3.

From www.researchgate.net

Proposed divideby 2/3 stage. Download Scientific Diagram How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Frequency divided. How To Divide Clock Frequency By 3.

From www.youtube.com

Clock frequency divider circuit (divide by 2) using D flip flop YouTube How To Divide Clock Frequency By 3 The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Frequency divided by 3 is explained by using wave form. If you have any doubts in digitalelectronics , please feel to comment , i. Learn how to design frequency dividers that divide the frequency of. How To Divide Clock Frequency By 3.

From www.slideshare.net

Clock divide by 3 How To Divide Clock Frequency By 3 The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of. How To Divide Clock Frequency By 3.

From www.researchgate.net

(PDF) An Extended True Single Phase Clock Based DivideBy2/3 Frequency How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by. How To Divide Clock Frequency By 3.

From guidelibrarysilke.z19.web.core.windows.net

Clock Divider Circuit Diagram How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b”. How To Divide Clock Frequency By 3.

From github.com

frequencydivideby3/README.md at master · RahulGala/frequencydivide How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by. How To Divide Clock Frequency By 3.

From www.youtube.com

Step by Step Method to design any Clock Frequency Divider YouTube How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.). How To Divide Clock Frequency By 3.

From www.slideshare.net

Clock divide by 3 How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b”. How To Divide Clock Frequency By 3.

From www.slideshare.net

Clock divide by 3 How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Frequency divided by 3 is explained by using. How To Divide Clock Frequency By 3.

From www.electroniclinic.com

How to design digital clock using counters decoders and displays How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar. How To Divide Clock Frequency By 3.

From www.semanticscholar.org

A 10 GHz lowpower multimodulus frequency divider using Extended True How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that. How To Divide Clock Frequency By 3.

From www.chegg.com

Solved Figure Q4.1 is a circuit diagram of a clock divider How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Frequency divided by 3 is explained by using. How To Divide Clock Frequency By 3.

From www.slideshare.net

Clock divide by 3 How To Divide Clock Frequency By 3 If you have any doubts in digitalelectronics , please feel to comment , i. Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b”. How To Divide Clock Frequency By 3.

From www.circuits-diy.com

Frequency Divider Circuit How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. If you have any doubts in digitalelectronics , please feel to comment , i. Using. How To Divide Clock Frequency By 3.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Frequency divided by 3 is explained by using wave form. The standard way to get a divide by 3 with a different. How To Divide Clock Frequency By 3.

From www.slideshare.net

Clock divide by 3 How To Divide Clock Frequency By 3 Frequency divided by 3 is explained by using wave form. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. Learn how to design frequency dividers that divide the frequency of an. How To Divide Clock Frequency By 3.

From schematicsestet.z13.web.core.windows.net

Clock Divider Circuit Diagram How To Divide Clock Frequency By 3 The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop or a phase. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of. How To Divide Clock Frequency By 3.

From www.youtube.com

Clock divided by 3 Explained step by step! [Frequency divide by 3 How To Divide Clock Frequency By 3 Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar rising edge (clock neg.) to shift the output of ”b” by 90. The standard way to get a divide by 3 with a different duty cycle is simply to instantiate a delay locked loop. How To Divide Clock Frequency By 3.

From alex9ufoexploer.blogspot.com

alex9ufo 聰明人求知心切 Clock divide by 4 How To Divide Clock Frequency By 3 Learn how to design frequency dividers that divide the frequency of an input clock signal by 2, 4, or 3. If you have any doubts in digitalelectronics , please feel to comment , i. Using the technique, we add a gate on the clock to get differential clock and clock bar, a flip flop that triggers on the clock bar. How To Divide Clock Frequency By 3.