Clock In Test Bench Vhdl . Wait for 1 clock cycle (i.e. All concurrent assignments can be. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. The way that synchronization occurs with the. It is used to synchronize the inputs and outputs of the dut with the testbench. The clock signal is an important component of the test bench. Set load = 1 when you input a. The clock signal can be generated using a process or a concurrent statement. Can anyone please help me to write a testbench for it? What is a vhdl test bench (tb)? • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench.

from www.chegg.com

All concurrent assignments can be. Wait for 1 clock cycle (i.e. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. It is used to synchronize the inputs and outputs of the dut with the testbench. What is a vhdl test bench (tb)? The clock signal is an important component of the test bench. The way that synchronization occurs with the. The clock signal can be generated using a process or a concurrent statement. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main.

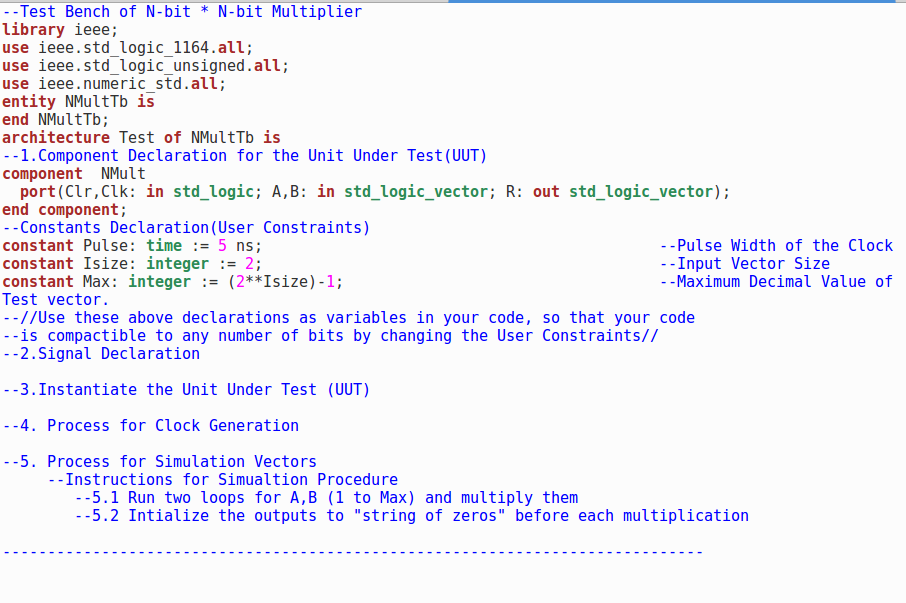

Solved Nbit Multiplier in VHDL code I need to finish the

Clock In Test Bench Vhdl The clock signal is an important component of the test bench. The way that synchronization occurs with the. Set load = 1 when you input a. The clock signal can be generated using a process or a concurrent statement. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Wait for 1 clock cycle (i.e. It is used to synchronize the inputs and outputs of the dut with the testbench. Can anyone please help me to write a testbench for it? If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. What is a vhdl test bench (tb)? • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. All concurrent assignments can be. The clock signal is an important component of the test bench.

From amberandconnorshakespeare.blogspot.com

Vhdl Test Bench Code For D Flip Flop amberandconnorshakespeare Clock In Test Bench Vhdl It is used to synchronize the inputs and outputs of the dut with the testbench. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. Set load = 1 when you input a. The clock signal is an important component of the test bench. All concurrent assignments can. Clock In Test Bench Vhdl.

From www.numerade.com

SOLVED Design a positiveedge triggered, gatelevel SR flipflop as Clock In Test Bench Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. What is a vhdl test bench (tb)? Wait for 1 clock cycle (i.e. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. The way that synchronization occurs with the.. Clock In Test Bench Vhdl.

From www.coursehero.com

[Solved] 4 bit ripple adder/subtractor VHDL code Testbench entity Clock In Test Bench Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Can anyone please help me to write a testbench for it? • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. Set load = 1 when you input a.. Clock In Test Bench Vhdl.

From www.hotzxgirl.com

How To Implement A Verilog Testbench Clock Generator For Sequential Clock In Test Bench Vhdl What is a vhdl test bench (tb)? In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. The way that synchronization occurs with the. All concurrent assignments can be. Set load = 1 when you input a. The clock signal can be generated using a process or a concurrent statement. If. Clock In Test Bench Vhdl.

From jp.mathworks.com

Verilog / VHDL / FPGA / ASICテストベンチ MATLAB & Simulink Clock In Test Bench Vhdl • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. It is used to synchronize the inputs and outputs of the dut with the testbench. The clock signal is an important component of the test bench. The way that synchronization occurs with the. In almost any testbench, a. Clock In Test Bench Vhdl.

From www.numerade.com

SOLVED Use the T flip flop design to write structural VHDL code for Clock In Test Bench Vhdl Set load = 1 when you input a. The clock signal is an important component of the test bench. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main.. Clock In Test Bench Vhdl.

From aaa-ai2.blogspot.com

Test Bench In Vhdl Pdf aaaai2 Clock In Test Bench Vhdl Can anyone please help me to write a testbench for it? The clock signal can be generated using a process or a concurrent statement. The clock signal is an important component of the test bench. Wait for 1 clock cycle (i.e. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench.. Clock In Test Bench Vhdl.

From allmodernbenches.blogspot.com

Modern Storage Benches and Dining Benches Vhdl Test Bench Clock Clock In Test Bench Vhdl • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. What is a vhdl test bench (tb)? All concurrent assignments can be. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Wait for 1 clock cycle (i.e. Can. Clock In Test Bench Vhdl.

From www.chegg.com

Describe the clock divider circuit in VHDL using the Clock In Test Bench Vhdl What is a vhdl test bench (tb)? Set load = 1 when you input a. All concurrent assignments can be. Wait for 1 clock cycle (i.e. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Can anyone please help me to write a testbench for it? The clock signal is. Clock In Test Bench Vhdl.

From www.youtube.com

VHDL Lecture 24 Lab 8 Clock Divider and Counters Explanation YouTube Clock In Test Bench Vhdl • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within. Clock In Test Bench Vhdl.

From www.numerade.com

SOLVED Write a VHDL code to implement the circuit function described Clock In Test Bench Vhdl Wait for 1 clock cycle (i.e. The clock signal can be generated using a process or a concurrent statement. All concurrent assignments can be. What is a vhdl test bench (tb)? It is used to synchronize the inputs and outputs of the dut with the testbench. Set load = 1 when you input a. • vhdl test bench (tb) is. Clock In Test Bench Vhdl.

From amberandconnorshakespeare.blogspot.com

Vhdl Test Bench Code For Half Adder amberandconnorshakespeare Clock In Test Bench Vhdl If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Set load = 1 when you input a. Wait for 1 clock cycle (i.e. All concurrent assignments can be. The way that synchronization occurs with the. In almost any testbench, a clock signal is usually required in order to. Clock In Test Bench Vhdl.

From www.vrogue.co

Switch Level Modeling In Verilog Hdl Using Modelsim I vrogue.co Clock In Test Bench Vhdl The clock signal can be generated using a process or a concurrent statement. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Can anyone please help me to write a testbench for it? Wait for 1 clock cycle (i.e. The way that synchronization occurs with the. In almost. Clock In Test Bench Vhdl.

From surf-vhdl.com

How to Implement a Full Adder in VHDL SurfVHDL Clock In Test Bench Vhdl If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. What is a vhdl test bench (tb)? The way that synchronization occurs with the. All concurrent assignments can be. •. Clock In Test Bench Vhdl.

From www.youtube.com

VHDL BASIC Tutorial TESTBENCH YouTube Clock In Test Bench Vhdl It is used to synchronize the inputs and outputs of the dut with the testbench. Set load = 1 when you input a. The way that synchronization occurs with the. The clock signal is an important component of the test bench. What is a vhdl test bench (tb)? All concurrent assignments can be. If the clk_gen procedure is placed in. Clock In Test Bench Vhdl.

From www.embeddedrelated.com

VHDL tutorial part 2 Testbench Gene Breniman Clock In Test Bench Vhdl It is used to synchronize the inputs and outputs of the dut with the testbench. What is a vhdl test bench (tb)? If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Can anyone please help me to write a testbench for it? The clock signal can be generated. Clock In Test Bench Vhdl.

From www.chegg.com

Solved issue with VHDL bench code. not using a clock (not Clock In Test Bench Vhdl What is a vhdl test bench (tb)? In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. It is used to synchronize the inputs and outputs of the dut with the testbench. All concurrent assignments can be. Set load = 1 when you input a. The way that synchronization occurs with. Clock In Test Bench Vhdl.

From biochiptronics.blogspot.com

EXP12 SIMULATION OF VHDL TEST BENCH CODE FOR TESTING A GATE Clock In Test Bench Vhdl Can anyone please help me to write a testbench for it? If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Set load = 1 when you input a. Wait for 1 clock cycle (i.e. The way that synchronization occurs with the. In almost any testbench, a clock signal. Clock In Test Bench Vhdl.

From www.slideserve.com

PPT VHDL PowerPoint Presentation, free download ID226593 Clock In Test Bench Vhdl Wait for 1 clock cycle (i.e. It is used to synchronize the inputs and outputs of the dut with the testbench. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. What is a vhdl test bench (tb)? If the clk_gen procedure is placed in a separate package, then reuse from. Clock In Test Bench Vhdl.

From www.youtube.com

Create a simple VHDL test bench using Xilinx ISE. YouTube Clock In Test Bench Vhdl Can anyone please help me to write a testbench for it? In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. It is used to synchronize the inputs and outputs of the dut with the testbench. Wait for 1 clock cycle (i.e. What is a vhdl test bench (tb)? If the. Clock In Test Bench Vhdl.

From www.embeddedrelated.com

VHDL tutorial A practical example part 3 VHDL testbench Gene Clock In Test Bench Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. The clock signal can be generated using a process or a concurrent statement. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. It is used to synchronize the. Clock In Test Bench Vhdl.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Clock In Test Bench Vhdl What is a vhdl test bench (tb)? All concurrent assignments can be. The clock signal can be generated using a process or a concurrent statement. It is used to synchronize the inputs and outputs of the dut with the testbench. Set load = 1 when you input a. • vhdl test bench (tb) is a piece of code meant to. Clock In Test Bench Vhdl.

From itecnotes.com

VHDL simulation does not work Valuable Tech Notes Clock In Test Bench Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Can anyone please help me to write a testbench for it? The clock signal is an important component of the. Clock In Test Bench Vhdl.

From www.youtube.com

VHDL Combinational and Sequential Design using Process blocks and Test Clock In Test Bench Vhdl What is a vhdl test bench (tb)? All concurrent assignments can be. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Set load = 1 when you input a. The clock signal can be generated using a process or a concurrent statement. It is used to synchronize the inputs and. Clock In Test Bench Vhdl.

From circuitdigest.com

Implementation of Basic Logic Gates using VHDL in ModelSim Clock In Test Bench Vhdl Set load = 1 when you input a. All concurrent assignments can be. Wait for 1 clock cycle (i.e. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. It is used to synchronize the inputs and outputs of the dut with the testbench. The clock signal is an important component. Clock In Test Bench Vhdl.

From www.embeddedrelated.com

VHDL tutorial part 2 Testbench Gene Breniman Clock In Test Bench Vhdl The clock signal is an important component of the test bench. It is used to synchronize the inputs and outputs of the dut with the testbench. The way that synchronization occurs with the. What is a vhdl test bench (tb)? All concurrent assignments can be. The clock signal can be generated using a process or a concurrent statement. Can anyone. Clock In Test Bench Vhdl.

From vhdltb.blogspot.com

VHDL Test Bench for FPGA/ASIC Verification VHDL Test Bench Usage Tips Clock In Test Bench Vhdl If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. What is a vhdl test bench (tb)? It is used to synchronize the inputs and outputs of the dut with the testbench. The clock signal is an important component of the test bench. Wait for 1 clock cycle (i.e.. Clock In Test Bench Vhdl.

From vhdlsimplified.blogspot.com

VHDL Codes VHDL Code For 4bit Serial In Parallel Out (SIPO) Shift Clock In Test Bench Vhdl Set load = 1 when you input a. Wait for 1 clock cycle (i.e. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. What is a vhdl test bench (tb)? The clock signal can be generated using a process or a concurrent statement. In almost any testbench, a. Clock In Test Bench Vhdl.

From fixlibrarygedwaaldebx.z21.web.core.windows.net

Clock Divider Circuit Diagram Clock In Test Bench Vhdl All concurrent assignments can be. Wait for 1 clock cycle (i.e. The way that synchronization occurs with the. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Can anyone please help me to write a testbench for it? In almost any testbench, a clock signal is usually required. Clock In Test Bench Vhdl.

From kner.at

VHDL Tutorial Clock In Test Bench Vhdl The clock signal can be generated using a process or a concurrent statement. Can anyone please help me to write a testbench for it? Set load = 1 when you input a. All concurrent assignments can be. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. If. Clock In Test Bench Vhdl.

From verificationacademy.com

An Evaluation of the Advantages of Moving from a VHDL to a UVM Clock In Test Bench Vhdl The way that synchronization occurs with the. It is used to synchronize the inputs and outputs of the dut with the testbench. Set load = 1 when you input a. All concurrent assignments can be. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the main. The clock signal. Clock In Test Bench Vhdl.

From embdev.net

vhdl input clock to output Clock In Test Bench Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Can anyone please help me to write a testbench for it? What is a vhdl test bench (tb)? The clock signal can be generated using a process or a concurrent statement. Set load = 1 when you input a. If the. Clock In Test Bench Vhdl.

From www.numerade.com

SOLVED Use Xilinx Vivado 2019.1 to design a circuit including a 1 Clock In Test Bench Vhdl What is a vhdl test bench (tb)? Set load = 1 when you input a. Can anyone please help me to write a testbench for it? In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. If the clk_gen procedure is placed in a separate package, then reuse from test bench. Clock In Test Bench Vhdl.

From www.chegg.com

Solved Nbit Multiplier in VHDL code I need to finish the Clock In Test Bench Vhdl The way that synchronization occurs with the. If the clk_gen procedure is placed in a separate package, then reuse from test bench to test bench becomes straight forward. Can anyone please help me to write a testbench for it? • vhdl test bench (tb) is a piece of code meant to verify the functional correctness of hdl model • the. Clock In Test Bench Vhdl.

From allmodernbenches.blogspot.com

Modern Storage Benches and Dining Benches Vhdl Test Bench Clock Clock In Test Bench Vhdl The way that synchronization occurs with the. What is a vhdl test bench (tb)? The clock signal can be generated using a process or a concurrent statement. Wait for 1 clock cycle (i.e. The clock signal is an important component of the test bench. • vhdl test bench (tb) is a piece of code meant to verify the functional correctness. Clock In Test Bench Vhdl.