Verilog Latch Example . In this tutorial, we will use. Here is the verilog result: A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Always @ (enable, data) begin if (enable) begin q. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Module latch (input enable, input data, output reg q); Note that when the convert. Here’s an example of a simple latch in verilog:

from mungfali.com

In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Always @ (enable, data) begin if (enable) begin q. Note that when the convert. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this tutorial, we will use. Here is the verilog result: Module latch (input enable, input data, output reg q); Here’s an example of a simple latch in verilog:

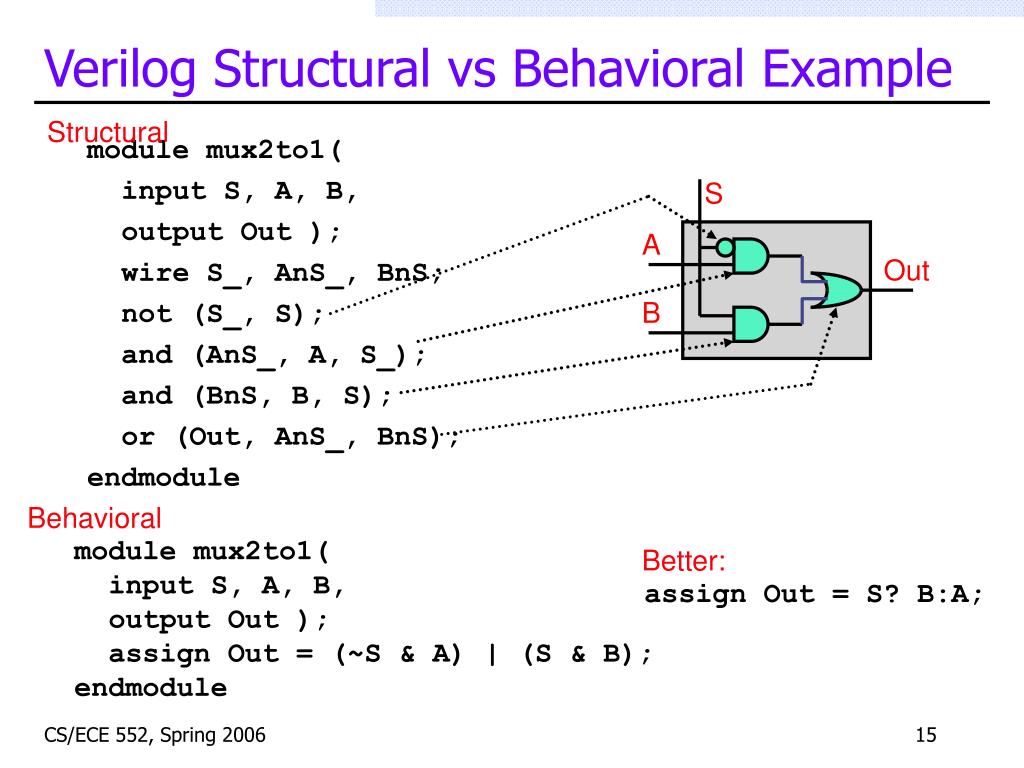

Verilog Structural Model

Verilog Latch Example Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Note that when the convert. Always @ (enable, data) begin if (enable) begin q. Here is the verilog result: In this tutorial, we will use. Module latch (input enable, input data, output reg q); A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Here’s an example of a simple latch in verilog: Latches are sequential logic circuits that store data and can change their output based on the current input or previous state.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download Verilog Latch Example In this tutorial, we will use. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Here’s an example of a simple latch in verilog: Note that when. Verilog Latch Example.

From www.youtube.com

SR LATCH VERILOG PROGRAM IN DATA FLOW YouTube Verilog Latch Example Note that when the convert. Here’s an example of a simple latch in verilog: A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Here is the verilog. Verilog Latch Example.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download Verilog Latch Example Always @ (enable, data) begin if (enable) begin q. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Here is the verilog result: Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Module latch (input enable,. Verilog Latch Example.

From www.youtube.com

SR NOR Latch Verilog Code including Test Bench EC Junction Verilog Latch Example Here is the verilog result: Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Module. Verilog Latch Example.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Verilog Latch Example Here is the verilog result: Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this tutorial, we will use. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this article we will look at. Verilog Latch Example.

From www.w3cschool.cn

Verilog 避免Latch_w3cschool Verilog Latch Example Here is the verilog result: In this tutorial, we will use. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Latches are sequential logic circuits that store data and can change their output based on the. Verilog Latch Example.

From www.youtube.com

Verilog Tutorial 20 Latch YouTube Verilog Latch Example Always @ (enable, data) begin if (enable) begin q. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Here’s an example of a simple latch in verilog: In this tutorial, we will use. Here is the. Verilog Latch Example.

From studylib.net

Verilog Example Verilog Latch Example Here is the verilog result: Module latch (input enable, input data, output reg q); Here’s an example of a simple latch in verilog: In this tutorial, we will use. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this article we will look at how transparent latches. Verilog Latch Example.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5198890 Verilog Latch Example A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this tutorial, we will use. Always @ (enable, data) begin if (enable) begin q. Here’s an example of a simple latch in verilog: Note that when the convert. Latches are sequential logic circuits that store data and can. Verilog Latch Example.

From slidetodoc.com

Hardware Description Languages Verilog z Verilog y Structural Verilog Latch Example Always @ (enable, data) begin if (enable) begin q. Note that when the convert. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Here’s an example of a simple latch in verilog: Module latch (input enable, input data, output reg q); In this tutorial, we will use. In. Verilog Latch Example.

From alex9ufoexploer.blogspot.com

alex9ufo 聰明人求知心切 4bit latch in Verilog Verilog Latch Example Here is the verilog result: Module latch (input enable, input data, output reg q); A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Verilog Latch Example.

From www.slideserve.com

PPT ECE 4680 Computer Architecture Verilog Presentation I. PowerPoint Verilog Latch Example Here is the verilog result: In this tutorial, we will use. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Always @ (enable, data) begin if (enable) begin q. In this article we will look at how transparent latches are synthesized from if statements and how to avoid. Verilog Latch Example.

From courses.cs.washington.edu

Structural Verilog Verilog Latch Example Module latch (input enable, input data, output reg q); Note that when the convert. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Verilog Latch Example.

From www.eeweb.com

Controlling Latches Before They Ruin Your Day EE Verilog Latch Example Module latch (input enable, input data, output reg q); A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Note that when the convert. Here’s an example of a simple latch in verilog: Here is the verilog result: In this tutorial, we will use. Always @ (enable, data) begin. Verilog Latch Example.

From www.youtube.com

Verilog code for D Flip Flop with Testbench YouTube Verilog Latch Example Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Note that when the convert. Here is the verilog result: Module latch (input enable, input data, output reg q); Always @ (enable, data) begin if (enable) begin q. Here’s an example of a simple latch in verilog: In this. Verilog Latch Example.

From www.chegg.com

Solved 1.Fill in the blanks for the Verilog HDL behavioral Verilog Latch Example Note that when the convert. Here’s an example of a simple latch in verilog: In this tutorial, we will use. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Always @ (enable, data) begin if (enable) begin q. In this article we will look at how transparent latches. Verilog Latch Example.

From slideplayer.com

Supplement on Verilog FF circuit examples ppt download Verilog Latch Example In this tutorial, we will use. Always @ (enable, data) begin if (enable) begin q. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Here’s an example of a simple latch in verilog: Here is the verilog result: In this article we will look at how transparent latches. Verilog Latch Example.

From www.chegg.com

Solved use the verilog code above and convert to a D latch Verilog Latch Example Here is the verilog result: Note that when the convert. In this tutorial, we will use. Module latch (input enable, input data, output reg q); A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this article we will look at how transparent latches are synthesized from if. Verilog Latch Example.

From www.youtube.com

Verilog Code of D latch YouTube Verilog Latch Example Always @ (enable, data) begin if (enable) begin q. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Here’s an example of a simple latch in verilog: A latch is inferred when the output of combinatorial. Verilog Latch Example.

From everythingbanana.hatenablog.com

Jk Latch In Verilog Code everythingbanana’s blog Verilog Latch Example Here is the verilog result: In this tutorial, we will use. Always @ (enable, data) begin if (enable) begin q. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Here’s an example of a simple latch in verilog: Module latch (input enable, input data, output reg q); Note. Verilog Latch Example.

From digilent.com

Verilog® HDL Project 1 Digilent Reference Verilog Latch Example Here is the verilog result: In this tutorial, we will use. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Note that when the convert. Module latch (input enable, input data, output reg q); Always @ (enable, data) begin if (enable) begin q. In this article we will. Verilog Latch Example.

From www.slideserve.com

PPT Verilog II CPSC 321 PowerPoint Presentation, free download ID Verilog Latch Example Here is the verilog result: In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Note. Verilog Latch Example.

From www.youtube.com

An Example Verilog Test Bench YouTube Verilog Latch Example Here is the verilog result: Always @ (enable, data) begin if (enable) begin q. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Verilog Latch Example.

From www.researchgate.net

(a) Verilog module which implements a NAND3 based Verilog Latch Example Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this tutorial, we will use. Always @ (enable, data) begin if (enable) begin q. Module latch (input enable, input data, output reg q); A latch is inferred when the output of combinatorial logic has undefined states, that is. Verilog Latch Example.

From mungfali.com

Verilog Structural Model Verilog Latch Example A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Here’s an example of a simple latch in verilog: Note that when the convert. Always @ (enable, data). Verilog Latch Example.

From www.scribd.com

Verilog For Sequential Circuits Example of D LATCH PDF Verilog Latch Example Here’s an example of a simple latch in verilog: In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Always @ (enable, data) begin if (enable) begin q. A latch is inferred when the output of combinatorial. Verilog Latch Example.

From www.slideserve.com

PPT Verilog Modules for Common Digital Functions PowerPoint Verilog Latch Example Here’s an example of a simple latch in verilog: Module latch (input enable, input data, output reg q); Always @ (enable, data) begin if (enable) begin q. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Here is the verilog result: Note that when the convert. Latches are. Verilog Latch Example.

From www.youtube.com

Verilog (Part 1) Example Dataflow and Structural Description YouTube Verilog Latch Example Here is the verilog result: In this tutorial, we will use. Here’s an example of a simple latch in verilog: Module latch (input enable, input data, output reg q); Always @ (enable, data) begin if (enable) begin q. Note that when the convert. Latches are sequential logic circuits that store data and can change their output based on the current. Verilog Latch Example.

From www.youtube.com

System Verilog Interview Question Write the code for DFlip Flop in Verilog Latch Example Note that when the convert. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this tutorial, we will use. Here is the verilog result: Module latch (input enable, input data, output reg q); A latch is inferred when the output of combinatorial logic has undefined states, that. Verilog Latch Example.

From regiszhao.github.io

Digital Circuits and Verilog Review Verilog Latch Example Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Here is the verilog result: A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. In this tutorial, we will use. Always @ (enable, data) begin if (enable). Verilog Latch Example.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5198890 Verilog Latch Example In this tutorial, we will use. A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Here is the verilog result: Here’s an example of a simple latch in verilog: Latches are sequential logic circuits that store data and can change their output based on the current input or. Verilog Latch Example.

From www.slideserve.com

PPT Digital System Design PowerPoint Presentation, free download ID Verilog Latch Example In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Here is the verilog result: In. Verilog Latch Example.

From www.slideserve.com

PPT Latchbased Design PowerPoint Presentation, free download ID Verilog Latch Example Note that when the convert. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. Module. Verilog Latch Example.

From www.chegg.com

Solved Sequential Logic; Active High/Low SR latch Design Verilog Latch Example Here is the verilog result: In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational logic circuits from. In this tutorial, we will use. Here’s an example of a simple latch in verilog: Note that when the convert. Latches are. Verilog Latch Example.

From www.numerade.com

SOLVED The SR latch can be built using NAND gates or NOR gates. This Verilog Latch Example A latch is inferred when the output of combinatorial logic has undefined states, that is it must hold its previous value. Note that when the convert. Always @ (enable, data) begin if (enable) begin q. Module latch (input enable, input data, output reg q); Here’s an example of a simple latch in verilog: In this tutorial, we will use. In. Verilog Latch Example.