Clock Gating Path . Can you figure out why? in between the start point and the end point there may be lots of buffers/inverters/clock divider. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. A path from a clock input port or cell pin, through one or more buffers or. Use internal (or external) signal to. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. sta also considers the following types of paths for timing analysis: this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Because a high on ‘en’ signal allows the.

from slidetodoc.com

Can you figure out why? Because a high on ‘en’ signal allows the. A path from a clock input port or cell pin, through one or more buffers or. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. sta also considers the following types of paths for timing analysis: Use internal (or external) signal to. in between the start point and the end point there may be lots of buffers/inverters/clock divider. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power.

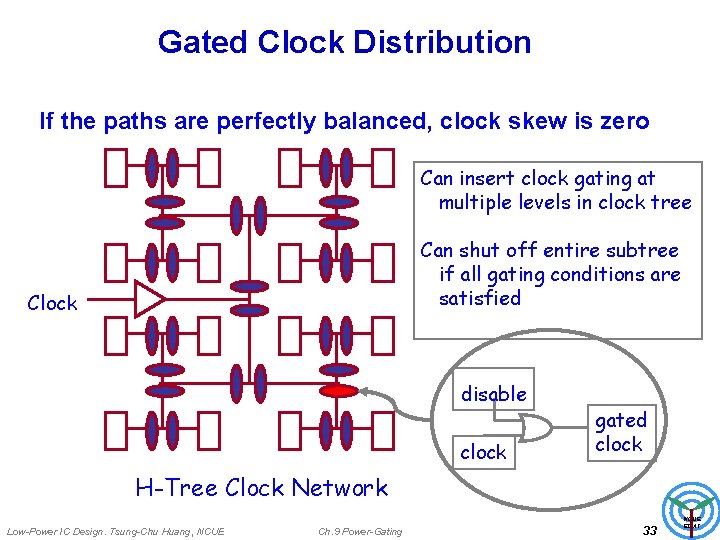

LowPower IC Design Gating Techniques TsungChu Huang Dept

Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. sta also considers the following types of paths for timing analysis: Use internal (or external) signal to. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. in between the start point and the end point there may be lots of buffers/inverters/clock divider. Because a high on ‘en’ signal allows the. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. A path from a clock input port or cell pin, through one or more buffers or. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Can you figure out why?

From www.vrogue.co

What Are Setup And Hold Timing Checks What Is Setup A vrogue.co Clock Gating Path A path from a clock input port or cell pin, through one or more buffers or. sta also considers the following types of paths for timing analysis: in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. clock gating is a technique employed in the design of digital circuits,. Clock Gating Path.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. Because a high on ‘en’ signal allows the. A path from a clock input port or cell pin, through one or more buffers or. sta also considers the following types of paths for timing analysis: . Clock Gating Path.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Path in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. sta also considers the following types of paths for timing analysis: in between the start point and the end point there may be lots of buffers/inverters/clock divider. this technique of using an ‘and’ gate is referred to as. Clock Gating Path.

From www.scirp.org

A New Clock Gated Flip Flop for Pipelining Architecture Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. A path from a clock input port. Clock Gating Path.

From slideplayer.com

Page 1 Department of Electrical Engineering National Chung Cheng Clock Gating Path sta also considers the following types of paths for timing analysis: in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Can you figure out why? A path from. Clock Gating Path.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Path A path from a clock input port or cell pin, through one or more buffers or. Because a high on ‘en’ signal allows the. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. Use internal (or external) signal to. this technique of using an ‘and’ gate is referred to. Clock Gating Path.

From www.youtube.com

Integrated Clock Gating Cell ICG Cell in VLSI Clock Gating Cell Clock Gating Path A path from a clock input port or cell pin, through one or more buffers or. Can you figure out why? clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Use internal (or external) signal to. sta also considers the following types of paths for timing analysis: this. Clock Gating Path.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Use internal (or external) signal to. Can you figure out why? in computer architecture, clock gating is a popular power management technique used. Clock Gating Path.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Clock Gating Path Use internal (or external) signal to. in between the start point and the end point there may be lots of buffers/inverters/clock divider. A path from a clock input port or cell pin, through one or more buffers or. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Because a. Clock Gating Path.

From coqube.com

Clock Gating for Power Reduction CoQube Analytics and Services Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. Use internal (or external) signal to. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce. Clock Gating Path.

From www.slideserve.com

PPT Timing Analysis PowerPoint Presentation, free download ID482036 Clock Gating Path clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. A path from a clock input port or cell pin, through one or more buffers or. Because a high on ‘en’ signal allows the. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits. Clock Gating Path.

From www.edn.com

Clock gating Smart use ensures smart returns EDN Clock Gating Path this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. in between the start point and the end point there may be lots of buffers/inverters/clock divider. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. Can you figure out why? Use internal. Clock Gating Path.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation Clock Gating Path in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. A path from a clock input port or cell pin, through one or more buffers or. clock gating is a technique employed in. Clock Gating Path.

From www.slideshare.net

Low Power Techniques Clock Gating Path Use internal (or external) signal to. in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. in between the start point and the end point there may be lots of buffers/inverters/clock divider. Can. Clock Gating Path.

From www.youtube.com

sta lec30 clock gating checks part1 Static Timing Analysis tutorial Clock Gating Path Can you figure out why? clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. in between the start point and the end point there may be lots of buffers/inverters/clock divider. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. in. Clock Gating Path.

From www.cnblogs.com

Clock Gating Checks 小勇5 博客园 Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. Because a high on ‘en’ signal allows the. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. A path from a clock input port or cell pin, through one or more buffers or. sta. Clock Gating Path.

From www.researchgate.net

(PDF) Power Optimization Using Clock Gating and Power Gating A Review Clock Gating Path clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. . Clock Gating Path.

From www.elecfans.com

低功耗设计基础:Clock Gating电子发烧友网 Clock Gating Path this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Use internal (or external) signal to. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. in between the start point and the end point there may be lots of buffers/inverters/clock divider. . Clock Gating Path.

From fyogyhdyn.blob.core.windows.net

What Is Clock Gating Efficiency at Mark Goff blog Clock Gating Path in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. A path from a clock input port or cell pin, through one or more buffers or. Can you figure out why? clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. . Clock Gating Path.

From slidetodoc.com

LowPower IC Design Gating Techniques TsungChu Huang Dept Clock Gating Path A path from a clock input port or cell pin, through one or more buffers or. Use internal (or external) signal to. Because a high on ‘en’ signal allows the. sta also considers the following types of paths for timing analysis: in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for. Clock Gating Path.

From blog.csdn.net

Timing Modeling and Analysis_timging pathCSDN博客 Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. Can you figure out why? clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. this technique of using an ‘and’ gate is referred to as ‘active. Clock Gating Path.

From vlsiuniverse.blogspot.com

Clock gating interview questions VLSI n EDA Clock Gating Path Because a high on ‘en’ signal allows the. in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. A path from a clock input port or cell pin, through one or more buffers or. clock gating is a technique employed in the design of digital circuits,. Clock Gating Path.

From slideplayer.com

Laboratory for Computer Science Massachusetts Institute of Technology Clock Gating Path this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Use internal (or external) signal to. Can you figure out why? Because a high on ‘en’ signal allows the. in between the start point and the end point there may be lots of buffers/inverters/clock divider. in computer architecture, clock gating is. Clock Gating Path.

From www.semanticscholar.org

Figure 5 from Complex clock gating with integrated clock gating logic Clock Gating Path clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Can you figure out why? in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal. Clock Gating Path.

From shumin.co.kr

[Digital Logic] Static Timing Analysis (STA) Shumin Blog Clock Gating Path Can you figure out why? this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. sta also considers the following types of paths for timing analysis: clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Use internal (or external) signal to. . Clock Gating Path.

From blogs.cuit.columbia.edu

Check clock gating Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. Because a high on ‘en’ signal allows the. A path from a clock input port or cell pin, through one or more buffers or. Can you figure out why? in computer architecture, clock gating is a. Clock Gating Path.

From www.researchgate.net

8Bit dual port sram with clock gating technique onchip power Clock Gating Path A path from a clock input port or cell pin, through one or more buffers or. sta also considers the following types of paths for timing analysis: Because a high on ‘en’ signal allows the. Can you figure out why? Use internal (or external) signal to. in computer architecture, clock gating is a popular power management technique used. Clock Gating Path.

From www.scirp.org

A New Clock Gated Flip Flop for Pipelining Architecture Clock Gating Path clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Because a high on ‘en’ signal allows the. Can you figure out why? Use internal (or external) signal to. A path from a clock input port or cell pin, through one or more buffers or. this technique of using an. Clock Gating Path.

From www.edn.com

Clock gating Smart use ensures smart returns EDN Clock Gating Path sta also considers the following types of paths for timing analysis: in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. A path from a clock input port or cell pin, through one or more buffers or. this technique of using an ‘and’ gate is referred to as ‘active. Clock Gating Path.

From shumin.co.kr

[Digital Logic] Static Timing Analysis (STA) Shumin Blog Clock Gating Path sta also considers the following types of paths for timing analysis: in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. this technique of using an. Clock Gating Path.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. sta also considers the following types of paths for timing analysis: A path from a clock input port or cell pin, through one or more buffers or. clock gating is a technique employed in the design of digital circuits, particularly in. Clock Gating Path.

From www.xilinx.com

AR 51737 Does XST support gated clock conversion? Clock Gating Path in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. Use internal (or external) signal to. sta also considers the following types of paths for timing analysis: Can you figure out why? this technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. A. Clock Gating Path.

From zhuanlan.zhihu.com

【STA专题一】Setup check 与 Hold check 知乎 Clock Gating Path sta also considers the following types of paths for timing analysis: A path from a clock input port or cell pin, through one or more buffers or. Because a high on ‘en’ signal allows the. clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. in computer architecture, clock. Clock Gating Path.

From www.researchgate.net

Flowchart of clock gating. The proposed clock gating circuit is shown Clock Gating Path in between the start point and the end point there may be lots of buffers/inverters/clock divider. Use internal (or external) signal to. A path from a clock input port or cell pin, through one or more buffers or. Because a high on ‘en’ signal allows the. in computer architecture, clock gating is a popular power management technique used. Clock Gating Path.

From www.youtube.com

PD Lec 56 Clock Gating Checks CGC Paths CTS VLSI Physical Clock Gating Path clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. sta also considers the following types of paths for timing analysis: in computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing. in between the start point and the end point. Clock Gating Path.