What Is A Clock Vhdl . In vhdl, you generate clock signals for hardware implementations or simulation purposes. For simulation, you create clocks using simple. How to use a clock and do assertions. In many test benches i see the following pattern for clock generation: Clock is the backbone of any synchronous design. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Defining a clock signal in vhdl. We use the after statement to generate the. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. Process begin clk <= '0';

from www.slideserve.com

In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. We use the after statement to generate the. For simulation, you create clocks using simple. Process begin clk <= '0'; How to use a clock and do assertions. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. In many test benches i see the following pattern for clock generation: Defining a clock signal in vhdl. Clock is the backbone of any synchronous design. In vhdl, you generate clock signals for hardware implementations or simulation purposes.

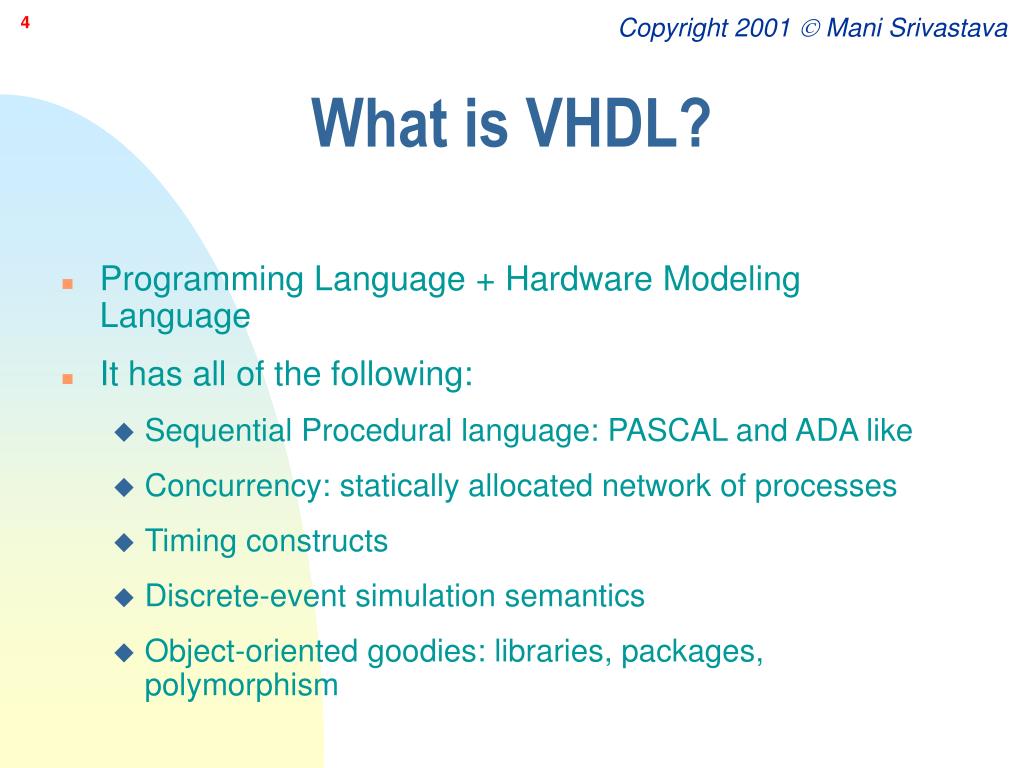

PPT VHDL Overview PowerPoint Presentation, free download ID6991479

What Is A Clock Vhdl Clock is the backbone of any synchronous design. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. We use the after statement to generate the. Clock is the backbone of any synchronous design. How to use a clock and do assertions. Process begin clk <= '0'; For simulation, you create clocks using simple. In vhdl, you generate clock signals for hardware implementations or simulation purposes. Defining a clock signal in vhdl. In many test benches i see the following pattern for clock generation:

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL What Is A Clock Vhdl The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Process begin clk <= '0'; For simulation, you create clocks using simple. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. We use the after statement to generate the. In vhdl, you. What Is A Clock Vhdl.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID3740926 What Is A Clock Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. For simulation, you create clocks using simple. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. How to use a clock and do assertions. The next thing we do when writing a vhdl. What Is A Clock Vhdl.

From www.chegg.com

Wright a VHDL code Design a dual clock synchronous What Is A Clock Vhdl Process begin clk <= '0'; For simulation, you create clocks using simple. Defining a clock signal in vhdl. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. In many test benches i see the following pattern for clock generation: How to use a clock and do assertions. In vhdl, you generate clock. What Is A Clock Vhdl.

From mathpag.weebly.com

Clock divider vhdl mathpag What Is A Clock Vhdl Defining a clock signal in vhdl. In vhdl, you generate clock signals for hardware implementations or simulation purposes. For simulation, you create clocks using simple. Process begin clk <= '0'; Clock is the backbone of any synchronous design. We use the after statement to generate the. How to use a clock and do assertions. This example shows how to generate. What Is A Clock Vhdl.

From itecnotes.com

Electronic VHDL Concurrent statement comparison Valuable Tech Notes What Is A Clock Vhdl Process begin clk <= '0'; For simulation, you create clocks using simple. Clock is the backbone of any synchronous design. Defining a clock signal in vhdl. How to use a clock and do assertions. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In many test benches i see the following. What Is A Clock Vhdl.

From www.youtube.com

How to create a Clocked Process in VHDL YouTube What Is A Clock Vhdl Process begin clk <= '0'; This example shows how to generate a clock, and give inputs and assert outputs for every cycle. In vhdl, you generate clock signals for hardware implementations or simulation purposes. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. We use the after statement to generate the.. What Is A Clock Vhdl.

From stackoverflow.com

vhdl clock input to output as a finite state machine Stack Overflow What Is A Clock Vhdl We use the after statement to generate the. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. How to use a clock and do assertions. Process begin clk <= '0'; The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. For simulation,. What Is A Clock Vhdl.

From www.chegg.com

Describe the clock divider circuit in VHDL using the What Is A Clock Vhdl Process begin clk <= '0'; How to use a clock and do assertions. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. We use the after statement to generate the. In many test benches i see the following pattern for clock generation: In vhdl, you generate clock signals for hardware implementations or. What Is A Clock Vhdl.

From www.youtube.com

VHDL Lecture 24 Lab 8 Clock Divider and Counters Explanation YouTube What Is A Clock Vhdl This example shows how to generate a clock, and give inputs and assert outputs for every cycle. How to use a clock and do assertions. We use the after statement to generate the. Process begin clk <= '0'; Defining a clock signal in vhdl. In many test benches i see the following pattern for clock generation: In almost any testbench,. What Is A Clock Vhdl.

From electronica.guru

sincronización de entrada FPGA Electronica What Is A Clock Vhdl This example shows how to generate a clock, and give inputs and assert outputs for every cycle. We use the after statement to generate the. How to use a clock and do assertions. Process begin clk <= '0'; Clock is the backbone of any synchronous design. In vhdl, you generate clock signals for hardware implementations or simulation purposes. In many. What Is A Clock Vhdl.

From vhdlwhiz.com

Course I²C controller for interfacing a realtime clock/calendar What Is A Clock Vhdl The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. For simulation, you create clocks using simple. In many test benches i see the following pattern for clock generation: Process begin clk <=. What Is A Clock Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL What Is A Clock Vhdl This example shows how to generate a clock, and give inputs and assert outputs for every cycle. In many test benches i see the following pattern for clock generation: Clock is the backbone of any synchronous design. How to use a clock and do assertions. In vhdl, you generate clock signals for hardware implementations or simulation purposes. For simulation, you. What Is A Clock Vhdl.

From www.youtube.com

Build an FPGA Digital Clock VHDL Code Tutorial YouTube What Is A Clock Vhdl Defining a clock signal in vhdl. Clock is the backbone of any synchronous design. In many test benches i see the following pattern for clock generation: In vhdl, you generate clock signals for hardware implementations or simulation purposes. For simulation, you create clocks using simple. The next thing we do when writing a vhdl testbench is generate a clock and. What Is A Clock Vhdl.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL What Is A Clock Vhdl How to use a clock and do assertions. Process begin clk <= '0'; Clock is the backbone of any synchronous design. For simulation, you create clocks using simple. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. We use the after statement to generate the. This example shows how to. What Is A Clock Vhdl.

From www.youtube.com

Course preview I²C controller for interfacing a realtime clock What Is A Clock Vhdl The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Process begin clk <= '0'; In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. We use the after statement to generate the. Defining a clock signal in vhdl. Clock is the backbone. What Is A Clock Vhdl.

From www.youtube.com

VHDL BASIC Tutorial Clock Divider YouTube What Is A Clock Vhdl We use the after statement to generate the. How to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. In many test benches i see the following pattern for clock generation: In vhdl, you generate clock signals for hardware implementations or simulation purposes. Defining. What Is A Clock Vhdl.

From github.com

GitHub rydarg/DigitalClockVHDL Digital Clock [MM/SS] on Seven Seg What Is A Clock Vhdl We use the after statement to generate the. Defining a clock signal in vhdl. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. For simulation, you create clocks using simple. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. Process begin clk. What Is A Clock Vhdl.

From www.embeddedrelated.com

VHDL tutorial combining clocked and sequential logic Gene Breniman What Is A Clock Vhdl We use the after statement to generate the. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. How to use a clock and do assertions. Clock is the backbone of any synchronous design.. What Is A Clock Vhdl.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL What Is A Clock Vhdl For simulation, you create clocks using simple. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Process begin clk <= '0'; Defining a clock signal in vhdl. We use the after statement to generate the. How to use a clock and do assertions. Clock is the backbone of any synchronous. What Is A Clock Vhdl.

From www.youtube.com

Mod04 Lec22 VHDL Examples, FSM Clock YouTube What Is A Clock Vhdl In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. Clock is the backbone of any synchronous design. We use the after statement to generate the. The next thing we do when writing a. What Is A Clock Vhdl.

From copyprogramming.com

How do we set time in vhdl simulation for an fpga kit having clock of What Is A Clock Vhdl This example shows how to generate a clock, and give inputs and assert outputs for every cycle. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In vhdl, you generate clock signals for hardware implementations or simulation purposes. For simulation, you create clocks using simple. We use the after statement to. What Is A Clock Vhdl.

From github.com

GitHub muhammedkocaoglu/DigitalandAnalogClockonVGAUsingVHDL What Is A Clock Vhdl In vhdl, you generate clock signals for hardware implementations or simulation purposes. Clock is the backbone of any synchronous design. For simulation, you create clocks using simple. Defining a clock signal in vhdl. Process begin clk <= '0'; How to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise. What Is A Clock Vhdl.

From github.com

GitHub twinjie/VHDLAlarmClock Alarm clock created on the Nexys 4 What Is A Clock Vhdl We use the after statement to generate the. Defining a clock signal in vhdl. Process begin clk <= '0'; The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In many test benches i see the following pattern for clock generation: In vhdl, you generate clock signals for hardware implementations or simulation. What Is A Clock Vhdl.

From www.youtube.com

VHDL Assignment (Digital Clock with Alarm) YouTube What Is A Clock Vhdl Process begin clk <= '0'; In many test benches i see the following pattern for clock generation: In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Clock is the backbone of any. What Is A Clock Vhdl.

From www.slideserve.com

PPT VHDL Overview PowerPoint Presentation, free download ID6991479 What Is A Clock Vhdl Clock is the backbone of any synchronous design. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. In many test benches i see the following pattern for clock generation: Defining a clock signal in vhdl. We use the after statement to generate the. How to use a clock and do. What Is A Clock Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL What Is A Clock Vhdl In many test benches i see the following pattern for clock generation: In vhdl, you generate clock signals for hardware implementations or simulation purposes. Defining a clock signal in vhdl. Clock is the backbone of any synchronous design. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. The next thing. What Is A Clock Vhdl.

From www.youtube.com

FPGA LED blink VHDL FPGA learn by Examples Ep02 VHDL clock divider What Is A Clock Vhdl This example shows how to generate a clock, and give inputs and assert outputs for every cycle. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. For simulation, you create clocks using simple. Clock is the backbone of any synchronous design. In vhdl, you generate clock signals for hardware implementations or. What Is A Clock Vhdl.

From www.youtube.com

Electronics clock frequency divide by 5 vhdl (2 Solutions!!) YouTube What Is A Clock Vhdl For simulation, you create clocks using simple. How to use a clock and do assertions. Defining a clock signal in vhdl. In vhdl, you generate clock signals for hardware implementations or simulation purposes. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Clock is the backbone of any synchronous design. Process. What Is A Clock Vhdl.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL What Is A Clock Vhdl The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Defining a clock signal in vhdl. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. For simulation, you create clocks using simple. We use the after statement to generate the. Clock is. What Is A Clock Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL What Is A Clock Vhdl For simulation, you create clocks using simple. This example shows how to generate a clock, and give inputs and assert outputs for every cycle. Defining a clock signal in vhdl. How to use a clock and do assertions. Clock is the backbone of any synchronous design. Process begin clk <= '0'; We use the after statement to generate the. The. What Is A Clock Vhdl.

From www.youtube.com

Digital Alarm Clock on Altera DE2 FPGA in VHDL YouTube What Is A Clock Vhdl The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. In many test benches i see the following pattern for clock generation: Process begin clk <= '0'; For simulation, you create clocks using simple. Clock is the backbone of any synchronous design. How to use a clock and do assertions. This example. What Is A Clock Vhdl.

From www.youtube.com

VHDL alarm clock project YouTube What Is A Clock Vhdl In many test benches i see the following pattern for clock generation: Defining a clock signal in vhdl. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Process begin clk <= '0'; This example shows how to generate a clock, and give inputs and assert outputs for every cycle. In almost. What Is A Clock Vhdl.

From www.youtube.com

How to create a timer in VHDL YouTube What Is A Clock Vhdl Process begin clk <= '0'; We use the after statement to generate the. How to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Defining a clock signal in vhdl. In vhdl, you generate clock signals for hardware implementations or simulation purposes. This example. What Is A Clock Vhdl.

From vhdlwhiz.com

Course I²C controller for interfacing a realtime clock/calendar What Is A Clock Vhdl How to use a clock and do assertions. In vhdl, you generate clock signals for hardware implementations or simulation purposes. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. For simulation, you. What Is A Clock Vhdl.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL What Is A Clock Vhdl Process begin clk <= '0'; The next thing we do when writing a vhdl testbench is generate a clock and a reset signal. How to use a clock and do assertions. Clock is the backbone of any synchronous design. We use the after statement to generate the. This example shows how to generate a clock, and give inputs and assert. What Is A Clock Vhdl.