Logic Verilog . 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. A wire is a data type that can model physical wires to connect. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). the systemverilog value set consists of the following four basic values: // default value of logic type. Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”. if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: Conceptually assign’s are evaluated continuously, so whenever a value used in. $display (my_data=0x%0h en=%0b, my_data, en);

from www.youtube.com

the systemverilog value set consists of the following four basic values: systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. Conceptually assign’s are evaluated continuously, so whenever a value used in. $display (my_data=0x%0h en=%0b, my_data, en); A wire is a data type that can model physical wires to connect. if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: // default value of logic type. Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”.

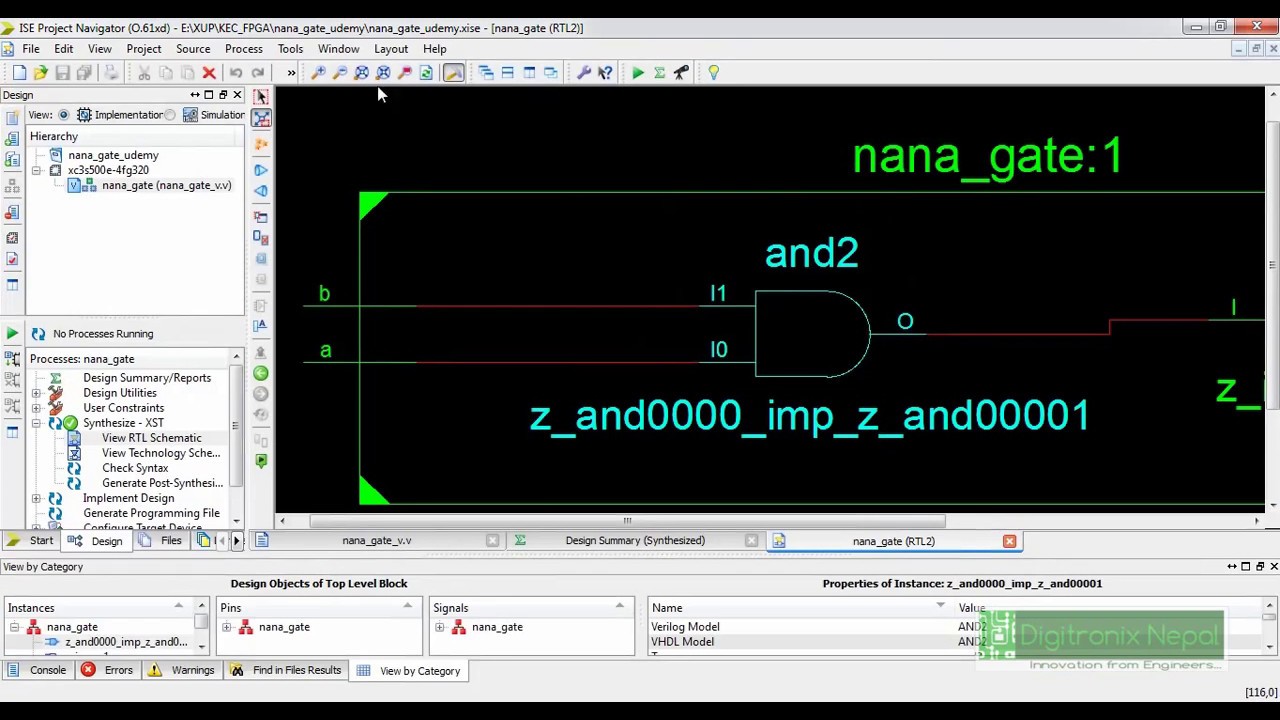

Logic Gate Design & Simulation in Verilog with Xilinx ISE YouTube

Logic Verilog Conceptually assign’s are evaluated continuously, so whenever a value used in. 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. Conceptually assign’s are evaluated continuously, so whenever a value used in. $display (my_data=0x%0h en=%0b, my_data, en); the systemverilog value set consists of the following four basic values: A wire is a data type that can model physical wires to connect. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: // default value of logic type.

From www.slideserve.com

PPT ECE 4680 Computer Architecture Verilog Presentation I. PowerPoint Logic Verilog A wire is a data type that can model physical wires to connect. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). Before we start understanding the “logic” data type for system verilog, let’s refresh. Logic Verilog.

From present5.com

Digital Design An Embedded Systems Approach Using Verilog Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”. Conceptually assign’s are evaluated continuously, so whenever a value used in. // default value of logic type. the systemverilog value set consists of the following four basic values: A wire is a data type that. Logic Verilog.

From www.ucsc-extension.edu

Digital Logic Design Using Verilog Course UCSC Silicon Valley Extension Logic Verilog the systemverilog value set consists of the following four basic values: $display (my_data=0x%0h en=%0b, my_data, en); A wire is a data type that can model physical wires to connect. Conceptually assign’s are evaluated continuously, so whenever a value used in. // default value of logic type. Before we start understanding the “logic” data type for system verilog, let’s refresh. Logic Verilog.

From www.chegg.com

Solved Write the verilog code for the 8bit ALU (Arithmetic Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. Conceptually assign’s are evaluated continuously, so whenever a. Logic Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID2400403 Logic Verilog if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: A wire is a data type that can model physical wires to connect. $display (my_data=0x%0h en=%0b, my_data, en); verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. . Logic Verilog.

From www.slideserve.com

PPT ECE 4680 Computer Architecture Verilog Presentation I. PowerPoint Logic Verilog the systemverilog value set consists of the following four basic values: verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. Conceptually assign’s are evaluated continuously, so whenever a value used in. 0 —represents a logic zero or a false condition 1 —represents a logic one or. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic and Verilog PowerPoint Presentation, free Logic Verilog the systemverilog value set consists of the following four basic values: verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. Conceptually assign’s are evaluated continuously, so whenever a value used in. A wire is a data type that can model physical wires to connect. // default. Logic Verilog.

From www.chegg.com

Solved Figure 8 shows a simple combinational logic circuit. Logic Verilog Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. A wire is a data type that can model physical wires to connect. $display (my_data=0x%0h en=%0b, my_data, en); . Logic Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); Conceptually assign’s are evaluated continuously, so whenever a value used in. // default value of logic type. the systemverilog value set consists of the following four basic values: 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. A. Logic Verilog.

From www.slideserve.com

PPT Verilog Basics PowerPoint Presentation, free download ID970632 Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). 0 —represents. Logic Verilog.

From www.youtube.com

18 Verilog Logic Values YouTube Logic Verilog systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: 0 —represents a logic zero or a. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Logic Verilog 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. Conceptually assign’s are evaluated continuously, so whenever a value used in. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. systemverilog. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic and Verilog PowerPoint Presentation, free Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: the. Logic Verilog.

From electronics.stackexchange.com

homework A 4 bit counter d flip flop with + 1 logic Verilog Logic Verilog if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: Conceptually assign’s are evaluated continuously, so whenever a value used in. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. A wire is a data type that can. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic and Verilog PowerPoint Presentation, free Logic Verilog A wire is a data type that can model physical wires to connect. // default value of logic type. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and. Logic Verilog.

From evokurt.weebly.com

Verilog decimal to binary 32 bit evokurt Logic Verilog the systemverilog value set consists of the following four basic values: if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”. $display (my_data=0x%0h en=%0b, my_data, en); verilog is a hardware. Logic Verilog.

From link.springer.com

Verilog (Part 1) SpringerLink Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be. Logic Verilog.

From studylib.net

Sequential Logic and Verilog Logic Verilog 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. A wire is a data type that can model physical wires to connect. Before we start understanding the “logic” data type for system verilog, let’s refresh verilog data types “reg” and “wire”. systemverilog introduced. Logic Verilog.

From www.youtube.com

Simple Combinational Logic Design in Verilog YouTube Logic Verilog A wire is a data type that can model physical wires to connect. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). 0 —represents a logic zero or a false condition 1 —represents a logic. Logic Verilog.

From www.youtube.com

Tutorial 20 Verilog code of 8 to 1 mux using 2 to 1 mux concept of Logic Verilog 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. A wire is a data type that can model physical wires to connect. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Logic Verilog $display (my_data=0x%0h en=%0b, my_data, en); Conceptually assign’s are evaluated continuously, so whenever a value used in. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). // default value of logic type. 0 —represents a logic. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Logic Verilog verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. // default value of logic type. Conceptually assign’s are evaluated continuously, so whenever a value used in. the systemverilog value set consists of the following four basic values: $display (my_data=0x%0h en=%0b, my_data, en); 0 —represents a logic. Logic Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID2400403 Logic Verilog A wire is a data type that can model physical wires to connect. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). 0 —represents a logic zero or a false condition 1 —represents a logic. Logic Verilog.

From www.youtube.com

Logic Gate Design & Simulation in Verilog with Xilinx ISE YouTube Logic Verilog 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. Before we start understanding the “logic” data type for system verilog, let’s refresh. Logic Verilog.

From studylib.net

Verilog Sequential Logic Logic Verilog Conceptually assign’s are evaluated continuously, so whenever a value used in. verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. $display (my_data=0x%0h. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Logic Verilog A wire is a data type that can model physical wires to connect. // default value of logic type. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). Before we start understanding the “logic” data. Logic Verilog.

From www.youtube.com

Sequential Logic In Verilog YouTube Logic Verilog if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). Conceptually assign’s are evaluated continuously, so whenever. Logic Verilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation Logic Verilog verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. Conceptually assign’s are evaluated continuously, so whenever a value used in. systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value. Logic Verilog.

From nokilfer.blogspot.com

4 To 1 Mux Verilog Code nokil Logic Verilog the systemverilog value set consists of the following four basic values: // default value of logic type. 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents an unknown logic value z. $display (my_data=0x%0h en=%0b, my_data, en); A wire is a data type that can model physical wires to. Logic Verilog.

From eliteengineerofficial.blogspot.com

LOGIC GATES USING VERILOG Logic Verilog verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. A wire is a data type that can model physical wires to connect. $display (my_data=0x%0h en=%0b, my_data, en); 0 —represents a logic zero or a false condition 1 —represents a logic one or a true condition x —represents. Logic Verilog.

From cselectricalandelectronics.com

Verilog Codes On Different Digital Logic Circuits, Programs On Verilog Logic Verilog if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). the systemverilog value set consists of. Logic Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Logic Verilog systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). the systemverilog value set consists of the following four basic values: 0 —represents a logic zero or a false condition 1 —represents a logic one. Logic Verilog.

From www.youtube.com

System Verilog tutorial Combinational logic design coding AND OR Logic Verilog the systemverilog value set consists of the following four basic values: systemverilog introduced the 'logic' type, which can behave both as 'wire' (can be driven by continuous assignments and ports) and as 'reg' (can hold a value and can be driven by procedural assignments). Conceptually assign’s are evaluated continuously, so whenever a value used in. 0 —represents a. Logic Verilog.

From www.studypool.com

SOLUTION Fundamentals of digital logic with verilog design third Logic Verilog verilog is a hardware description language (hdl) that is used to describe digital systems and circuits in the form of code. $display (my_data=0x%0h en=%0b, my_data, en); Conceptually assign’s are evaluated continuously, so whenever a value used in. // default value of logic type. the systemverilog value set consists of the following four basic values: A wire is a. Logic Verilog.

From userdiagrammeyer.z19.web.core.windows.net

Logical Operators In Verilog Logic Verilog Conceptually assign’s are evaluated continuously, so whenever a value used in. // default value of logic type. if we want to specify a behavior equivalent to combinational logic, use verilog’s operators and continuous assignment statements: the systemverilog value set consists of the following four basic values: A wire is a data type that can model physical wires to. Logic Verilog.