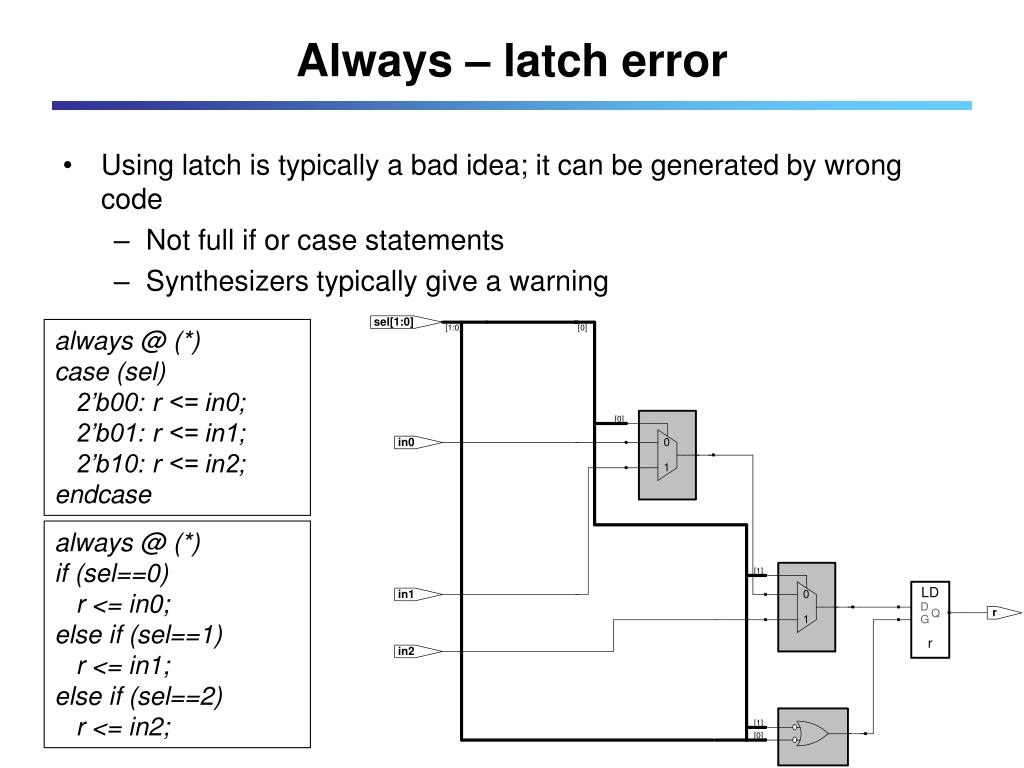

How To Avoid Latches In Verilog . Latches can lead to timing issues and race conditions. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Typical coding structures which will create latches in verilog and vhdl. To avoid latches in a hdl design , two major points you have to keep in mind. The way to prevent latches then is to ensure that in every. Whenever a combinational circuit is asked to hold its value, you get a latch. 1) make sure that you cover all possible. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog.

from www.slideserve.com

To avoid latches in a hdl design , two major points you have to keep in mind. Typical coding structures which will create latches in verilog and vhdl. The way to prevent latches then is to ensure that in every. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Whenever a combinational circuit is asked to hold its value, you get a latch. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. 1) make sure that you cover all possible. Latches can lead to timing issues and race conditions. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog.

PPT Verilog & FPGA PowerPoint Presentation, free download ID3542144

How To Avoid Latches In Verilog When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Latches can lead to timing issues and race conditions. To avoid latches in a hdl design , two major points you have to keep in mind. Whenever a combinational circuit is asked to hold its value, you get a latch. The way to prevent latches then is to ensure that in every. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. Typical coding structures which will create latches in verilog and vhdl. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. 1) make sure that you cover all possible.

From www.youtube.com

verilog code for SR FLIP FLOP with testbench YouTube How To Avoid Latches In Verilog To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. To avoid latches in a hdl design , two major points you have to keep in mind. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. How To Avoid Latches In Verilog.

From slideplayer.com

1021 UnderGraduate Project RTL Coding Style ppt download How To Avoid Latches In Verilog When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. To implement this memory the. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog Tutorial PowerPoint Presentation, free download ID1428843 How To Avoid Latches In Verilog 1) make sure that you cover all possible. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Typical coding structures which will create latches in verilog and vhdl. Learn how to avoid inferred latches in fsm designs by ensuring. How To Avoid Latches In Verilog.

From www.numerade.com

SOLVED The SR latch can be built using NAND gates or NOR gates. This How To Avoid Latches In Verilog Typical coding structures which will create latches in verilog and vhdl. Whenever a combinational circuit is asked to hold its value, you get a latch. 1) make sure that you cover all possible. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download How To Avoid Latches In Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Latches can lead to timing issues and race conditions. To avoid latches in a hdl design , two major points you have to keep in mind. When you have registered. How To Avoid Latches In Verilog.

From www.researchgate.net

(a) Verilog module which implements a NAND3 based How To Avoid Latches In Verilog 1) make sure that you cover all possible. Whenever a combinational circuit is asked to hold its value, you get a latch. Typical coding structures which will create latches in verilog and vhdl. The way to prevent latches then is to ensure that in every. To implement this memory the synthesis tool will insert a latch, often referred to as. How To Avoid Latches In Verilog.

From www.youtube.com

26 Describing D Latches and D FlipFlops in Verilog YouTube How To Avoid Latches In Verilog 1) make sure that you cover all possible. Latches can lead to timing issues and race conditions. Typical coding structures which will create latches in verilog and vhdl. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. In this article we will look at how transparent latches are synthesized from if. How To Avoid Latches In Verilog.

From blog.csdn.net

HDL—Verilog Language—Procedures—Avoiding latchesCSDN博客 How To Avoid Latches In Verilog When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. To avoid latches in a hdl design , two major points you have to keep in mind. The way to prevent latches then is to ensure that in every. Latches can lead to timing issues. How To Avoid Latches In Verilog.

From www.youtube.com

SR LATCH VERILOG PROGRAM IN DATA FLOW YouTube How To Avoid Latches In Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. 1) make sure that you cover all possible. Latches can lead to timing issues and race conditions. Whenever a combinational circuit is asked to hold its value, you get a. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation How To Avoid Latches In Verilog Typical coding structures which will create latches in verilog and vhdl. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. 1) make sure that you cover all possible. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate. How To Avoid Latches In Verilog.

From www.youtube.com

Sequential Circuit Design, D Latch, D flipflop, JK flipflop, Counter How To Avoid Latches In Verilog The way to prevent latches then is to ensure that in every. Typical coding structures which will create latches in verilog and vhdl. To avoid latches in a hdl design , two major points you have to keep in mind. Latches can lead to timing issues and race conditions. Whenever a combinational circuit is asked to hold its value, you. How To Avoid Latches In Verilog.

From www.youtube.com

System Verilog Interview Question Write the code for DFlip Flop in How To Avoid Latches In Verilog Typical coding structures which will create latches in verilog and vhdl. Whenever a combinational circuit is asked to hold its value, you get a latch. The way to prevent latches then is to ensure that in every. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of. How To Avoid Latches In Verilog.

From www.youtube.com

An Example Verilog Test Bench YouTube How To Avoid Latches In Verilog Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. The way to prevent latches then is to ensure that in every. Typical coding structures which will create latches in verilog and vhdl. In this article we will look at how transparent latches are synthesized from if statements and how. How To Avoid Latches In Verilog.

From www.youtube.com

15.1 Modeling Latches and FlipFlops in Verilog YouTube How To Avoid Latches In Verilog Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. Latches can lead to timing issues and race conditions. The way to prevent latches then. How To Avoid Latches In Verilog.

From www.youtube.com

Posedge detector using Verilog task YouTube How To Avoid Latches In Verilog 1) make sure that you cover all possible. Latches can lead to timing issues and race conditions. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. To avoid latches in a. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog Tutorial PowerPoint Presentation, free download ID882273 How To Avoid Latches In Verilog The way to prevent latches then is to ensure that in every. Whenever a combinational circuit is asked to hold its value, you get a latch. 1) make sure that you cover all possible. To avoid latches in a hdl design , two major points you have to keep in mind. In this article we will look at how transparent. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Lab 1 and 2 Digital System Design Using Verilog PowerPoint How To Avoid Latches In Verilog The way to prevent latches then is to ensure that in every. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Typical coding structures which will create latches in verilog and vhdl. When you have registered logic (in a. How To Avoid Latches In Verilog.

From www.youtube.com

Verilog Tutorial 20 Latch YouTube How To Avoid Latches In Verilog Latches can lead to timing issues and race conditions. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. 1) make sure that you cover all possible. Whenever a combinational circuit is asked to hold its value, you get a. How To Avoid Latches In Verilog.

From slideplayer.com

Hardware Basic & Verilog Introduction ppt download How To Avoid Latches In Verilog Latches can lead to timing issues and race conditions. To avoid latches in a hdl design , two major points you have to keep in mind. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Whenever a combinational circuit. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download How To Avoid Latches In Verilog To avoid latches in a hdl design , two major points you have to keep in mind. The way to prevent latches then is to ensure that in every. Typical coding structures which will create latches in verilog and vhdl. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog.. How To Avoid Latches In Verilog.

From mavink.com

Shift Register Verilog How To Avoid Latches In Verilog Whenever a combinational circuit is asked to hold its value, you get a latch. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. Typical. How To Avoid Latches In Verilog.

From www.w3cschool.cn

Verilog 避免Latch_w3cschool How To Avoid Latches In Verilog Latches can lead to timing issues and race conditions. To avoid latches in a hdl design , two major points you have to keep in mind. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will never generate a latch. Typical coding structures which will create latches in verilog. How To Avoid Latches In Verilog.

From www.chegg.com

Solved use the verilog code above and convert to a D latch How To Avoid Latches In Verilog To avoid latches in a hdl design , two major points you have to keep in mind. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. In this article we will. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog Modules for Common Digital Functions PowerPoint How To Avoid Latches In Verilog To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. Whenever a combinational circuit is asked to hold its value, you get a latch. 1) make sure that you cover all possible.. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog Tutorial PowerPoint Presentation, free download ID6095134 How To Avoid Latches In Verilog 1) make sure that you cover all possible. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Typical coding structures which will create latches in verilog and vhdl. Whenever a combinational circuit is asked to hold its value, you get a latch. The way to prevent latches then is to ensure. How To Avoid Latches In Verilog.

From www.chegg.com

Solved Sequential Logic; Active High/Low SR latch Design How To Avoid Latches In Verilog 1) make sure that you cover all possible. Typical coding structures which will create latches in verilog and vhdl. To avoid latches in a hdl design , two major points you have to keep in mind. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog & FPGA PowerPoint Presentation, free download ID3542144 How To Avoid Latches In Verilog To avoid latches in a hdl design , two major points you have to keep in mind. Latches can lead to timing issues and race conditions. Typical coding structures which will create latches in verilog and vhdl. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. When you have registered logic. How To Avoid Latches In Verilog.

From www.chegg.com

Solved 1.Fill in the blanks for the Verilog HDL behavioral How To Avoid Latches In Verilog Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. Latches can lead to timing issues and race conditions. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. The. How To Avoid Latches In Verilog.

From www.youtube.com

SR NOR Latch Verilog Code including Test Bench EC Junction How To Avoid Latches In Verilog Latches can lead to timing issues and race conditions. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. When you have registered logic (in a sequential process in vhdl or in a sequential always block in verilog) you will. How To Avoid Latches In Verilog.

From www.eeweb.com

Controlling Latches Before They Ruin Your Day EE How To Avoid Latches In Verilog 1) make sure that you cover all possible. The way to prevent latches then is to ensure that in every. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Typical coding structures which will create latches in verilog and. How To Avoid Latches In Verilog.

From www.youtube.com

Verilog Code of D latch YouTube How To Avoid Latches In Verilog 1) make sure that you cover all possible. To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. The way to prevent latches then is to ensure that in every. To avoid. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5198890 How To Avoid Latches In Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. To avoid latches in a hdl design , two major points you have to keep in mind. Latches can lead to timing issues and race conditions. 1) make sure that. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Verilog II CPSC 321 PowerPoint Presentation, free download ID How To Avoid Latches In Verilog To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Typical coding structures which will create latches in verilog and vhdl. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. Whenever a combinational circuit is asked to hold its value, you. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation How To Avoid Latches In Verilog To implement this memory the synthesis tool will insert a latch, often referred to as an implied latch. Whenever a combinational circuit is asked to hold its value, you get a latch. 1) make sure that you cover all possible. Typical coding structures which will create latches in verilog and vhdl. When you have registered logic (in a sequential process. How To Avoid Latches In Verilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download How To Avoid Latches In Verilog 1) make sure that you cover all possible. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Learn how to avoid inferred latches in fsm designs by ensuring full state coverage and using best practices in verilog. Latches can. How To Avoid Latches In Verilog.