Cycle Per Instruction Cache . Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. 14.2 is a metric that has been a part of the vtune interface for many years. For data accesses, which occur on about 1/3 of all. Cycles per instruction, or cpi, as defined in fig. Programs tend to reuse data and instructions near those they have used recently. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency.

from www.chegg.com

Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. For data accesses, which occur on about 1/3 of all. 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction, or cpi, as defined in fig. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency.

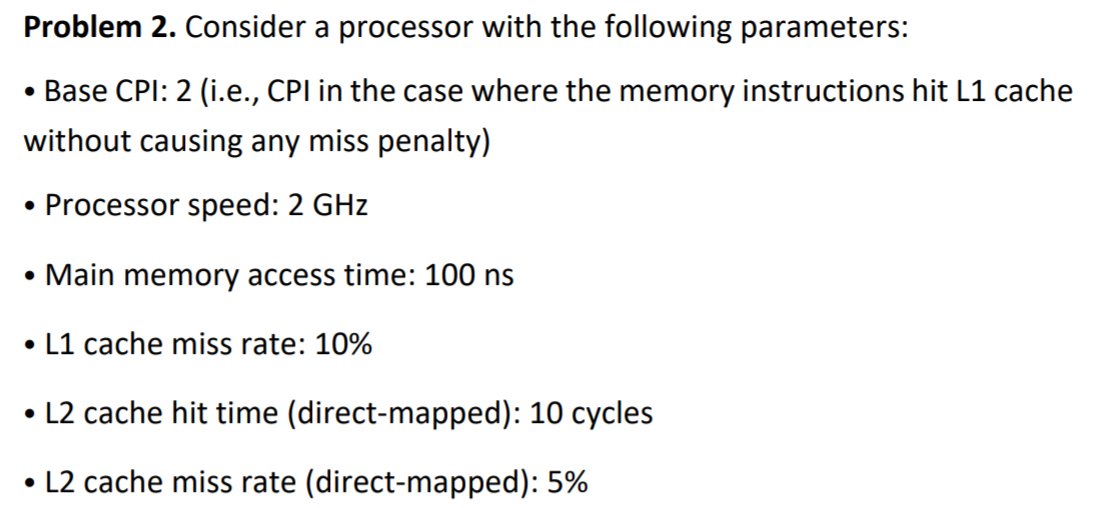

Problem 2. Consider a processor with the following

Cycle Per Instruction Cache For data accesses, which occur on about 1/3 of all. 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction, or cpi, as defined in fig. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. For data accesses, which occur on about 1/3 of all. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate.

From www.researchgate.net

Cycles per instruction stack [1]. Download Scientific Diagram Cycle Per Instruction Cache For data accesses, which occur on about 1/3 of all. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Computer Performance Evaluation Cycles Per Instruction (CPI Cycle Per Instruction Cache 14.2 is a metric that has been a part of the vtune interface for many years. For data accesses, which occur on about 1/3 of all. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Programs tend to reuse data and instructions near those they have used. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Performance of Cache Memory PowerPoint Presentation, free Cycle Per Instruction Cache For data accesses, which occur on about 1/3 of all. Programs tend to reuse data and instructions near those they have used recently. 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction, or cpi, as defined in fig. Memory is accessed via a separate data and instruction cache, with a. Cycle Per Instruction Cache.

From www.slideserve.com

PPT CHAPTER 2 PowerPoint Presentation ID458405 Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that has been a part of the vtune interface for many years. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one. Cycle Per Instruction Cache.

From itecnotes.com

Electronic Instruction cache’s purpose Valuable Tech Notes Cycle Per Instruction Cache Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. For data accesses, which occur on about 1/3 of all. Cycles per instruction, or cpi, as defined in fig. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Programs tend to reuse data. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Cache Memory and Performance PowerPoint Presentation, free Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. 14.2 is a metric that has been a part of the vtune interface for many years. Programs tend to reuse. Cycle Per Instruction Cache.

From www.cgdirector.com

What is a CPU's IPC? Instructions per Cycle explained Cycle Per Instruction Cache Programs tend to reuse data and instructions near those they have used recently. 14.2 is a metric that has been a part of the vtune interface for many years. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Cycles per instruction (cpi) is a pivotal metric for. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Instruction cycle PowerPoint Presentation, free download ID9333272 Cycle Per Instruction Cache Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Cycles per instruction, or cpi, as defined in fig. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10%. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Memory Hierarchy Motivation PowerPoint Presentation, free Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. 14.2 is a metric that has been a part of the vtune interface for many years. Memory is accessed. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Memory Hierarchy PowerPoint Presentation, free download ID3739739 Cycle Per Instruction Cache 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Cycles per instruction, or cpi, as defined in fig. For data accesses, which occur on about 1/3 of all. Programs tend to reuse data and instructions near those they have. Cycle Per Instruction Cache.

From ocw.mit.edu

21.1 Annotated Slides Computation Structures Electrical Engineering Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction, or cpi, as. Cycle Per Instruction Cache.

From community.ibm.com

Part 1 Lower MLC Software Costs with Processor Cache Optimization Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Cycles per instruction, or cpi, as defined in fig. Programs tend to reuse data and instructions near those they have used recently. For data accesses, which occur on about 1/3 of all. In a cisc architecture (x86, 68000,. Cycle Per Instruction Cache.

From studylib.net

CPU Performance Evaluation Cycles Per Instruction (CPI) Cycle Per Instruction Cache For data accesses, which occur on about 1/3 of all. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Cycles per instruction (cpi) is a pivotal metric for assessing. Cycle Per Instruction Cache.

From www.researchgate.net

CPU Cycles, Instructions, and Cache Misses Per Record Download Table Cycle Per Instruction Cache 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction, or cpi, as defined in fig. For data accesses, which occur on about 1/3 of all. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi) is a pivotal. Cycle Per Instruction Cache.

From www.slideserve.com

PPT What impact the memory system design? Principle of Locality Cycle Per Instruction Cache 14.2 is a metric that has been a part of the vtune interface for many years. For data accesses, which occur on about 1/3 of all. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Programs tend to reuse data and instructions near those they have used recently. Cycles per instruction,. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Chapter 8 Stacks PowerPoint Presentation, free download ID Cycle Per Instruction Cache For data accesses, which occur on about 1/3 of all. Cycles per instruction, or cpi, as defined in fig. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Programs tend to reuse data. Cycle Per Instruction Cache.

From www.slideserve.com

PPT CPU Performance Evaluation Cycles Per Instruction (CPI Cycle Per Instruction Cache Programs tend to reuse data and instructions near those they have used recently. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. For data accesses, which occur on about 1/3 of all. Cycles per instruction, or cpi, as defined in fig. 14.2 is a metric that has been a part of the vtune interface for. Cycle Per Instruction Cache.

From www.slideserve.com

PPT CPU Performance Evaluation Cycles Per Instruction (CPI Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. Programs tend to reuse data and instructions near those they have used recently. 14.2 is a metric that has been a part of the vtune interface for many years. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. For data accesses, which. Cycle Per Instruction Cache.

From www.researchgate.net

Simulation Cycles for Instruction Cache with varying block size Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Programs tend to reuse data and instructions near those they have used recently. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. In a cisc architecture (x86, 68000, vax) one instruction is powerful,. Cycle Per Instruction Cache.

From www.c-jump.com

The Instruction Cycle Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Programs tend to reuse data and instructions near those they have used recently. For data accesses, which occur on about 1/3 of all. Cycles per instruction (cpi) is a pivotal metric for assessing. Cycle Per Instruction Cache.

From www.chegg.com

Problem 2. Consider a processor with the following Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. 14.2 is a metric that has been a part of the vtune interface for many years. For data accesses, which occur on about 1/3 of all. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Performance of Cache Memory PowerPoint Presentation, free Cycle Per Instruction Cache Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that has been a part of the vtune interface for many years. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to. Cycle Per Instruction Cache.

From slidetodoc.com

Computer Performance Evaluation Cycles Per Instruction CPI Most Cycle Per Instruction Cache In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction, or cpi, as defined in fig. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that has been a part of the vtune interface for many years. For data accesses,. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Graduate Computer Architecture I PowerPoint Presentation, free Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that has. Cycle Per Instruction Cache.

From slidetodoc.com

The Memory Hierarchy Cache Main Memory and Virtual Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. 14.2 is a metric that has been a part of the vtune interface for many years. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Programs tend to reuse data and instructions near those they have used recently. Memory is accessed via. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Memory PowerPoint Presentation, free download ID4890173 Cycle Per Instruction Cache 14.2 is a metric that has been a part of the vtune interface for many years. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Cycles per instruction, or cpi, as defined in fig. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Memory is accessed. Cycle Per Instruction Cache.

From www.codingninjas.com

Instruction Cycle Coding Ninjas Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. For data accesses, which occur on about 1/3 of all. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. 14.2 is a metric that has been a part of the vtune interface for many years. Programs tend to. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Lecture 1 Course Introduction, Technology Trends, Performance Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. For data accesses, which occur on about 1/3 of all. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi) is a pivotal metric for assessing. Cycle Per Instruction Cache.

From www.slideserve.com

PPT Performance of Cache Memory PowerPoint Presentation, free Cycle Per Instruction Cache For data accesses, which occur on about 1/3 of all. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that. Cycle Per Instruction Cache.

From www.chegg.com

Solved Evaluate the CPI(clock cycles per Instruction ), MIPS Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. 14.2 is a metric that has been a part of the vtune interface for many years. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi). Cycle Per Instruction Cache.

From www.chegg.com

Solved 5. Assume the miss rate of an instruction cache is 2 Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that has been a part of the vtune interface for many years. Memory is accessed. Cycle Per Instruction Cache.

From studylib.net

Computer Performance Evaluation Cycles Per Instruction (CPI) Cycle Per Instruction Cache Cycles per instruction, or cpi, as defined in fig. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Programs tend to reuse data and instructions near those they have used recently. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. For data accesses, which occur on. Cycle Per Instruction Cache.

From www.chegg.com

Category Instructions CPI(Clock Cycle per Cycle Per Instruction Cache 14.2 is a metric that has been a part of the vtune interface for many years. For data accesses, which occur on about 1/3 of all. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Cycles per instruction, or cpi, as defined in fig. In a cisc architecture (x86, 68000, vax) one instruction is powerful,. Cycle Per Instruction Cache.

From slideplayer.com

Cache Optimization. ppt download Cycle Per Instruction Cache Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Programs tend to reuse data and instructions near those they have used recently. Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. 14.2 is a metric that has been a part of the. Cycle Per Instruction Cache.

From www.javatpoint.com

Instruction Cycle Computer Organization and Architecture Tutorial Cycle Per Instruction Cache Cycles per instruction (cpi) is a pivotal metric for assessing cpu performance and efficiency. Memory is accessed via a separate data and instruction cache, with a 5% instruction cache miss rate and 10% data miss rate. Cycles per instruction, or cpi, as defined in fig. 14.2 is a metric that has been a part of the vtune interface for many. Cycle Per Instruction Cache.