Transmission Gate Dff . A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,.

from kasaplow.weebly.com

However, m is isolated from x,. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of pmos and nmos are the complement of each. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d has continuously.

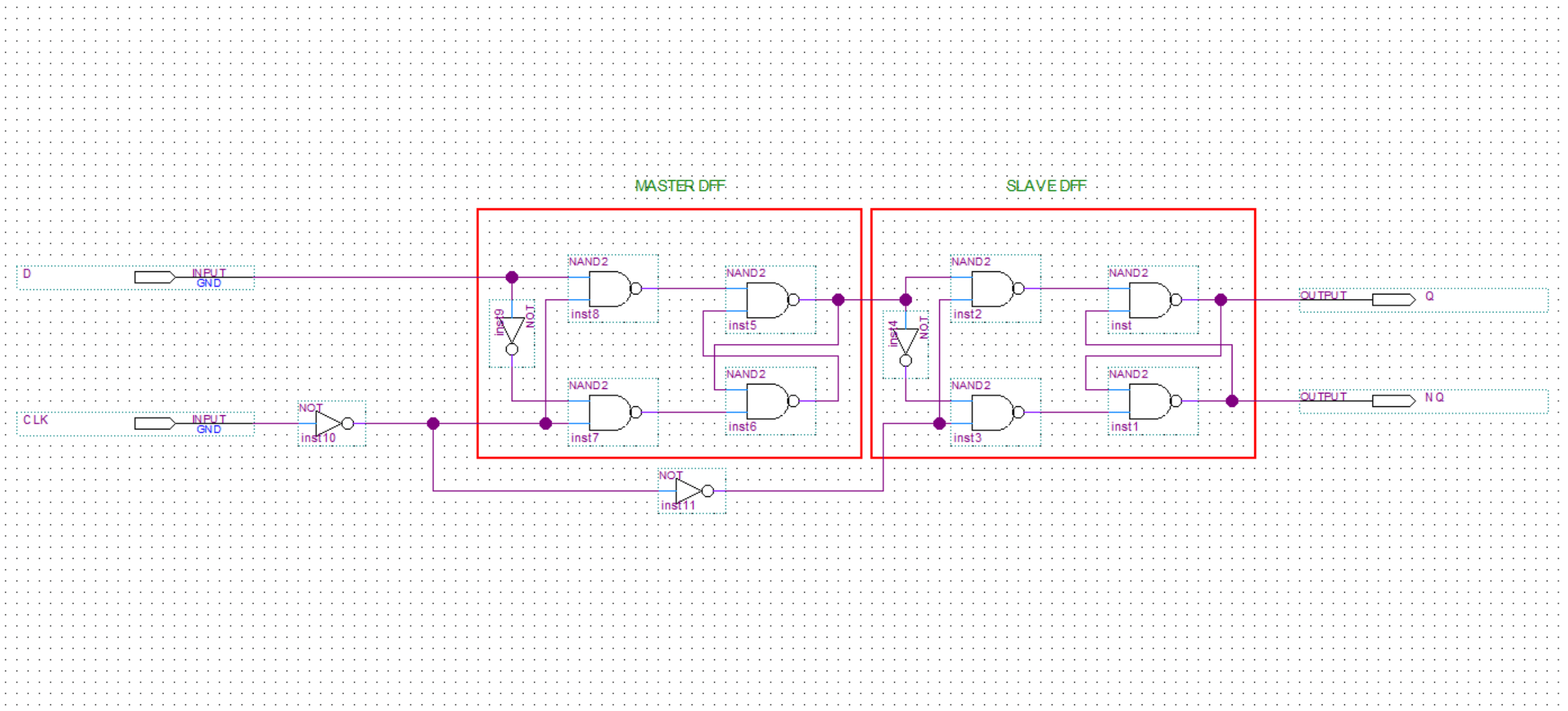

Edge triggered flip flop by using nor gates kasaplow

Transmission Gate Dff A transmission gate consists of a pmos and nmos connected by the drain. A transmission gate consists of a pmos and nmos connected by the drain. When the clock is low, x follows whatever value d has continuously. The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. However, m is isolated from x,. The following diagram illustrates the implementation of an inverter and transmission gate:

From cmosedu.com

Lab Transmission Gate Dff The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of pmos and nmos are the complement of each. When the clock is. Transmission Gate Dff.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Lecture 1 Circuits & Layout Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d. Transmission Gate Dff.

From teamvlsi.blogspot.com

Team VLSI Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. When the clock is. Transmission Gate Dff.

From www.circuitdiagram.co

Cmos Transmission Gate Circuit Circuit Diagram Transmission Gate Dff When the clock is low, x follows whatever value d has continuously. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of. Transmission Gate Dff.

From www.semanticscholar.org

Figure 8 from Design and Performance Analysis of Transmission Gate Transmission Gate Dff A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. However, m is isolated from x,. When the clock is low, x follows whatever value d has continuously. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates. Transmission Gate Dff.

From zhuanlan.zhihu.com

从MasterSlave DFF到TSPC DFF 知乎 Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d has continuously. The transmission gate is consists of a parallel connection of pmos & nmos. However, m is isolated from x,. A transmission gate consists of. Transmission Gate Dff.

From www.youtube.com

[62] D Flip Flop master slave DFF DFF with reset YouTube Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. However, m is isolated from x,. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is. Transmission Gate Dff.

From www.semanticscholar.org

Figure 2 from A High Speed Transmission Gate Logic Base 1/N Frequency Transmission Gate Dff However, m is isolated from x,. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d has continuously. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists. Transmission Gate Dff.

From cmosedu.com

Lab Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. However, m is isolated from x,. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of pmos and nmos are the complement of each. When the clock is. Transmission Gate Dff.

From cmosedu.com

Lab Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. When the clock is low, x follows whatever value d has continuously. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by. Transmission Gate Dff.

From www.youtube.com

Transmission Gate logic Implement Logic Gates using Transmission Transmission Gate Dff However, m is isolated from x,. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. When the clock is. Transmission Gate Dff.

From electronics.stackexchange.com

digital logic D flipflop frequency divider Electrical Engineering Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. However, m is isolated from x,. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of. Transmission Gate Dff.

From kasaplow.weebly.com

Edge triggered flip flop by using nor gates kasaplow Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. However, m is isolated from x,. When the clock is low, x follows whatever value d has continuously. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates. Transmission Gate Dff.

From www.slideserve.com

PPT CMOS Circuits PowerPoint Presentation, free download ID3362550 Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. The transmission gate is consists of a parallel connection of pmos & nmos. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of. Transmission Gate Dff.

From www.semanticscholar.org

Figure 8 from Layout Design of 5 Transistor D Flip Flop for Power and Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of. Transmission Gate Dff.

From www.researchgate.net

DFlip Flop using Transmission gates Download Scientific Diagram Transmission Gate Dff When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists. Transmission Gate Dff.

From www.studypool.com

SOLUTION 12 pass transistor and transmission gate logic circuits Transmission Gate Dff When the clock is low, x follows whatever value d has continuously. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. Two gate voltage of. Transmission Gate Dff.

From buzztech.in

CMOS Transmission Gate (Pass Gates) Buzztech Transmission Gate Dff The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. However, m is isolated from x,. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of a pmos and nmos connected by the drain. The following diagram illustrates. Transmission Gate Dff.

From www.slideserve.com

PPT CMOS Transmission Gate PowerPoint Presentation, free download Transmission Gate Dff However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is. Transmission Gate Dff.

From www.slideserve.com

PPT CMOS Transmission Gate PowerPoint Presentation, free download Transmission Gate Dff The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d has continuously. A transmission gate consists of a pmos and nmos connected by the drain. However, m is isolated from x,. Two gate voltage of. Transmission Gate Dff.

From www.youtube.com

DFF from masterslave latches and timing waveforms YouTube Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of a pmos and nmos connected by the drain. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. The transmission gate is consists. Transmission Gate Dff.

From www.semanticscholar.org

Figure 7 from Transmission gatebased approximate adders for inexact Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: Two gate voltage of pmos and nmos are the complement of each. The transmission gate is consists of a parallel connection of pmos & nmos. A transmission gate consists of a pmos and nmos connected by the drain. When the clock is low, x follows whatever value d. Transmission Gate Dff.

From www.youtube.com

Pass Transistor Transmission Gate Switch logic PDC Lec116 Transmission Gate Dff The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: A transmission gate consists of a pmos and nmos connected by the drain. When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,. Two gate voltage of. Transmission Gate Dff.

From cmosedu.com

Lab Transmission Gate Dff A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. When the clock is low, x follows whatever value d has continuously. The transmission gate is consists. Transmission Gate Dff.

From www.researchgate.net

TFET transmission gate based (a) 3‐stage cascaded delay chain,(b Transmission Gate Dff The transmission gate is consists of a parallel connection of pmos & nmos. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of a pmos and nmos connected by the drain. However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates. Transmission Gate Dff.

From www.researchgate.net

TSPC Dflipflop with SET and RESET lines. Download Scientific Diagram Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,. The transmission gate is consists. Transmission Gate Dff.

From www.researchgate.net

Various latch topologies a Transmissiongate based latch [11] b Transmission Gate Dff A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates. Transmission Gate Dff.

From www.allaboutcircuits.com

The CMOS Transmission Gate Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,. The transmission gate is consists of a parallel connection of pmos & nmos. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of. Transmission Gate Dff.

From electronics.stackexchange.com

digital logic D flip flop with asynchronous reset circuit design Transmission Gate Dff However, m is isolated from x,. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is. Transmission Gate Dff.

From www.slideserve.com

PPT CMOS Transmission Gate PowerPoint Presentation, free download Transmission Gate Dff When the clock is low, x follows whatever value d has continuously. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. The transmission gate is consists of a parallel connection of pmos & nmos. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of. Transmission Gate Dff.

From www.slideserve.com

PPT Lecture 10 Circuit Families PowerPoint Presentation, free Transmission Gate Dff When the clock is low, x follows whatever value d has continuously. Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists. Transmission Gate Dff.

From www.youtube.com

D Latch Implementation using Transmission Gate CMOS Transmission Gate Transmission Gate Dff The following diagram illustrates the implementation of an inverter and transmission gate: The transmission gate is consists of a parallel connection of pmos & nmos. A transmission gate consists of a pmos and nmos connected by the drain. Two gate voltage of pmos and nmos are the complement of each. However, m is isolated from x,. When the clock is. Transmission Gate Dff.

From electronics.stackexchange.com

digital logic D flipflop frequency divider Electrical Engineering Transmission Gate Dff The transmission gate is consists of a parallel connection of pmos & nmos. Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. When the clock is low, x follows whatever value d has continuously. However, m is isolated from x,. The following diagram illustrates. Transmission Gate Dff.

From www.slideserve.com

PPT FM Transmitter PowerPoint Presentation, free download ID722841 Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists of a parallel connection of pmos & nmos. The following diagram illustrates the implementation of an inverter and transmission gate: When the clock is low, x follows whatever value d. Transmission Gate Dff.

From www.youtube.com

Microwind Implementation of MUX Using TRANSMISSION GATES YouTube Transmission Gate Dff Two gate voltage of pmos and nmos are the complement of each. The following diagram illustrates the implementation of an inverter and transmission gate: However, m is isolated from x,. When the clock is low, x follows whatever value d has continuously. A transmission gate consists of a pmos and nmos connected by the drain. The transmission gate is consists. Transmission Gate Dff.