Wire Load Model Design Compiler . • defining wire load models: cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to.

from www.semanticscholar.org

before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. • defining wire load models:

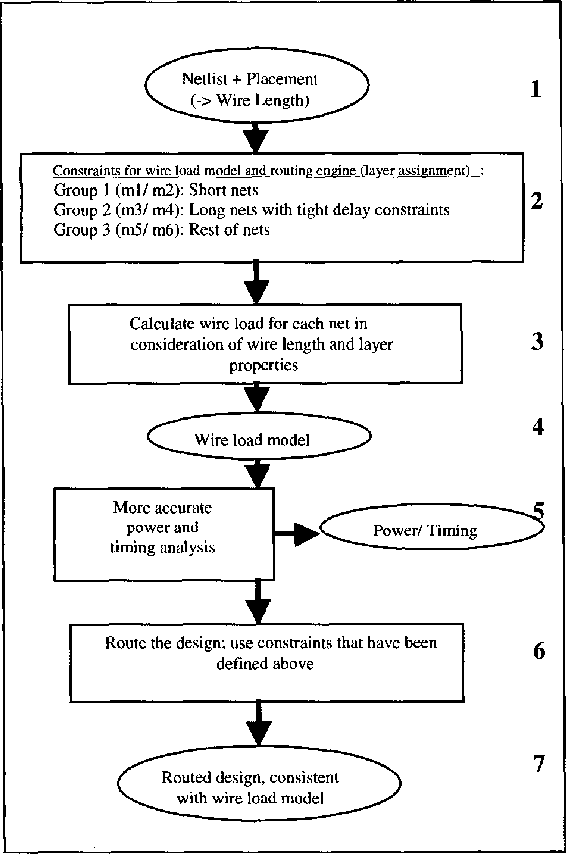

Figure 1 from A wire load model considering metal layer properties

Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. • defining wire load models: before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to.

From www.slideserve.com

PPT Design Compiler & TetraMAX PowerPoint Presentation, free download Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. •. Wire Load Model Design Compiler.

From www.slideserve.com

PPT Design Compiler & TetraMAX PowerPoint Presentation, free download Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before. Wire Load Model Design Compiler.

From blog.csdn.net

物理综合:关于wire_loadCSDN博客 Wire Load Model Design Compiler before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire.. Wire Load Model Design Compiler.

From www.cnblogs.com

物理综合:关于wire_load 魏老师说IC 博客园 Wire Load Model Design Compiler • defining wire load models: Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive. Wire Load Model Design Compiler.

From dxouvvlfz.blob.core.windows.net

Wire Load Model Types at Anna Leblanc blog Wire Load Model Design Compiler Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before you. Wire Load Model Design Compiler.

From www.youtube.com

𝐖𝐢𝐫𝐞 𝐋𝐨𝐚𝐝 𝐌𝐨𝐝𝐞𝐥 (𝐖𝐋𝐌) 𝐢𝐧 𝐒𝐓𝐀/𝐕𝐋𝐒𝐈 𝐰/ 𝐄𝐱𝐚𝐦𝐩𝐥𝐞𝐬 vlsiexcellence YouTube Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. Wire load. Wire Load Model Design Compiler.

From www.slideserve.com

PPT CSCI660 Introduction to VLSI Design PowerPoint Presentation Wire Load Model Design Compiler Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before you. Wire Load Model Design Compiler.

From www.slideserve.com

PPT ECE 681 VLSI Design Automation PowerPoint Presentation, free Wire Load Model Design Compiler before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output.. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models for synthesis Wire Load Model Design Compiler Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. — this paper presents. Wire Load Model Design Compiler.

From www.semanticscholar.org

Figure 1 from A wire load model considering metal layer properties Wire Load Model Design Compiler Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. • defining wire load models: cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good. Wire Load Model Design Compiler.

From vlsi.kr

DC, DCT, DCG 차이. Synopsys Design Compiler Topographical Graphical Mode Wire Load Model Design Compiler before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. • defining wire load models: before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. Wire load modeling allows you to estimate the effect of wire length and fanout on the. Wire Load Model Design Compiler.

From vlsi.kr

DC, DCT, DCG 차이. Synopsys Design Compiler Topographical Graphical Mode Wire Load Model Design Compiler before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. • defining wire load models: cell libraries (worst case and best case) operating conditions, wire load models, design rules input. Wire Load Model Design Compiler.

From www.cnblogs.com

物理综合:关于wire_load 魏老师说IC 博客园 Wire Load Model Design Compiler before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. • defining wire load models: before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. — this paper presents a novel design flow that enables a better forecast on layout. Wire Load Model Design Compiler.

From www.slideserve.com

PPT CSCI660 Introduction to VLSI Design PowerPoint Presentation Wire Load Model Design Compiler before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. . Wire Load Model Design Compiler.

From www.slideserve.com

PPT ECE 681 VLSI Design Automation PowerPoint Presentation, free Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. • defining wire load models: before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Environmental constraints Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. • defining wire load models: Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. — this paper. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Environmental constraints Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before going. Wire Load Model Design Compiler.

From blog.csdn.net

物理综合:关于wire_loadCSDN博客 Wire Load Model Design Compiler before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. • defining wire load models: cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is. Wire Load Model Design Compiler.

From www.slideserve.com

PPT ECE 681 VLSI Design Automation PowerPoint Presentation, free Wire Load Model Design Compiler before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. — this paper presents a. Wire Load Model Design Compiler.

From www.shangyexinzhi.com

DC、DCT与DCG_随芯所欲商业新知 Wire Load Model Design Compiler before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. • defining wire load models: cell libraries (worst case and best case) operating conditions, wire load models, design rules input. Wire Load Model Design Compiler.

From www.slideserve.com

PPT ECE 681 VLSI Design Automation PowerPoint Presentation, free Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. . Wire Load Model Design Compiler.

From www.slideserve.com

PPT CSCI660 Introduction to VLSI Design PowerPoint Presentation Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. • defining wire load models: — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before you synthesize the vhdl code {literally execute the design compiler {dc} compile. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design July 2013 Wire Load Model Design Compiler • defining wire load models: — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input. Wire Load Model Design Compiler.

From www.slideshare.net

Library Characterization Flow Wire Load Model Design Compiler before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. • defining wire load models: cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output.. Wire Load Model Design Compiler.

From www.slideserve.com

PPT Design Compiler & TetraMAX PowerPoint Presentation, free download Wire Load Model Design Compiler Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. • defining wire load models: — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it. Wire Load Model Design Compiler.

From zhuanlan.zhihu.com

IMPL14. set_wire_load_model & set_wire_load_mode浅析 知乎 Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models for synthesis Wire Load Model Design Compiler Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. — this paper presents a. Wire Load Model Design Compiler.

From www.slideserve.com

PPT CSCI660 Introduction to VLSI Design PowerPoint Presentation Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. • defining wire load models: — this paper presents a novel design flow that enables a better forecast on layout characteristics. Wire Load Model Design Compiler.

From www.slideserve.com

PPT ECE 681 VLSI Design Automation PowerPoint Presentation, free Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. • defining wire load models: before you synthesize the vhdl code {literally execute the design compiler {dc} compile. Wire Load Model Design Compiler.

From www.scribd.com

Wire Load Model PDF Computing Computer Engineering Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to.. Wire Load Model Design Compiler.

From slidetodoc.com

On the Relevance of Wire Load Models Wire Load Model Design Compiler before going for floorplanning or layout, wire load models (wlm) can be used to calculate interconnect wiring. Wire load modeling allows you to estimate the effect of wire length and fanout on the resistance,. before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. • defining wire load. Wire Load Model Design Compiler.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models Wire Load Model Design Compiler cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. • defining wire load models: Wire load modeling allows you to estimate the effect of wire length and fanout. Wire Load Model Design Compiler.

From www.cnblogs.com

物理综合:关于wire_load 魏老师说IC 博客园 Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. • defining wire load models: before you synthesize the vhdl code {literally execute the design compiler {dc} compile command), it is good practice to. before going for floorplanning or layout, wire load models (wlm) can be. Wire Load Model Design Compiler.

From cnuinfotech-cd.blogspot.com

Phases of a compiler COMPILER DESIGN Wire Load Model Design Compiler — this paper presents a novel design flow that enables a better forecast on layout characteristics by computing a wire. cell libraries (worst case and best case) operating conditions, wire load models, design rules input drive strengths, output. • defining wire load models: before going for floorplanning or layout, wire load models (wlm) can be used. Wire Load Model Design Compiler.