Arm Cpu Topology . Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. Syntactically they are defined as device tree nodes. The arm cpu architecture specifies the behavior of a cpu implementation. Support arm cpu topology definition. Access to these system registers is. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. The arm central processor unit (cpu) architecture comes in three varieties: Achieve different performance characteristics with different implementations of. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy;

from www.cnx-software.com

Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Support arm cpu topology definition. The arm central processor unit (cpu) architecture comes in three varieties: The arm cpu architecture specifies the behavior of a cpu implementation. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Access to these system registers is. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy;

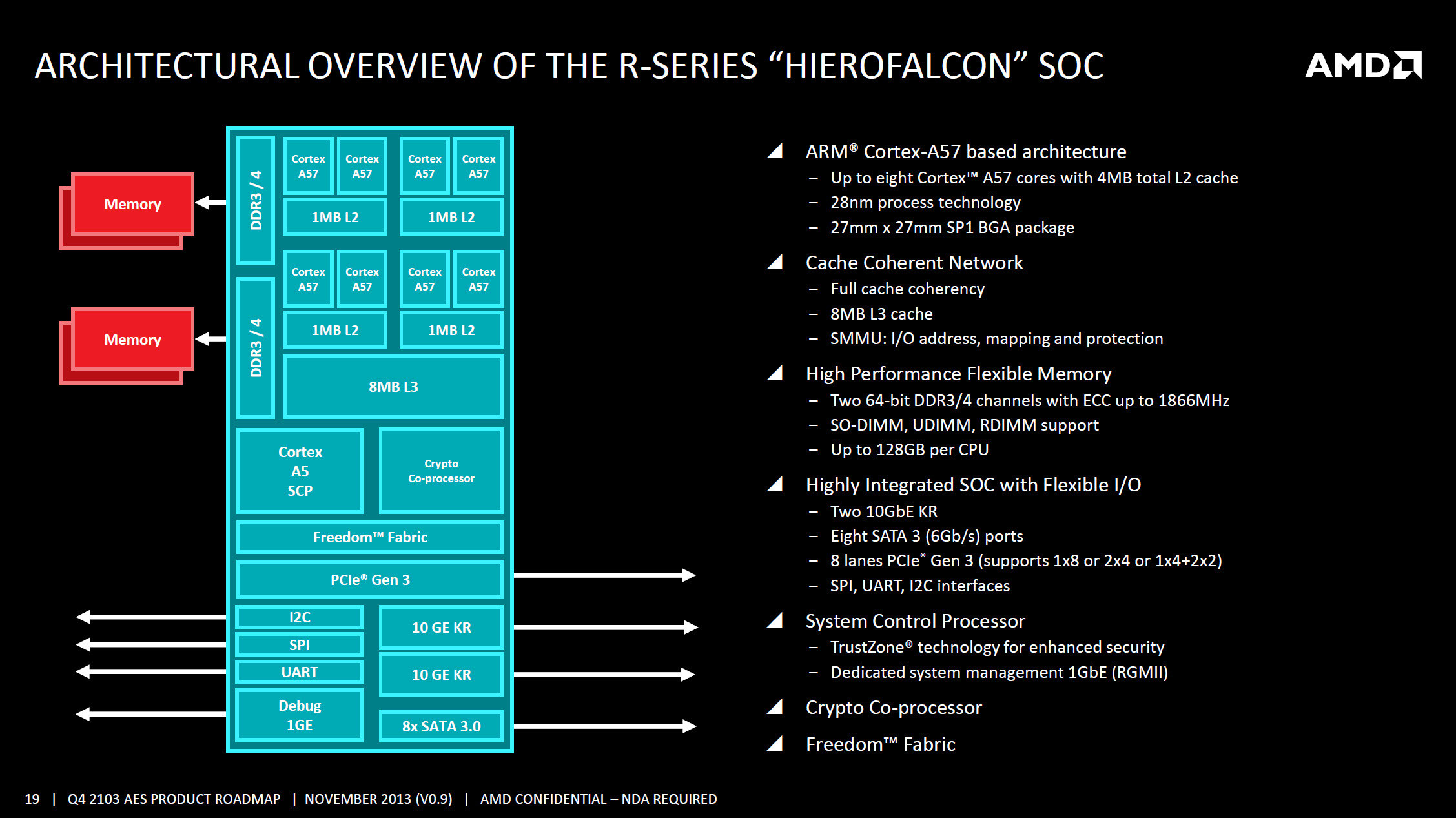

AMD “Hierofalcon” Octacore ARM Cortex A57 Embedded Processors to Ship

Arm Cpu Topology Access to these system registers is. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Access to these system registers is. The arm central processor unit (cpu) architecture comes in three varieties: Achieve different performance characteristics with different implementations of. Support arm cpu topology definition. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The arm cpu architecture specifies the behavior of a cpu implementation. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Syntactically they are defined as device tree nodes. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system.

From www.youtube.com

ARM Processors Modes AMR7 LPC2148 Advanced Processors YouTube Arm Cpu Topology The arm central processor unit (cpu) architecture comes in three varieties: Access to these system registers is. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The mpidr register defines affinity between processors which is then used. Arm Cpu Topology.

From www.starlab.io

How the Xen Hypervisor Supports CPU Virtualization on ARM — Star Lab Arm Cpu Topology The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The arm central processor unit (cpu) architecture comes in three varieties: Syntactically they are defined as device tree. Arm Cpu Topology.

From www.zdnet.com

Arm processors Everything you need to know now Arm Cpu Topology The arm cpu architecture specifies the behavior of a cpu implementation. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The arm central processor unit (cpu) architecture comes in three varieties: Syntactically they are defined as device tree nodes. Arm's dynamiq technology combines the big and little cpus into a single, fully. Arm Cpu Topology.

From community.arm.com

Arm Fundamentals Intro to understanding Arm processors Architectures Arm Cpu Topology The arm central processor unit (cpu) architecture comes in three varieties: The arm cpu architecture specifies the behavior of a cpu implementation. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Support arm. Arm Cpu Topology.

From www.youtube.com

ARM core Data flow model YouTube Arm Cpu Topology The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Access to these system registers is. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. Support arm cpu topology definition. Syntactically they are defined as device tree nodes. Arm's dynamiq. Arm Cpu Topology.

From pcper.com

ARM Introduces DynamIQ Technology PC Perspective Arm Cpu Topology The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Syntactically they are defined as device tree nodes. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy;. Arm Cpu Topology.

From community.arm.com

10 Useful Facts of the CortexM System Design Kit Architectures and Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. The arm cpu architecture specifies the behavior of a cpu implementation.. Arm Cpu Topology.

From phys.org

ARM Introduces New CortexA5 PowerEfficient and CostEffective Arm Cpu Topology Syntactically they are defined as device tree nodes. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. Achieve different performance characteristics with different implementations of. Access to these system registers is.. Arm Cpu Topology.

From blog.csdn.net

ARM、ARM架构、ARM架构芯片_arm芯片CSDN博客 Arm Cpu Topology The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Syntactically they are defined as device tree nodes. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine). Arm Cpu Topology.

From www.tomshardware.com

Arm Details Neoverse V1 and N2 Platforms, New Mesh Design Tom's Hardware Arm Cpu Topology Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Access to these system registers is. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Achieve different performance characteristics with different implementations of. The arm cpu architecture specifies the behavior of a cpu implementation. Syntactically they are. Arm Cpu Topology.

From kronos-ref-stack.docs.arm.com

Heterogeneous InterProcessor Communication (HIPC) — Arm Kronos Arm Cpu Topology The arm cpu architecture specifies the behavior of a cpu implementation. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. The arm central processor unit (cpu) architecture comes in three varieties: Achieve different performance characteristics with different implementations of. Access to these system registers is. Arm (stylised in lowercase as arm, formerly an. Arm Cpu Topology.

From www.watelectronics.com

What is ARM Processor ARM Architecture and Applications Arm Cpu Topology The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Syntactically they are defined as device tree nodes. The arm central processor unit (cpu) architecture comes in three varieties: Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The mpidr. Arm Cpu Topology.

From www.embeddedinsights.com

Embedded Insights Embedded Processing Directory ARM CortexR4(F) Arm Cpu Topology Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Syntactically they are defined as device tree nodes. The arm central processor unit (cpu) architecture comes in three varieties: Arm (stylised in lowercase as arm, formerly an. Arm Cpu Topology.

From www.slideserve.com

PPT ARM Processor Architecture (II) PowerPoint Presentation, free Arm Cpu Topology The arm central processor unit (cpu) architecture comes in three varieties: The arm cpu architecture specifies the behavior of a cpu implementation. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. Syntactically they are defined as device tree nodes. Access to these system registers is. The. Arm Cpu Topology.

From bitsum.com

cputopology Arm Cpu Topology Syntactically they are defined as device tree nodes. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. The arm cpu architecture specifies the behavior of a cpu implementation. The arm central processor unit. Arm Cpu Topology.

From www.anandtech.com

A new CI700 Coherent Interconnect & NI700 NoC For SoCs Arm Arm Cpu Topology Access to these system registers is. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Support arm cpu topology definition. Achieve different performance characteristics with different implementations of. The arm central processor unit (cpu) architecture comes in three varieties: The mpidr register defines affinity between processors which is then used to describe. Arm Cpu Topology.

From wccftech.com

ARM Announces the CortexM0+ as the World's Most EnergyEfficient Processor Arm Cpu Topology The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. The arm central processor unit (cpu) architecture comes in three varieties: Access to these system registers is. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. Support. Arm Cpu Topology.

From www.efxkits.co.uk

ARM Cortex A9 Processor Architecture and Features Arm Cpu Topology The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Support arm cpu topology definition. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Achieve different performance characteristics with different implementations. Arm Cpu Topology.

From www.slideserve.com

PPT ARM Processor Architecture (II) PowerPoint Presentation, free Arm Cpu Topology Syntactically they are defined as device tree nodes. Support arm cpu topology definition. The arm cpu architecture specifies the behavior of a cpu implementation. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Achieve different performance characteristics with different implementations of. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines. Arm Cpu Topology.

From www.youtube.com

Learn the Fundamentals of ARM® Cortex®M0 Processor and DesignStartTM Arm Cpu Topology Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. The arm central processor unit (cpu) architecture comes in three varieties: Access to these system registers is. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The arm architecture defines a. Arm Cpu Topology.

From www.anandtech.com

Arm Unveils Client CPU Performance Roadmap Through 2020 Taking Intel Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. The arm cpu architecture specifies the behavior of a cpu implementation. Syntactically they are defined as device tree nodes. The arm central processor unit. Arm Cpu Topology.

From www.anandtech.com

CPU Chip Topologies Amazon's Armbased Graviton2 Against AMD and Arm Cpu Topology Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. The arm central processor unit (cpu) architecture comes in three varieties: The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Achieve different performance characteristics with different implementations of. Cpu topology bindings allow one to associate. Arm Cpu Topology.

From michaelbambrick.com

Arm Processor Instruction Set Arm Cpu Topology The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Arm topology bindings allow one to associate cpu nodes with hierarchical groups. Arm Cpu Topology.

From blog.csdn.net

Linux arm cpu topology_mpidrCSDN博客 Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The arm central processor unit (cpu) architecture comes in three varieties: Syntactically they are defined as device tree nodes. The arm cpu architecture specifies the behavior of a cpu implementation. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding. Arm Cpu Topology.

From copperhilltech.com

A Brief Introduction to the ARM Cortex M3 Processor Copperhill Arm Cpu Topology Achieve different performance characteristics with different implementations of. Syntactically they are defined as device tree nodes. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The arm central processor unit (cpu) architecture comes in three varieties: The arm cpu architecture specifies the behavior of a cpu. Arm Cpu Topology.

From iestol.blogspot.com

Arm Announces Mobile Armv9 CPU Microarchitectures CortexX2, Cortex Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Access to these system registers is. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Syntactically they are defined as device tree nodes. The arm architecture defines a set of feature registers, which. Arm Cpu Topology.

From zhuanlan.zhihu.com

世界第一ARM CPU?鲲鹏920规格 知乎 Arm Cpu Topology Support arm cpu topology definition. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Access to these system registers is. The arm cpu architecture specifies the behavior of a cpu implementation. Syntactically they are defined as device tree. Arm Cpu Topology.

From www.anandtech.com

New DSU110 L3 & Cluster Massively More Bandwidth Arm Announces Arm Cpu Topology Syntactically they are defined as device tree nodes. Access to these system registers is. Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. The arm central processor. Arm Cpu Topology.

From www.anandtech.com

DynamIQ Exploring DynamIQ and ARM’s New CPUs CortexA75, CortexA55 Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Access to these system registers is. Support arm cpu topology definition. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. The. Arm Cpu Topology.

From www.cnx-software.com

AMD “Hierofalcon” Octacore ARM Cortex A57 Embedded Processors to Ship Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Syntactically they are defined as device tree nodes. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Access to these system registers is. The arm cpu architecture specifies the behavior of a cpu. Arm Cpu Topology.

From community.arm.com

First Armv9 Cortex CPUs for Consumer Compute Processors blog Arm Cpu Topology The arm central processor unit (cpu) architecture comes in three varieties: Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. Cpu topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Syntactically. Arm Cpu Topology.

From www.anandtech.com

A new CI700 Coherent Interconnect & NI700 NoC For SoCs Arm Arm Cpu Topology Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The arm cpu architecture specifies the behavior of a cpu implementation. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; Arm's dynamiq technology combines the big and little cpus. Arm Cpu Topology.

From www.anandtech.com

Arm Announces CortexR82 First 64bit Real Time Processor Arm Cpu Topology Arm (stylised in lowercase as arm, formerly an acronym for advanced risc machines and originally acorn risc machine) is a family of risc. The arm cpu architecture specifies the behavior of a cpu implementation. Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The arm central processor unit (cpu) architecture comes in. Arm Cpu Topology.

From news.mydrivers.com

高通发布第5代自主ARM CPU架构Falkor:24核10nm高通,ARM,Intel,10nm ——快科技(驱动之家旗下媒体)科技改变未来 Arm Cpu Topology Arm's dynamiq technology combines the big and little cpus into a single, fully integrated cluster. The arm architecture defines a set of feature registers, which describe the capabilities of the cpu/system. Achieve different performance characteristics with different implementations of. The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. The arm. Arm Cpu Topology.

From www.anandtech.com

Arm's CortexA76 CPU Unveiled Taking Aim at the Top for 7nm Arm Cpu Topology Arm topology bindings allow one to associate cpu nodes with hierarchical groups corresponding to the system hierarchy; The mpidr register defines affinity between processors which is then used to describe the cpu topology of an arm. Achieve different performance characteristics with different implementations of. The arm cpu architecture specifies the behavior of a cpu implementation. The arm central processor unit. Arm Cpu Topology.