Z In System Verilog . Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. The verilog standard defines four types of bit values: Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. Types that can have unknown (x) and high. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. It basically means that you aren't driving the output of the. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Z represents a high impedance state, but why would you want that? If the second operand of a. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the.

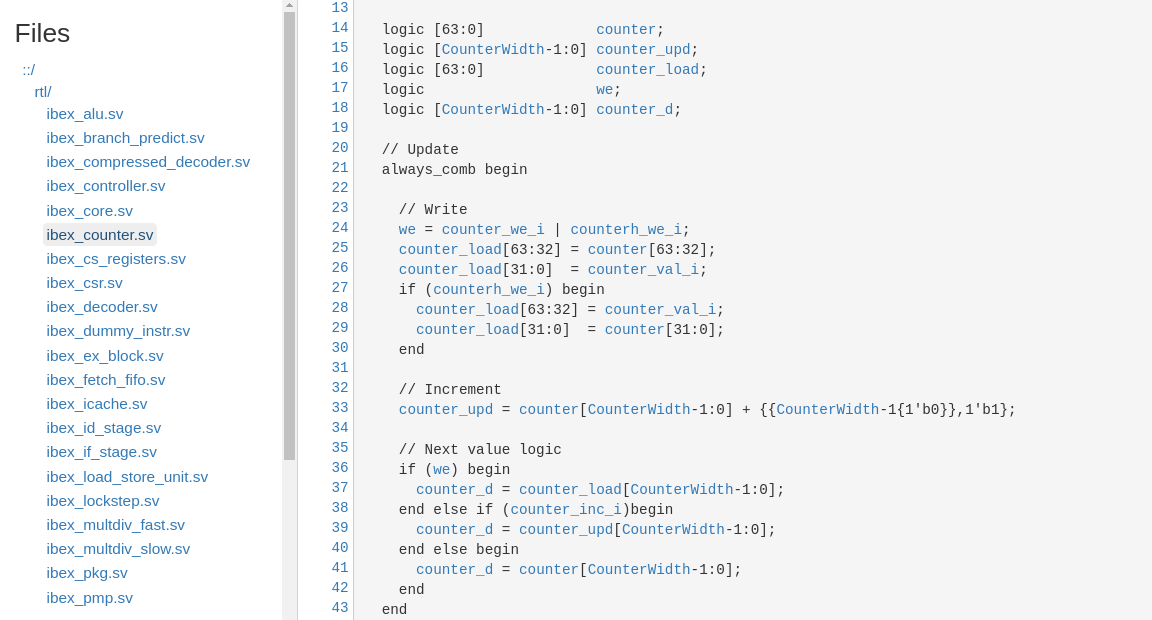

from www.chipsalliance.org

The verilog standard defines four types of bit values: It basically means that you aren't driving the output of the. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. Z represents a high impedance state, but why would you want that? Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. If the second operand of a. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. Types that can have unknown (x) and high.

Open Source SystemVerilog Tools in ASIC Design Chips Alliance

Z In System Verilog Z represents a high impedance state, but why would you want that? Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. Types that can have unknown (x) and high. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. The verilog standard defines four types of bit values: Z represents a high impedance state, but why would you want that? Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. It basically means that you aren't driving the output of the. If the second operand of a.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 09 Function and Task YouTube Z In System Verilog Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Z represents a high impedance state, but why would you want that? Values 0 and 1 serve the same purpose as in languages such as. Z In System Verilog.

From www.youtube.com

[Verilog 강의 10강] Verilog Simulation 3 YouTube Z In System Verilog Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. The verilog standard defines four types of bit values: Z represents a high impedance state, but why would you want that? The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate. Z In System Verilog.

From mungfali.com

Verilog Symbols Z In System Verilog Z represents a high impedance state, but why would you want that? If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. 0, 1, x, and z where 0 means low, 1 means high, x means. Z In System Verilog.

From verificationacademy.com

Assertion to check x or z when signal toggles instead of every clock Z In System Verilog 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. It basically means that you aren't driving the output of the. If the second operand of a. Types that can have unknown (x) and high. If you want to check that all the bits in data are z, you can write if (data. Z In System Verilog.

From www.slideserve.com

PPT Verilog For Computer Design PowerPoint Presentation, free Z In System Verilog Types that can have unknown (x) and high. Z represents a high impedance state, but why would you want that? The verilog standard defines four types of bit values: Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. 0, 1, x, and z where 0 means low, 1 means high, x. Z In System Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID2400403 Z In System Verilog Z represents a high impedance state, but why would you want that? It basically means that you aren't driving the output of the. The verilog standard defines four types of bit values: If the second operand of a. Types that can have unknown (x) and high. If you want to check that all the bits in data are z, you. Z In System Verilog.

From www.microcontrollertips.com

How to structure SystemVerilog for reuse as Portable Stimulus Z In System Verilog It basically means that you aren't driving the output of the. Z represents a high impedance state, but why would you want that? If the second operand of a. The verilog standard defines four types of bit values: If you want to check that all the bits in data are z, you can write if (data === 'z) if you. Z In System Verilog.

From slidetodoc.com

Hardware Description Languages Verilog z Verilog y Structural Z In System Verilog The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. Types that can have unknown (x) and high. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that. Z In System Verilog.

From gbu-presnenskij.ru

Verilog HDL Simulation With Ams Simulator MixedSignal, 45 OFF Z In System Verilog 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Z represents a high impedance state, but why would you want that? Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. The widest operand in our new expression is {c, z}, which. Z In System Verilog.

From slidetodoc.com

Hardware Description Languages Verilog z Verilog y Structural Z In System Verilog Z represents a high impedance state, but why would you want that? 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. If the second operand of a. The verilog standard defines four types of bit values: Types that can have unknown (x) and high. It basically means that you aren't driving the. Z In System Verilog.

From www.vrogue.co

Module Hierarchy Example 1 Verilog Pro vrogue.co Z In System Verilog 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. It basically means that you aren't driving the output of the. If the second operand of a. The widest operand in our new expression is. Z In System Verilog.

From mavink.com

What Is Verilog Z In System Verilog The verilog standard defines four types of bit values: 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Z represents a high impedance state, but why would you want that? Types that can have unknown (x) and high. If the second operand of a. It basically means that you aren't driving the. Z In System Verilog.

From mavink.com

Verilog Xor Operator Z In System Verilog The verilog standard defines four types of bit values: The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. If you want to check that all the. Z In System Verilog.

From www.youtube.com

System Verilog tutorial Combinational logic design coding AND OR Z In System Verilog The verilog standard defines four types of bit values: It basically means that you aren't driving the output of the. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. Types that can have unknown (x) and high. Z represents a high impedance state,. Z In System Verilog.

From www.chipverify.com

Verilog Module Instantiations Z In System Verilog Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. Z represents a high impedance state, but why would you want that? It basically means that you aren't driving the output of the. If you want to check that all the bits in data are z, you can write if (data ===. Z In System Verilog.

From www.chegg.com

Solved 4. Draw the circuit corresponding to the Verilog Z In System Verilog The verilog standard defines four types of bit values: If the second operand of a. Types that can have unknown (x) and high. Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. Z represents a high impedance state, but why would you want that? It basically means that you aren't driving. Z In System Verilog.

From enginelibirresolute.z21.web.core.windows.net

System Verilog Tutorial For Beginners Pdf Z In System Verilog 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. If the second operand of a. Values 0 and 1 serve the same purpose as in languages. Z In System Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID905399 Z In System Verilog Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. The verilog standard defines four types of bit values: Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. Types that can have unknown (x) and high. It basically means that you. Z In System Verilog.

From blog.csdn.net

systemVerilog操作符及语法_use systemverilog mode insteadCSDN博客 Z In System Verilog Types that can have unknown (x) and high. Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. If the second operand of a. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. The widest operand in our new expression is {c,. Z In System Verilog.

From www.youtube.com

Module 3 Reduction / shift /Concatenation / Conditional / replication Z In System Verilog If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. Let's look at some of the. Z In System Verilog.

From www.slideserve.com

PPT The data types in Systemverilog PowerPoint Presentation, free Z In System Verilog Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. If the second operand of a. Z represents a high impedance state, but why would you want that? It basically means that you aren't driving the output of the. Types that can have unknown (x) and high. Let's look at. Z In System Verilog.

From www.slideserve.com

PPT Dataflow Verilog PowerPoint Presentation, free download ID2990697 Z In System Verilog Z represents a high impedance state, but why would you want that? It basically means that you aren't driving the output of the. The verilog standard defines four types of bit values: If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit. Z In System Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID2400403 Z In System Verilog If the second operand of a. Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. The verilog standard defines four types of bit values: The widest operand in our new expression is. Z In System Verilog.

From wiringdiagramkoh.z21.web.core.windows.net

Convert Systemverilog To Verilog Z In System Verilog If the second operand of a. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. It basically means that you aren't driving the output of the. The verilog standard defines four types of bit values:. Z In System Verilog.

From slidetodoc.com

Hardware Description Languages Verilog z Verilog y Structural Z In System Verilog Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. It basically means that you aren't driving the output of the. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. If you want to check. Z In System Verilog.

From www.chipsalliance.org

Open Source SystemVerilog Tools in ASIC Design Chips Alliance Z In System Verilog Types that can have unknown (x) and high. Z represents a high impedance state, but why would you want that? If the second operand of a. The verilog standard defines four types of bit values: Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. The widest operand in our. Z In System Verilog.

From www.youtube.com

Posedge detector using Verilog task YouTube Z In System Verilog Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. Types that can have unknown (x) and high. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the.. Z In System Verilog.

From diagrampartunimparted.z21.web.core.windows.net

System Verilog Reference Manual Pdf Z In System Verilog It basically means that you aren't driving the output of the. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. Z represents a high impedance state, but why would you want that? Values 0 and. Z In System Verilog.

From stackoverflow.com

system verilog Hazards in the wave in systemverilog Stack Overflow Z In System Verilog It basically means that you aren't driving the output of the. Let's look at some of the operators in verilog that would enable synthesis tools realize appropriate hardware elements. Z represents a high impedance state, but why would you want that? The verilog standard defines four types of bit values: Types that can have unknown (x) and high. If you. Z In System Verilog.

From www.tina.com

SystemVerilog Simulation Z In System Verilog If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. The verilog standard defines four types of bit values:. Z In System Verilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 17a Concurrent Assertions YouTube Z In System Verilog Z represents a high impedance state, but why would you want that? The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Values 0 and 1 serve. Z In System Verilog.

From manualdatagnashing.z21.web.core.windows.net

System Verilog Tutorial For Beginners Pdf Z In System Verilog 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. Types that can have unknown (x) and high. The verilog standard defines four types of bit values: The widest operand in our new. Z In System Verilog.

From enginelibirresolute.z21.web.core.windows.net

Verilog To System Verilog Z In System Verilog It basically means that you aren't driving the output of the. 0, 1, x, and z where 0 means low, 1 means high, x means unknown, and z. The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. Values 0 and 1 serve the. Z In System Verilog.

From www.youtube.com

Functions and Tasks in SystemVerilog with conceptual examples YouTube Z In System Verilog The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. Types that can have unknown (x) and high. Values 0 and 1 serve the same purpose as in languages such as c/c++, but x and z are hardware. Let's look at some of the. Z In System Verilog.

From www.numerade.com

SOLVED 2. Write a structural style model in SystemVerilog for the Z In System Verilog The widest operand in our new expression is {c, z}, which is 5 bits wide, so when we evaluate x + y, we get 10010 2. If you want to check that all the bits in data are z, you can write if (data === 'z) if you want to check that any bit in data is z, use the.. Z In System Verilog.