Second Clock Verilog . either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock divider is simulated. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. Usage will normally produce a. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle.

from www.chegg.com

either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. The verilog clock divider is simulated. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. Usage will normally produce a.

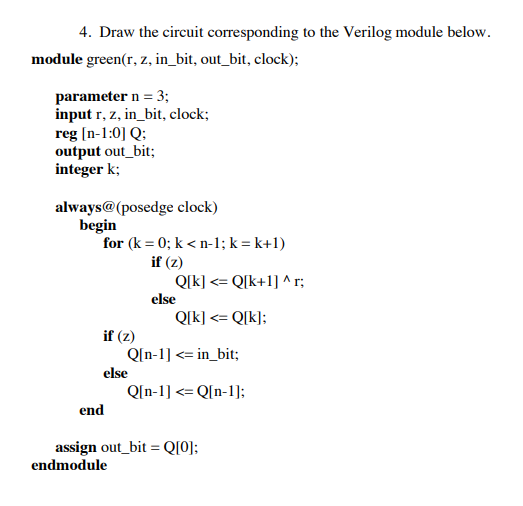

Solved 4. Draw the circuit corresponding to the Verilog

Second Clock Verilog either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. The verilog clock divider is simulated. Usage will normally produce a. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Second Clock Verilog either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Usage will normally produce a. i am working on xilinx ise, i have tried following code to. Second Clock Verilog.

From www.youtube.com

Verilog Code of Clock Generator with TB to generate CLK with Varying Second Clock Verilog this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. . Second Clock Verilog.

From github.com

GitHub merino22/DigitalClock Digital Clock developed in Hardware Second Clock Verilog Usage will normally produce a. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays. Second Clock Verilog.

From hetpro-store.com

Verilog Diseño de Contadores y Clocks HeTProTutoriales Second Clock Verilog either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock divider is simulated. this verilog project provides full verilog code for the clock divider on fpga. Second Clock Verilog.

From www.slideserve.com

PPT Verilog II CPSC 321 PowerPoint Presentation, free download ID Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. the following verilog clock. Second Clock Verilog.

From illustrationarttutorialgraphicdesign.blogspot.com

how to design a timer in verilog illustrationarttutorialgraphicdesign Second Clock Verilog The verilog clock divider is simulated. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. this verilog project provides full verilog code for the clock divider on fpga. Second Clock Verilog.

From verilogprojects.com

Clock Divider in Verilog Verilog Projects Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock divider is simulated. . Second Clock Verilog.

From www.youtube.com

verilog code ring counter johnsons counter YouTube Second Clock Verilog The verilog clock divider is simulated. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. Usage will normally produce a. the following verilog clock. Second Clock Verilog.

From www.slideserve.com

PPT Chapter 15Introduction to Verilog Testbenches PowerPoint Second Clock Verilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Usage will normally produce a. The verilog clock divider is simulated. i am working on xilinx ise, i have tried following. Second Clock Verilog.

From www.docsity.com

Generating a ClockVerilog HDL and FPGAsLecture Slides Docsity Second Clock Verilog Usage will normally produce a. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i'm using a fpga (bemicromax10) to create a digital clock. Second Clock Verilog.

From www.youtube.com

How to generate clock in Verilog HDL YouTube Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated. the following verilog clock generator module has three parameters to tweak the three different properties as discussed. Second Clock Verilog.

From www.researchgate.net

Figure A5. VerilogA code of the clock amplitudebased control Second Clock Verilog Usage will normally produce a. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays. Second Clock Verilog.

From www.pinterest.se

Verilog code for Alarm clock on FPGA Block Diagram, Circuits, Arduino Second Clock Verilog this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated. Usage will normally produce a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following verilog clock generator module has three parameters to tweak the. Second Clock Verilog.

From devcodef1.com

Verilog HDL Time Clock A Comprehensive Guide to Hardware Description Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty. Second Clock Verilog.

From www.youtube.com

digital clock by verilog code on fpga de2 kit YouTube Second Clock Verilog i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock divider is simulated. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on. Second Clock Verilog.

From www.youtube.com

5 Ways To Generate Clock Signal In Verilog YouTube Second Clock Verilog this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following. Second Clock Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5709023 Second Clock Verilog The verilog clock divider is simulated. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on. Second Clock Verilog.

From www.transtutors.com

(Get Answer) GR 2400HW 3 Verilog/DigitalDesign/Clocks/Counters/Mux Second Clock Verilog The verilog clock divider is simulated. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. either you should use a power of two clock signal (32.768 khz is a common clock for. Second Clock Verilog.

From exojsfvro.blob.core.windows.net

Generating Clock In Verilog at John Saunders blog Second Clock Verilog i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. Usage will normally. Second Clock Verilog.

From www.chegg.com

Solved 4. Draw the circuit corresponding to the Verilog Second Clock Verilog The verilog clock divider is simulated. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital. Second Clock Verilog.

From www.youtube.com

21 Verilog Clock Generator YouTube Second Clock Verilog this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following. Second Clock Verilog.

From www.chegg.com

this is verilog code for digital clock.i need help Second Clock Verilog The verilog clock divider is simulated. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. either you should use a power of two clock signal (32.768 khz is a common clock for. Second Clock Verilog.

From www.youtube.com

How to generate clock in Verilog HDL Verilog code of clock generator Second Clock Verilog either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. . Second Clock Verilog.

From www.youtube.com

VERILOG & FPGA Project DIGITAL CLOCK WITH ALARM AND FLEXIBLE TIME Second Clock Verilog i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. either you should use a power of two clock signal (32.768 khz is a common clock for these applications). Second Clock Verilog.

From stackoverflow.com

verilog 1 Second ClkDivider Simulation Not Working Stack Overflow Second Clock Verilog i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock divider is simulated. Usage will normally produce a. i'm using a fpga (bemicromax10) to create a digital clock. Second Clock Verilog.

From www.codenong.com

verilog 实现多功能数字钟,定时,报时,校时功能 码农家园 Second Clock Verilog either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock divider is simulated. i'm using a fpga (bemicromax10) to create a digital clock using seven segment. Second Clock Verilog.

From exogvchsq.blob.core.windows.net

Verilog Testbench Clock Example at Albert Kellum blog Second Clock Verilog Usage will normally produce a. The verilog clock divider is simulated. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following verilog clock generator module has three parameters to tweak the. Second Clock Verilog.

From www.youtube.com

25 Verilog Clock Divider YouTube Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. The verilog clock. Second Clock Verilog.

From verilogprojects.com

Clock Divider in Verilog Verilog Projects Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. . Second Clock Verilog.

From www.chegg.com

Solved I need only the (verilog code) for clock module and Second Clock Verilog Usage will normally produce a. either you should use a power of two clock signal (32.768 khz is a common clock for these applications) or you should. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. i'm using a fpga (bemicromax10) to create a digital clock using seven. Second Clock Verilog.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Second Clock Verilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. i am working on xilinx ise, i have tried following code to get 1 second clock with 50% duty cycle. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. The verilog clock. Second Clock Verilog.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube Second Clock Verilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. The verilog clock divider is simulated. this verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. either you should use a power of two clock signal (32.768 khz is a common. Second Clock Verilog.

From www.chegg.com

Solved Type up Verilog Verilog program use delay to Second Clock Verilog The verilog clock divider is simulated. Usage will normally produce a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. the following verilog clock generator module has three parameters to tweak the three different. Second Clock Verilog.

From www.scribd.com

Verilog Code of Clubbing Two Clocks PDF Computer Engineering Second Clock Verilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. i am working on xilinx ise,. Second Clock Verilog.

From electrodast.weebly.com

Clock divider verilog electrodast Second Clock Verilog i'm using a fpga (bemicromax10) to create a digital clock using seven segment displays on a. Usage will normally produce a. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. either you should use a power of two clock signal (32.768 khz is a common clock for these. Second Clock Verilog.