Define Simulation Verilog . The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog.

from cefbhoou.blob.core.windows.net

A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation.

Simulation Tools Verilog at Mercedes Sparrow blog

Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation.

From www.mathworks.com

Verilog Testbench MATLAB & Simulink Define Simulation Verilog Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. A verilog testbench is a simulation environment used to verify the functionality and correctness of. Define Simulation Verilog.

From www.youtube.com

Tutorial on Writing Simulation Testbench on Verilog with VIVADO YouTube Define Simulation Verilog A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the. Define Simulation Verilog.

From cefbhoou.blob.core.windows.net

Simulation Tools Verilog at Mercedes Sparrow blog Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted. Define Simulation Verilog.

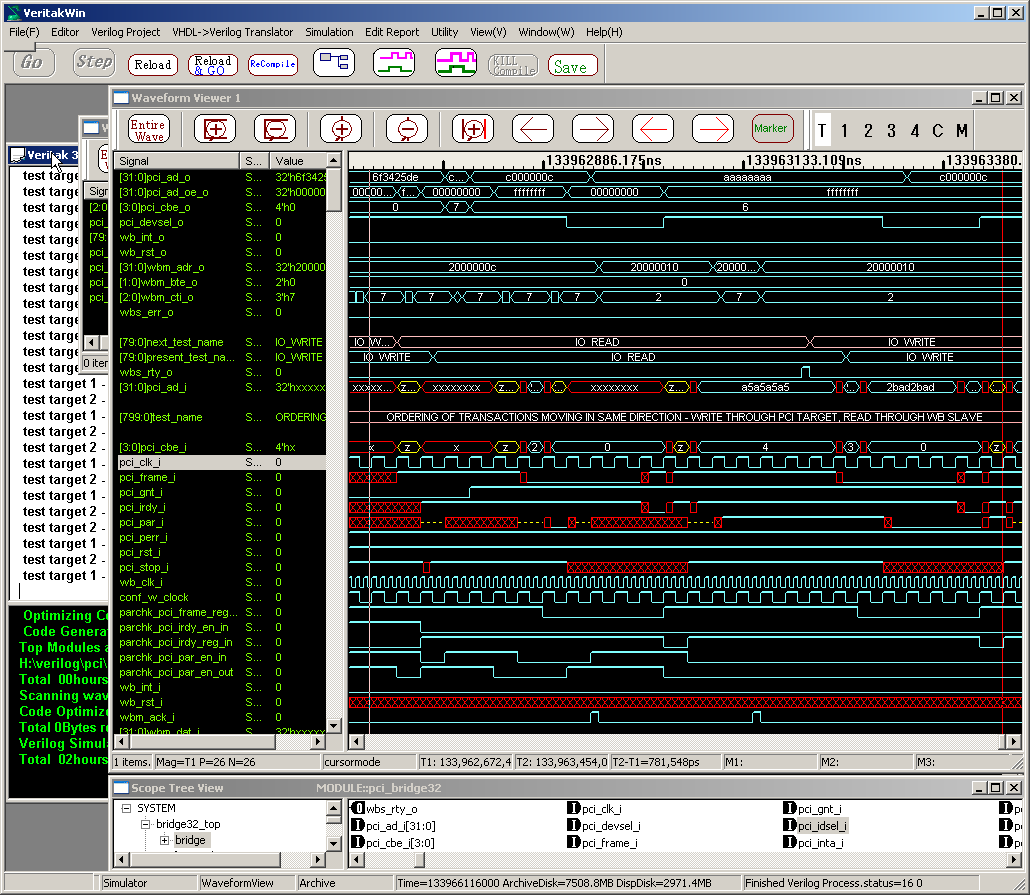

From www.syncad.com

VeriLogger Pro screen shot Define Simulation Verilog Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. The verilog source that represents the simulation model and the test bench is compiled into. Define Simulation Verilog.

From www.chipverify.com

Verilog Module Instantiations Define Simulation Verilog Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and. Define Simulation Verilog.

From digilent.com

Verilog® HDL Project 1 Digilent Reference Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a. Define Simulation Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5709023 Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and. Define Simulation Verilog.

From help.simetrix.co.uk

Verilog A Reference A Simple Device Model Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. A verilog testbench is a simulation environment used to verify the functionality and correctness of. Define Simulation Verilog.

From www.slideserve.com

PPT Chapter 11 PowerPoint Presentation, free download ID3713476 Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow.. Define Simulation Verilog.

From www.youtube.com

Verilog Simulation YouTube Define Simulation Verilog X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a. Define Simulation Verilog.

From www.youtube.com

Verilog Tutorial 13 `define, parameter and localparam YouTube Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and. Define Simulation Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID2400403 Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. The. Define Simulation Verilog.

From stackoverflow.com

verilog Xilinx FIFO IP block output in simulation Stack Overflow Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. Simulation is a technique of applying different input stimulus to the design at different times to. Define Simulation Verilog.

From www.numerade.com

SOLVED Design an arbiter (FSM in Verilog and test using Xilinx Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when. Define Simulation Verilog.

From community.cadence.com

Verilog HDL simulation with ams simulator MixedSignal Design Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in. Define Simulation Verilog.

From www.numerade.com

SOLVED Using Verilog gatelevel and structural specification Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation.. Define Simulation Verilog.

From www.profotho.co

verilog simulator VERILOG Cdmambile Define Simulation Verilog A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a. Define Simulation Verilog.

From www.youtube.com

ALU Design in Verilog with Testbench Simulation in Modelsim Define Simulation Verilog X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. A verilog testbench is a simulation environment used to verify the. Define Simulation Verilog.

From www.semanticscholar.org

DigitalJS a Visual Verilog Simulator for Teaching Semantic Scholar Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the. Define Simulation Verilog.

From junkyhor.weebly.com

Failure to obtain a verilog simulation license junkyhor Define Simulation Verilog X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. This tutorial explores verilog simulation and synthesis, discussing their differences. Define Simulation Verilog.

From exozhyxag.blob.core.windows.net

Clock Doubler Verilog at Marvin Edwards blog Define Simulation Verilog X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. The verilog source that represents the simulation model and the. Define Simulation Verilog.

From www.youtube.com

(온라인 워크숍) [Verilog 강의 10강] Verilog Simulation 3 YouTube Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. Simulation is a technique of applying different input stimulus to the design at different times to check if. Define Simulation Verilog.

From slideplayer.com

Introduction to Verilog sonoma ppt download Define Simulation Verilog X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. This tutorial explores verilog simulation and synthesis, discussing their differences and. Define Simulation Verilog.

From www.tina.com

SystemVerilog Simulation Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. In this fpga tutorial, we demonstrate how to write a testbench in verilog,. Define Simulation Verilog.

From www.tina.com

SystemVerilog Simulation Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. A verilog testbench is a simulation environment used to verify the functionality and correctness of a. Define Simulation Verilog.

From hackaday.io

Verilog Simulation Tools Details Hackaday.io Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. A verilog testbench is a simulation environment used to verify the functionality and. Define Simulation Verilog.

From www.youtube.com

Verilog code and test bench of Register File and RAM ModelSim Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the. Define Simulation Verilog.

From www.syncad.com

Verilog Simulator Verilog Compiler Synapticad Define Simulation Verilog X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. The verilog source that represents the simulation model and the test bench. Define Simulation Verilog.

From www.slideserve.com

PPT Basic Logic Design with Verilog Hardware Description Language Define Simulation Verilog In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when the predicted value is an. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in. Define Simulation Verilog.

From community.cadence.com

How to define a binary matrix parameter in Verilog A Custom IC Design Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. X unknown value (simulation) “x” is used by simulators when a wire hasn’t been initialized to a known value or when. Define Simulation Verilog.

From www.researchgate.net

The simulation using ‘Verilog Scenario Generator’ and ‘ModelSim’ (a Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow.. Define Simulation Verilog.

From joiqlstgi.blob.core.windows.net

What Is Simulation In Math Definition at Daniel Arce blog Define Simulation Verilog A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves. Define Simulation Verilog.

From electronics.stackexchange.com

verilog How does this SystemVerilog compiler directive work Define Simulation Verilog A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. In this fpga tutorial, we demonstrate how to write a testbench in verilog, simulate a design with icarus verilog, and view. The. Define Simulation Verilog.

From www.slideserve.com

PPT Verilog HDL Introduction PowerPoint Presentation, free download Define Simulation Verilog This tutorial explores verilog simulation and synthesis, discussing their differences and significance in the design flow. A verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the verilog. The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a. Define Simulation Verilog.

From circuitgenerator.com

Modelsim tutorial Inverter verilog code and testbench simulation Define Simulation Verilog The verilog source that represents the simulation model and the test bench is compiled into an executable form and executed by a simulation. Simulation is a technique of applying different input stimulus to the design at different times to check if the rtl code behaves the intended. A verilog testbench is a simulation environment used to verify the functionality and. Define Simulation Verilog.