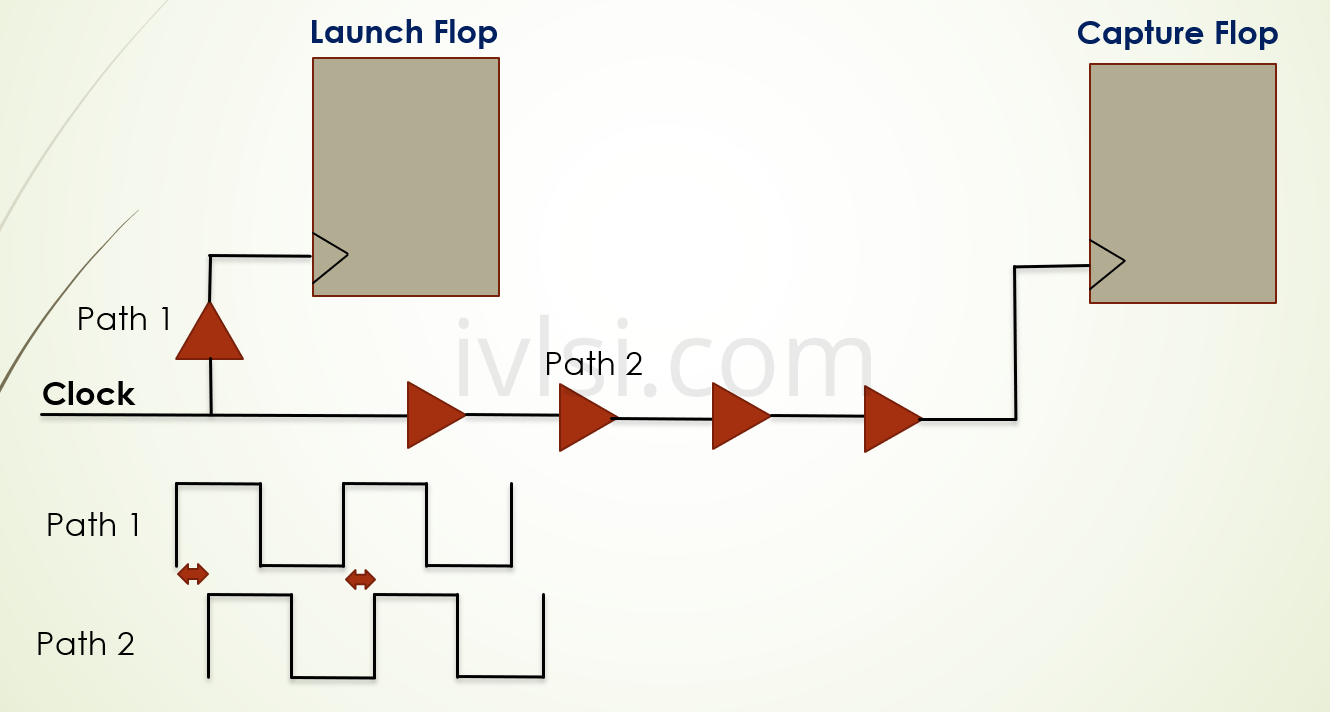

Clock Tree Example . Basically, clock gets evenly distributed throughout the design across all the sequential elements. clock tree synthesis (cts) is one of the most important stages in pnr. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. A clock tree is a clock distribution network within a system or hardware design. what is a clock tree? the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Key system clocking considerations include: Cts qor decides timing convergence & power. clock tree diagram example for an ultrasound scanner. In most of the ics. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. Basically, clock gets evenly distributed throughout the design across all the sequential elements.

from ivlsi.com

In most of the ics. clock tree synthesis (cts) is one of the most important stages in pnr. A clock tree is a clock distribution network within a system or hardware design. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Basically, clock gets evenly distributed throughout the design across all the sequential elements. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Key system clocking considerations include: what is a clock tree? Basically, clock gets evenly distributed throughout the design across all the sequential elements. Cts qor decides timing convergence & power.

Clock Tree Synthesis in VLSI Physical Design

Clock Tree Example cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. Basically, clock gets evenly distributed throughout the design across all the sequential elements. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Cts qor decides timing convergence & power. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. what is a clock tree? Basically, clock gets evenly distributed throughout the design across all the sequential elements. In most of the ics. A clock tree is a clock distribution network within a system or hardware design. clock tree synthesis (cts) is one of the most important stages in pnr. clock tree diagram example for an ultrasound scanner. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. Key system clocking considerations include:

From www.youtube.com

VLSI Physical Design Clock Tree Synthesis (CTS) YouTube Clock Tree Example clock tree synthesis (cts) is one of the most important stages in pnr. Key system clocking considerations include: the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree diagram example for an ultrasound scanner. In. Clock Tree Example.

From tech.tdzire.com

Clock Tree Guidances for better Clock Tree Synthesis TechnologyTdzire Clock Tree Example clock tree synthesis (cts) is one of the most important stages in pnr. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the. Clock Tree Example.

From www.researchgate.net

An example of ClockTree Wireand BufferSizing Problem. Download Clock Tree Example clock tree synthesis (cts) is one of the most important stages in pnr. In most of the ics. Basically, clock gets evenly distributed throughout the design across all the sequential elements. Cts qor decides timing convergence & power. clock tree diagram example for an ultrasound scanner. A clock tree is a clock distribution network within a system or. Clock Tree Example.

From slidetodoc.com

Introduction to Clock Tree Synthesis Clock Jargon Important Clock Tree Example A clock tree is a clock distribution network within a system or hardware design. Basically, clock gets evenly distributed throughout the design across all the sequential elements. Cts qor decides timing convergence & power. clock tree diagram example for an ultrasound scanner. cts (clock tree synthesis) is the process of connecting the clock from clock port to the. Clock Tree Example.

From www.analogictips.com

Clock Tree 101 Clock Tree Example Basically, clock gets evenly distributed throughout the design across all the sequential elements. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. clock tree diagram example for an ultrasound scanner. In most of the ics. what is a clock tree? the concept of clock tree. Clock Tree Example.

From www.vlsiguru.com

CLOCK_TREE_SYNTHESIS(pavan) vlsi Clock Tree Example In most of the ics. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. clock tree synthesis (cts) is one of the most important stages in pnr. clock tree diagram example for an ultrasound scanner. Cts qor decides timing convergence & power. Basically, clock gets evenly. Clock Tree Example.

From tech.tdzire.com

Clock Tree Guidances for better Clock Tree Synthesis TechnologyTdzire Clock Tree Example Basically, clock gets evenly distributed throughout the design across all the sequential elements. A clock tree is a clock distribution network within a system or hardware design. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. Key system clocking considerations include: In most of the ics. what. Clock Tree Example.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design Clock Tree Example In most of the ics. A clock tree is a clock distribution network within a system or hardware design. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. what is a clock tree? the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters. Clock Tree Example.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design Clock Tree Example Cts qor decides timing convergence & power. Key system clocking considerations include: In most of the ics. Basically, clock gets evenly distributed throughout the design across all the sequential elements. Basically, clock gets evenly distributed throughout the design across all the sequential elements. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock. Clock Tree Example.

From designbundles.net

Clock Tree of Life SVG, Tree cut file, Clock svg Clock Tree Example In most of the ics. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Basically, clock gets evenly distributed throughout the design across all the sequential elements. the concept of clock tree synthesis (cts) is the automatic. Clock Tree Example.

From physicaldesign-asic.blogspot.com

Clock Tree Synthesis Clock Tree Example clock tree diagram example for an ultrasound scanner. what is a clock tree? Basically, clock gets evenly distributed throughout the design across all the sequential elements. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. A clock tree is a clock distribution network within a system. Clock Tree Example.

From www.slideserve.com

PPT Chapter 9 High Speed Clock Management PowerPoint Presentation Clock Tree Example In most of the ics. Cts qor decides timing convergence & power. clock tree synthesis (cts) is one of the most important stages in pnr. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree. Clock Tree Example.

From www.slideserve.com

PPT ASIC BackEnd Design PowerPoint Presentation, free download ID Clock Tree Example Cts qor decides timing convergence & power. what is a clock tree? cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. In most of the ics. clock tree synthesis (cts) is one of the most important stages in pnr. A clock tree is a clock distribution. Clock Tree Example.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi Clock Tree Example the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Cts qor decides timing convergence & power. what is a clock tree? Basically, clock gets evenly distributed throughout the design across all the sequential elements. Key system clocking. Clock Tree Example.

From vlsiconceptsforyou.blogspot.com

VLSI Concepts Different Types of Clock Tree Structure Clock Tree Example Basically, clock gets evenly distributed throughout the design across all the sequential elements. Cts qor decides timing convergence & power. In most of the ics. Key system clocking considerations include: the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock. Clock Tree Example.

From www.slideserve.com

PPT Clock and Power PowerPoint Presentation, free download ID417576 Clock Tree Example A clock tree is a clock distribution network within a system or hardware design. Cts qor decides timing convergence & power. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Basically, clock gets evenly distributed throughout the design. Clock Tree Example.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Tree Example Cts qor decides timing convergence & power. Key system clocking considerations include: the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree synthesis (cts) is one of the most important stages in pnr. A clock tree. Clock Tree Example.

From www.youtube.com

Lecture on Clock Tree Synthesis Physical Design flow YouTube Clock Tree Example Key system clocking considerations include: In most of the ics. what is a clock tree? the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree diagram example for an ultrasound scanner. cts (clock tree. Clock Tree Example.

From www.researchgate.net

Clock network with toplevel tree driving a leaflevel mesh. The clock Clock Tree Example what is a clock tree? clock tree synthesis (cts) is one of the most important stages in pnr. A clock tree is a clock distribution network within a system or hardware design. Basically, clock gets evenly distributed throughout the design across all the sequential elements. In most of the ics. clock tree diagram example for an ultrasound. Clock Tree Example.

From www.researchgate.net

(PDF) An Efficient Clock Tree Synthesis Method in Physical Design Clock Tree Example the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree synthesis (cts) is one of the most important stages in pnr. Basically, clock gets evenly distributed throughout the design across all the sequential elements. A clock. Clock Tree Example.

From www.slideserve.com

PPT ASIC BackEnd Design PowerPoint Presentation, free download ID Clock Tree Example what is a clock tree? cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Cts qor. Clock Tree Example.

From www.researchgate.net

Graphic representation of the clock tree structure Download Clock Tree Example In most of the ics. Key system clocking considerations include: clock tree synthesis (cts) is one of the most important stages in pnr. Basically, clock gets evenly distributed throughout the design across all the sequential elements. what is a clock tree? the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock. Clock Tree Example.

From www.slideserve.com

PPT CLOCK DISTRIBUTION PowerPoint Presentation, free download ID Clock Tree Example the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Basically, clock gets evenly distributed throughout the design across all the sequential elements. A clock tree is a clock distribution network within a system or hardware design. the. Clock Tree Example.

From www.slideserve.com

PPT CLOCK DISTRIBUTION PowerPoint Presentation, free download ID Clock Tree Example the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Key system clocking considerations include: In most of the ics. what is a clock tree? clock tree diagram example for an ultrasound scanner. cts (clock tree. Clock Tree Example.

From www.slideserve.com

PPT Skew Management of NBTI Impacted Gated Clock Trees PowerPoint Clock Tree Example the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Cts qor decides timing convergence & power. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design. Clock Tree Example.

From www.slideserve.com

PPT Clock Network Synthesis PowerPoint Presentation, free download Clock Tree Example clock tree diagram example for an ultrasound scanner. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree synthesis (cts) is one of the most important stages in pnr. Basically, clock gets evenly distributed throughout. Clock Tree Example.

From vorasaumil.wixsite.com

Clock Tree Synthesis Part 3 Clock Structures, its Implementation Clock Tree Example A clock tree is a clock distribution network within a system or hardware design. Key system clocking considerations include: Basically, clock gets evenly distributed throughout the design across all the sequential elements. Cts qor decides timing convergence & power. what is a clock tree? the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along. Clock Tree Example.

From www.slideserve.com

PPT Zero Skew Clock tree Implementation PowerPoint Presentation, free Clock Tree Example Cts qor decides timing convergence & power. Key system clocking considerations include: clock tree synthesis (cts) is one of the most important stages in pnr. cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. In most of the ics. the concept of clock tree synthesis (cts). Clock Tree Example.

From www.researchgate.net

4 (a) Nonequidistant clock tree (b) Equidistant clock tree. Download Clock Tree Example Key system clocking considerations include: the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock tree diagram example for an ultrasound scanner. A clock tree is a clock distribution network within a system or hardware design. . Clock Tree Example.

From www.slideserve.com

PPT Power and Slewaware Clock Network Design for ThroughSiliconVia Clock Tree Example what is a clock tree? clock tree diagram example for an ultrasound scanner. Basically, clock gets evenly distributed throughout the design across all the sequential elements. clock tree synthesis (cts) is one of the most important stages in pnr. In most of the ics. the concept of clock tree synthesis (cts) is the automatic insertion of. Clock Tree Example.

From www.vlsisystemdesign.com

Selective NonDefault Rules Based Clock Tree Synthesis using open Clock Tree Example Basically, clock gets evenly distributed throughout the design across all the sequential elements. A clock tree is a clock distribution network within a system or hardware design. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. clock. Clock Tree Example.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi Clock Tree Example the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. Cts qor decides timing convergence & power. Basically, clock gets evenly distributed throughout the design across all the sequential elements. cts (clock tree synthesis) is the process of. Clock Tree Example.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design Clock Tree Example Key system clocking considerations include: what is a clock tree? cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. In most of the ics. A clock tree is a clock distribution network within a system or hardware design. clock tree synthesis (cts) is one of the. Clock Tree Example.

From www.slideserve.com

PPT Clock Network Synthesis PowerPoint Presentation, free download Clock Tree Example cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential. clock tree synthesis (cts) is one of the most important stages in pnr. A clock tree is a clock distribution network within a system or hardware design. Cts qor decides timing convergence & power. Key system clocking considerations. Clock Tree Example.

From www.citronshop.com

woodenwallclocktrees Citron Clock Tree Example A clock tree is a clock distribution network within a system or hardware design. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along the clock paths of the asic design to balance the clock delay to all clock inputs. the concept of clock tree synthesis (cts) is the automatic insertion of buffers/inverters along. Clock Tree Example.