Glitch Filter Fpga . Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they.

from www.youtube.com

we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they.

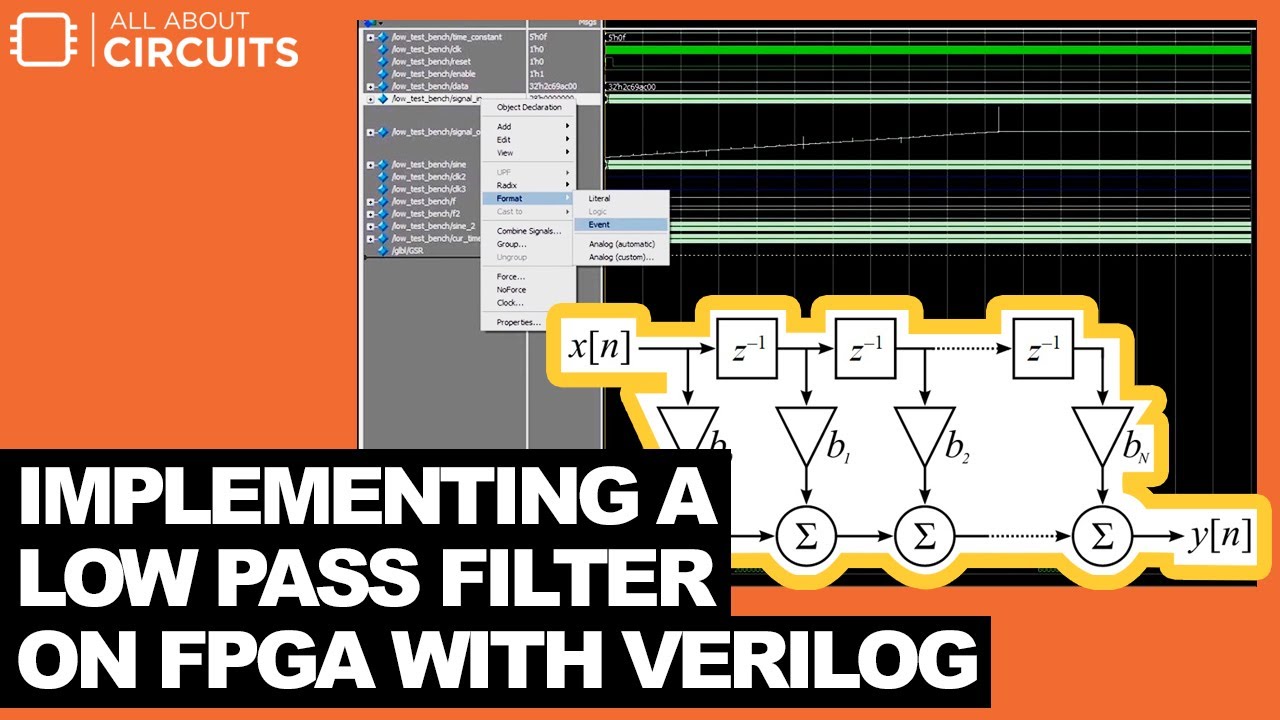

Implementing a low pass filter on FPGA with verilog YouTube

Glitch Filter Fpga \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they.

From laptrinhx.com

Using an FPGA to Glitch the Olimex LPCP1343 LaptrinhX Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering. Glitch Filter Fpga.

From www.youtube.com

Electronics Glitch filter implementation YouTube Glitch Filter Fpga Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient to remove metastability within your desired. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Dynamic power minimization in fpgas through edge alignment and glitch filtering this. Glitch Filter Fpga.

From www.researchgate.net

(a) Highpass filter structure implemented in the FPGA for 4096 Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. . Glitch Filter Fpga.

From e2e.ti.com

LM5060Q1 Glitch on nPGD line when asserting EN line. Power Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Dynamic power minimization in fpgas through. Glitch Filter Fpga.

From laptrinhx.com

Using an FPGA to Glitch the Olimex LPCP1343 LaptrinhX Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause. Glitch Filter Fpga.

From www.element14.com

Gradient Filter implementation on an FPGA Par... element14 FPGA Group Glitch Filter Fpga Assuming the double flop is sufficient to remove metastability within your desired. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. \$\begingroup\$ glitch filters are often useful for determining which types of. Glitch Filter Fpga.

From valentfx.com

Gradient Filter implementation on an FPGA Part 1 Interfacing an FPGA Glitch Filter Fpga \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient. Glitch Filter Fpga.

From www.youtube.com

FPGA and DSP ep. 2 Implementing a folded FIR filter on FPGA YouTube Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate. Glitch Filter Fpga.

From www.nxfee.com

FIR Filter Design based on FPGA Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause. Glitch Filter Fpga.

From tigerente-lab.com

Implementing a FIR filter on FPGA Electronic Design Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient to remove metastability within your. Glitch Filter Fpga.

From allaboutfpga.com

VHDL Code for Debounce Circuit in FPGA Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient to remove metastability within your. Glitch Filter Fpga.

From nl.mathworks.com

Programmable FIR Filter for FPGA MATLAB & Simulink MathWorks Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate. Glitch Filter Fpga.

From e2e.ti.com

LM5060Q1 Glitch on nPGD line when asserting EN line. Power Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches. Glitch Filter Fpga.

From www.slideserve.com

PPT Energy Optimization Techniques FPGA Glitch Reduction PowerPoint Glitch Filter Fpga Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. . Glitch Filter Fpga.

From www.slideserve.com

PPT Energy Optimization Techniques FPGA Glitch Reduction PowerPoint Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient to remove metastability within your desired. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section. Glitch Filter Fpga.

From www.pantechsolutions.net

FPGA based Median Filter Implementation using Spartan3 FPGA Image Glitch Filter Fpga \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. . Glitch Filter Fpga.

From www.slideserve.com

PPT Energy Optimization Techniques FPGA Glitch Reduction PowerPoint Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Dynamic power minimization in fpgas through. Glitch Filter Fpga.

From www.youtube.com

Implementing a low pass filter on FPGA with verilog YouTube Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Assuming the double flop is sufficient to remove metastability within your desired. . Glitch Filter Fpga.

From www.knitronics.com

DSP for FPGA Custom AXI4Stream FIR filter IP in Vivado — Knitronics Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch. Glitch Filter Fpga.

From www.embedded.com

Asynchronous reset synchronization and distribution Special cases Glitch Filter Fpga \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering. Glitch Filter Fpga.

From www.semanticscholar.org

FPGA Implementation of FIR based Decimation Filter Structure for WiMAX Glitch Filter Fpga Assuming the double flop is sufficient to remove metastability within your desired. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section. Glitch Filter Fpga.

From www.pantechsolutions.net

FPGA based Median Filter Implementation using Spartan3 FPGA Image Glitch Filter Fpga Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. . Glitch Filter Fpga.

From www.semanticscholar.org

Figure 3 from Design and FPGA implementation of sequential digital 7 Glitch Filter Fpga we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Intel fpga recommends that you use the glitch filtering feature. Glitch Filter Fpga.

From www.semanticscholar.org

Figure 2 from Voltage Glitch Filter and Detector with SelfChecking Glitch Filter Fpga Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. \$\begingroup\$ glitch filters are often useful for determining which types. Glitch Filter Fpga.

From www.pantechsolutions.net

FPGA based Median Filter Implementation using Spartan3 FPGA Image Glitch Filter Fpga \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability. Glitch Filter Fpga.

From www.youtube.com

Xilinx HLS 2 FPGA FIR Filter Design in C in 30 minutes (Vivado High Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches. Glitch Filter Fpga.

From abdushshakurblog.wordpress.com

Using an FPGA to Glitch the Olimex LPCP1343 Hacking Tricks Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types. Glitch Filter Fpga.

From www.studypool.com

SOLUTION Fpga 11 sequence detector fir iir filter Studypool Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Assuming the double flop is sufficient to remove metastability within your desired. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches. Glitch Filter Fpga.

From saw235.github.io

Realtime Image Filtering using FPGA Saw's Blog Glitch Filter Fpga Assuming the double flop is sufficient to remove metastability within your desired. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed. Glitch Filter Fpga.

From www.studypool.com

SOLUTION Fpga 11 sequence detector fir iir filter Studypool Glitch Filter Fpga Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques. Glitch Filter Fpga.

From www.slideserve.com

PPT Reducing Energy in FPGA Multipliers Through Glitch Reduction Glitch Filter Fpga Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. . Glitch Filter Fpga.

From www.slideserve.com

PPT Energy Optimization Techniques FPGA Glitch Reduction PowerPoint Glitch Filter Fpga Assuming the double flop is sufficient to remove metastability within your desired. Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section. Glitch Filter Fpga.

From www.pantechsolutions.net

FPGA based Median Filter Implementation using Spartan3 FPGA Image Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Assuming the double flop is sufficient to remove metastability. Glitch Filter Fpga.

From www.youtube.com

FPGA FIR Filter Circuit Architecture and VHDL Design YouTube Glitch Filter Fpga \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. Assuming the double flop is sufficient to remove metastability within your desired. we provide an overview of glitch power in fpgas and previous techniques proposed to reduce glitches in section 2. Intel fpga recommends that you use the glitch filtering feature. Glitch Filter Fpga.

From www.hackster.io

DSP for FPGA Simple FIR Filter in Verilog Hackster.io Glitch Filter Fpga Dynamic power minimization in fpgas through edge alignment and glitch filtering this paper. Assuming the double flop is sufficient to remove metastability within your desired. Intel fpga recommends that you use the glitch filtering feature to obtain the most accurate power. \$\begingroup\$ glitch filters are often useful for determining which types of inputs can cause metastability, but they. . Glitch Filter Fpga.