Case Vs If Vhdl . While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. When the number of options greater than two we can use the vhdl “elsif” clause. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. Last time, in the third installment of vhdl we discussed logic gates and adders. In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version:

from www.youtube.com

Last time, in the third installment of vhdl we discussed logic gates and adders. While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. When the number of options greater than two we can use the vhdl “elsif” clause. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple.

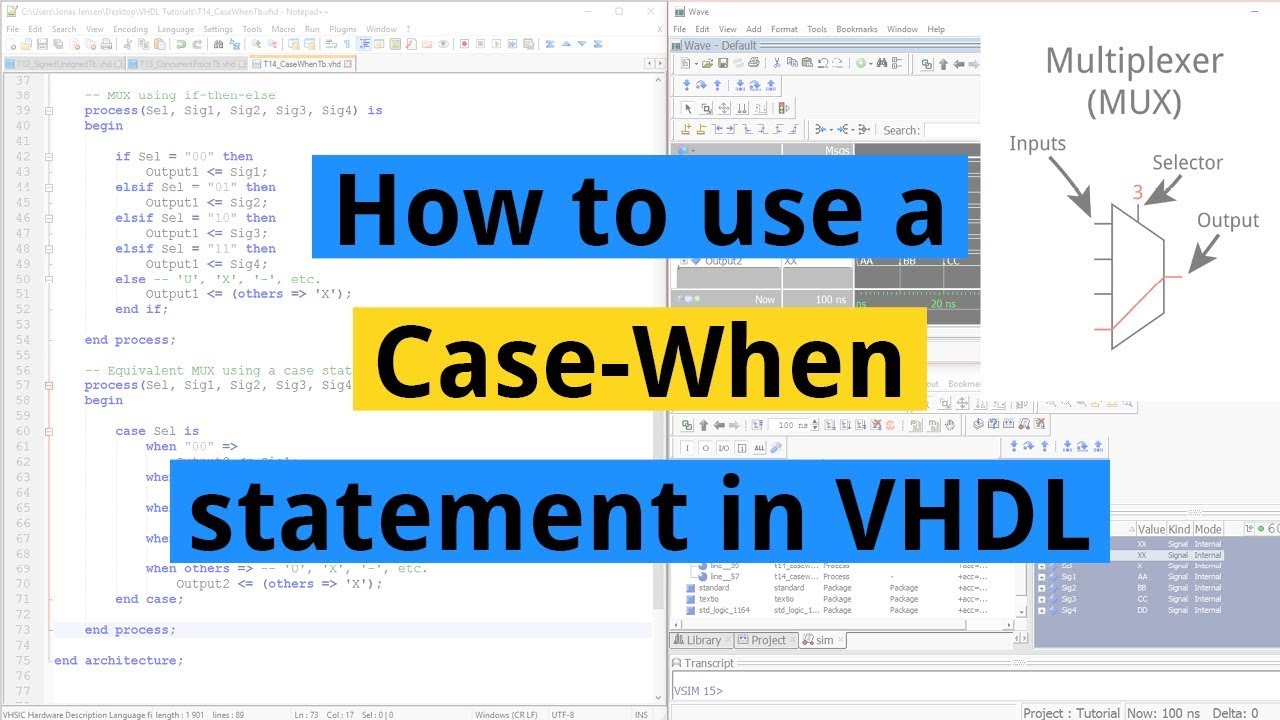

How to use a CaseWhen statement in VHDL YouTube

Case Vs If Vhdl In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: When the number of options greater than two we can use the vhdl “elsif” clause. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. Last time, in the third installment of vhdl we discussed logic gates and adders. In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement.

From www.slideserve.com

PPT FPGA ja VHDL PowerPoint Presentation, free download ID4384942 Case Vs If Vhdl Last time, in the third installment of vhdl we discussed logic gates and adders. When the number of options greater than two we can use the vhdl “elsif” clause. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. In case of multiple options, vhdl provides a. Case Vs If Vhdl.

From www.youtube.com

How to write 41mux using case statement. in VHDL behavioral modeling Case Vs If Vhdl Last time, in the third installment of vhdl we discussed logic gates and adders. When the number of options greater than two we can use the vhdl “elsif” clause. While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In case. Case Vs If Vhdl.

From www.mdpi.com

Designs Free FullText Automated Test Case Generation for Digital Case Vs If Vhdl In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. While the priority of each branch is set by means of the query’s order in the if. Case Vs If Vhdl.

From www.chegg.com

Solved 1. Using the VHDL CASE statement write behavior Case Vs If Vhdl In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. When the number of options greater than two we can use the vhdl “elsif” clause. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to. Case Vs If Vhdl.

From present5.com

Chapter 4 Combinational Logic Circuits Chapter Case Vs If Vhdl When the number of options greater than two we can use the vhdl “elsif” clause. Last time, in the third installment of vhdl we discussed logic gates and adders. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. While the priority of each branch is set. Case Vs If Vhdl.

From www.slideserve.com

PPT An Introduction to Verilog Transitioning from VHDL PowerPoint Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: Last time, in the third installment of vhdl we discussed logic gates and. Case Vs If Vhdl.

From jjmk.dk

If Then Else Case Vs If Vhdl In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: When the number of options greater than two we can use the vhdl “elsif” clause. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. Last time, in the. Case Vs If Vhdl.

From surf-vhdl.com

IFTHENELSE statement in VHDL SurfVHDL Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. The difference is one is a sequential statement. Case Vs If Vhdl.

From firsteda.com

Blog Achieving Better Coverage with VHDL Part 1 FirstEDA Case Vs If Vhdl The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In general, when using a process to describe a combinational circuit,. Case Vs If Vhdl.

From www.youtube.com

VHDL Example Episode 01 Decoder Using "IF" / "Case" / "Logic Gates Case Vs If Vhdl In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential. Case Vs If Vhdl.

From surf-vhdl.com

VHDL CASE statement SurfVHDL Case Vs If Vhdl Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. Last time, in the third installment of vhdl we discussed logic gates and adders. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: When the number of options. Case Vs If Vhdl.

From www.youtube.com

How to use conditional statements in VHDL IfThenElsifElse YouTube Case Vs If Vhdl In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. When the number of options greater than two we can use the vhdl. Case Vs If Vhdl.

From www.jjmk.dk

Case Is Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: In general, when using a process to describe a combinational circuit, we need. Case Vs If Vhdl.

From slideplayer.com

CPRE 583 Reconfigurable Computing ppt download Case Vs If Vhdl The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity. Case Vs If Vhdl.

From www.youtube.com

VHDL Course session 12 (Chapter 5 case statements and loops) YouTube Case Vs If Vhdl When the number of options greater than two we can use the vhdl “elsif” clause. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. While the priority of each branch is set by means of the query’s order in the if case, all branches are equal. Case Vs If Vhdl.

From www.youtube.com

lesson 37 Sequence Detector in VHDL How to describe state diagram in Case Vs If Vhdl When the number of options greater than two we can use the vhdl “elsif” clause. While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In general, when using a process to describe a combinational circuit, we need to include all. Case Vs If Vhdl.

From www.allaboutcircuits.com

Sequential VHDL If and Case Statements Technical Articles Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: The difference is one is a sequential statement and must occur inside a. Case Vs If Vhdl.

From surf-vhdl.com

VHDL CASE statement SurfVHDL Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. Case is looking at a single variable and deciding cases for. Case Vs If Vhdl.

From www.youtube.com

IF and CASE condition in VHDL VHDL Basic Tutorial Part 3 YouTube Case Vs If Vhdl Last time, in the third installment of vhdl we discussed logic gates and adders. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. In case of. Case Vs If Vhdl.

From www.youtube.com

What is a VHDL process? (Part 1) YouTube Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. Last time, in the third installment of vhdl we discussed logic gates and adders. The difference is one is a sequential statement and must occur inside a process, while the other. Case Vs If Vhdl.

From www.youtube.com

VHDL Lab 4 If/then/else and Case Part 1 YouTube Case Vs If Vhdl When the number of options greater than two we can use the vhdl “elsif” clause. Last time, in the third installment of vhdl we discussed logic gates and adders. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. While the priority of each branch is set by means of. Case Vs If Vhdl.

From surf-vhdl.com

VHDL CASE statement SurfVHDL Case Vs If Vhdl When the number of options greater than two we can use the vhdl “elsif” clause. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. Last time, in the. Case Vs If Vhdl.

From englishstudypage.com

"in case" vs "if" in English English Study Page Case Vs If Vhdl In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. Last time, in the third installment of vhdl we discussed logic gates and adders. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. When the number. Case Vs If Vhdl.

From www.slideserve.com

PPT Chapter 8 PowerPoint Presentation, free download ID1749004 Case Vs If Vhdl Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. In general, when using a process to describe a combinational circuit, we need to include all of. Case Vs If Vhdl.

From www.researchgate.net

6 Hardware implementation of VHDL if and case constructs. Download Case Vs If Vhdl Last time, in the third installment of vhdl we discussed logic gates and adders. While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. Case is looking at a single variable and deciding cases for each possible outcome while an if. Case Vs If Vhdl.

From www.youtube.com

VHDL BASIC Tutorial CASE Statement YouTube Case Vs If Vhdl Last time, in the third installment of vhdl we discussed logic gates and adders. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case. Case Vs If Vhdl.

From www.youtube.com

VHDL Lab 4 If/then/else and Case Part 3 YouTube Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. When the number of options greater than two we can use the vhdl “elsif” clause. In general, when using a process to describe a combinational circuit, we need to include all. Case Vs If Vhdl.

From www.youtube.com

VHDL Commandes séquentielles (if, case, loop, while, for) YouTube Case Vs If Vhdl In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: Last time, in the third installment of vhdl we discussed logic gates and adders. When the number of options greater than two we can use the vhdl “elsif” clause. The difference is one is a sequential statement and must occur inside a. Case Vs If Vhdl.

From www.slideserve.com

PPT VHDL Tutorial PowerPoint Presentation, free download ID228079 Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. Last time, in the third installment of vhdl we discussed logic gates and adders. Case is looking at a single variable and deciding cases for each possible outcome while an if. Case Vs If Vhdl.

From www.researchgate.net

(a) A VHDL " case " statement. (b) DAG representation. Download Case Vs If Vhdl The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. Last time, in the third installment of vhdl we discussed logic gates and adders. While the priority. Case Vs If Vhdl.

From www.slideserve.com

PPT VHDL Tutorial PowerPoint Presentation, free download ID228079 Case Vs If Vhdl The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. While the priority of each branch is set by means of the query’s order in the if. Case Vs If Vhdl.

From www.slideserve.com

PPT Miscellaneous PowerPoint Presentation, free download ID3354992 Case Vs If Vhdl Case is looking at a single variable and deciding cases for each possible outcome while an if statement can be applied to multiple. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: When the number of options greater than two we can use the vhdl “elsif” clause. In general, when using. Case Vs If Vhdl.

From surf-vhdl.com

IFTHENELSE statement in VHDL SurfVHDL Case Vs If Vhdl In general, when using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list. When the number of options greater than two we can use the vhdl “elsif” clause. In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: Case is looking at. Case Vs If Vhdl.

From www.youtube.com

How to use a CaseWhen statement in VHDL YouTube Case Vs If Vhdl In case of multiple options, vhdl provides a more powerful statement both in the concurrent and sequential version: While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. In general, when using a process to describe a combinational circuit, we need. Case Vs If Vhdl.

From slideplayer.com

CPRE 583 Reconfigurable Computing ppt download Case Vs If Vhdl While the priority of each branch is set by means of the query’s order in the if case, all branches are equal in priority when using a case statement. The difference is one is a sequential statement and must occur inside a process, while the other is a concurrent. In general, when using a process to describe a combinational circuit,. Case Vs If Vhdl.