Design Xor Gate Using 2 1 Mux . What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. Generate rtl schematic and simulate the 2:1 mux using testbench. First multiplexer will act as not gate which will provide. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. And, or, xor, nand, and nor. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. There is an alternate way to describe xor operation, which one can observe based. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic.

from www.youtube.com

What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. And, or, xor, nand, and nor. There is an alternate way to describe xor operation, which one can observe based. First multiplexer will act as not gate which will provide. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. Generate rtl schematic and simulate the 2:1 mux using testbench. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input.

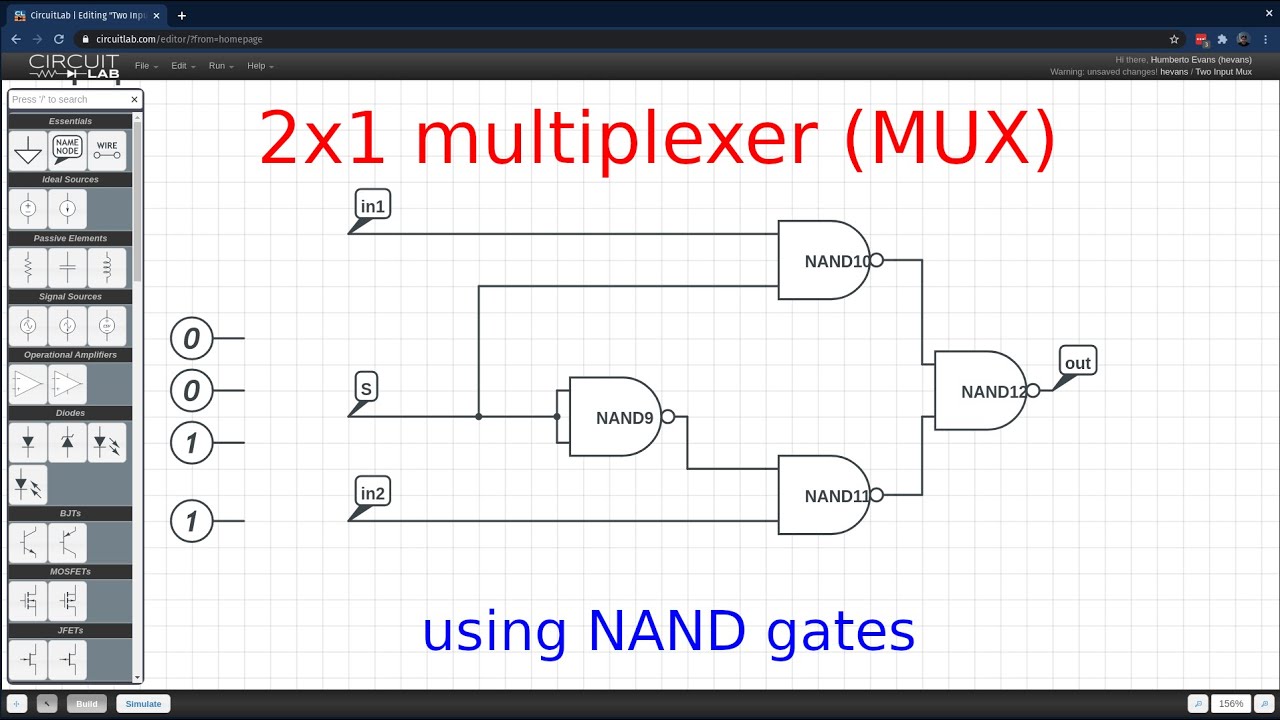

2x1 MUX What's a Multiplexer? (Built and Explained from 3 NAND Gates

Design Xor Gate Using 2 1 Mux On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). There is an alternate way to describe xor operation, which one can observe based. We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. First multiplexer will act as not gate which will provide. And, or, xor, nand, and nor. Generate rtl schematic and simulate the 2:1 mux using testbench. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input.

From manuallistcantabank.z21.web.core.windows.net

Xor Gate Diagram Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. There is. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Implementation of Basic Logic Gates(AND,OR,NOT,NAND,XOR,XNOR) Using 21 Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. First multiplexer will act as not gate which will provide. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. And, or, xor, nand, and nor. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). On. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Implementation of XOR gate using 21 mux YouTube Design Xor Gate Using 2 1 Mux Design the 2:1 mux in verilog with all abstraction layers (modeling styles). We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. First multiplexer will act as not gate which will provide. And,. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

2x1 MUX What's a Multiplexer? (Built and Explained from 3 NAND Gates Design Xor Gate Using 2 1 Mux What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. We often use symbol or symbol ‘+’ with circle. Design Xor Gate Using 2 1 Mux.

From www.researchgate.net

Schematic of 21 MUX using CMOS Logic in DSCH2 Download Scientific Design Xor Gate Using 2 1 Mux What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. There is an alternate way to describe xor operation, which one can observe based. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. As we know, a 2:1 multiplexer selects between two inputs depending upon the. Design Xor Gate Using 2 1 Mux.

From circuitfixmatthew.z6.web.core.windows.net

Logic Diagram Of 2x1 Mux Design Xor Gate Using 2 1 Mux Design the 2:1 mux in verilog with all abstraction layers (modeling styles). On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. First multiplexer will act as not gate which will provide. There is. Design Xor Gate Using 2 1 Mux.

From www.chegg.com

Solved A) Design XOR And XNOR Gate Using One 2 1 MUX Con... Design Xor Gate Using 2 1 Mux What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. On an fpga using fewer resources is better and. Design Xor Gate Using 2 1 Mux.

From www.gsnetwork.com

XOR Gate, Exclusive OR Gate Built with Transistors Design Xor Gate Using 2 1 Mux And, or, xor, nand, and nor. Generate rtl schematic and simulate the 2:1 mux using testbench. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. There is an alternate way to describe xor operation, which one can observe based. First multiplexer will act as not gate which will. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

OR gate using 21 MUX vhdl (SMS) YouTube Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). And, or, xor, nand, and nor. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. We often. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

CMOS Logic Circuit Design for XOR and XNOR Gate YouTube Design Xor Gate Using 2 1 Mux Design the 2:1 mux in verilog with all abstraction layers (modeling styles). On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. And, or, xor, nand, and nor. What's the smallest combination of xor. Design Xor Gate Using 2 1 Mux.

From design.udlvirtual.edu.pe

What Is Xor Gates Design Talk Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. There is an alternate way to describe xor operation, which one can observe based. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). First multiplexer will act as not gate which will provide. On an fpga using fewer resources is better and usually an fpga consists of. Design Xor Gate Using 2 1 Mux.

From www.chegg.com

2 Design an INVERTER, AND gate, OR gate, XOR gate, Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. As we know, a 2:1 multiplexer selects between two inputs. Design Xor Gate Using 2 1 Mux.

From www.176iot.com

2 1 Mux Circuit Diagram IOT Wiring Diagram Design Xor Gate Using 2 1 Mux First multiplexer will act as not gate which will provide. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). There is an alternate way to describe xor operation, which one can observe based. And, or, xor, nand, and nor. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. We often use symbol or symbol. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Implement NAND gate using 21MUX how to implement NAND gate using Design Xor Gate Using 2 1 Mux We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. There is an alternate way to describe xor. Design Xor Gate Using 2 1 Mux.

From circuitlibverla.z21.web.core.windows.net

Circuit Diagram For 2x1 Multiplexer Design Xor Gate Using 2 1 Mux First multiplexer will act as not gate which will provide. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. We often use symbol or symbol ‘+’ with circle around it. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Microwind Implementation of MUX Using TRANSMISSION GATES YouTube Design Xor Gate Using 2 1 Mux As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. There is an alternate way to describe xor operation, which one can observe based. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a. Design Xor Gate Using 2 1 Mux.

From courses.cs.washington.edu

Mux implementation using logic gates Design Xor Gate Using 2 1 Mux As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. Generate rtl schematic and simulate the 2:1 mux using testbench. First multiplexer will act as not gate which will provide. We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. Design the 2:1 mux in verilog. Design Xor Gate Using 2 1 Mux.

From arledgespearknigh91.blogspot.com

Design an Xor Gate Using a 4 1 Mux Arledge Spearknigh91 Design Xor Gate Using 2 1 Mux Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic.. Design Xor Gate Using 2 1 Mux.

From copyprogramming.com

How a 21 multiplexer (MUX) work? Design Xor Gate Using 2 1 Mux And, or, xor, nand, and nor. Generate rtl schematic and simulate the 2:1 mux using testbench. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Design XOR gate using Structural Modeling VHDL Language in XILINX All Design Xor Gate Using 2 1 Mux On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. Generate rtl schematic. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

OR gate using 21Mux / realise OR gate using MUX YouTube Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. First multiplexer will act as not gate which will provide. And, or, xor, nand,. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Design XOR gate using 21 MUX implement XOR gate using MUX how to Design Xor Gate Using 2 1 Mux First multiplexer will act as not gate which will provide. And, or, xor, nand, and nor. We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. There is an alternate way to describe xor operation, which one can observe based. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. On an. Design Xor Gate Using 2 1 Mux.

From www.vrogue.co

Xor Gate Circuit Diagram Using Transistor vrogue.co Design Xor Gate Using 2 1 Mux What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. Generate rtl schematic and simulate the 2:1 mux using testbench. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. And, or, xor, nand, and nor. Implementation of nand, nor, xor. Design Xor Gate Using 2 1 Mux.

From www.chegg.com

1. Create the layout for a 2 input XOR gate using Design Xor Gate Using 2 1 Mux And, or, xor, nand, and nor. We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic). Design Xor Gate Using 2 1 Mux.

From www.youtube.com

MIcrowind Implementation of 21 MUX using Logic gates YouTube Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. First multiplexer will act as not gate which will provide. We often use symbol. Design Xor Gate Using 2 1 Mux.

From www.youtube.com

Logic Gates using Multiplexer How to implement a logic gate using the Design Xor Gate Using 2 1 Mux There is an alternate way to describe xor operation, which one can observe based. First multiplexer will act as not gate which will provide. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain. Design Xor Gate Using 2 1 Mux.

From siliconvlsi.com

21 MUX Using NAND Siliconvlsi Design Xor Gate Using 2 1 Mux First multiplexer will act as not gate which will provide. Generate rtl schematic and simulate the 2:1 mux using testbench. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. There is an alternate. Design Xor Gate Using 2 1 Mux.

From www.engineersgarage.com

VHDL Tutorial 5 Design, simulate and verify NAND, NOR, XOR and XNOR Design Xor Gate Using 2 1 Mux We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. What's the smallest combination of xor and/or maj. Design Xor Gate Using 2 1 Mux.

From circuitenginedundee.z13.web.core.windows.net

Multiplexer Circuit Diagram With Gates Design Xor Gate Using 2 1 Mux We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). What's the smallest combination of xor and/or maj gates (with inversions (not) possible at. Design Xor Gate Using 2 1 Mux.

From circuithyunjin3188309e.z22.web.core.windows.net

Implement Full Adder Using 21 Mux Design Xor Gate Using 2 1 Mux On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like a mux combined with some other logic) and a memory element to form a cell or logic. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). As we know, a 2:1 multiplexer selects between two inputs depending upon. Design Xor Gate Using 2 1 Mux.

From www.slideserve.com

PPT Multiplexers DeMultiplexers XOR gates PowerPoint Presentation Design Xor Gate Using 2 1 Mux And, or, xor, nand, and nor. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. There is an alternate way to describe xor operation, which one can observe based. On an fpga using fewer resources is better and usually an fpga consists of a simple logic chain (like. Design Xor Gate Using 2 1 Mux.

From www.chegg.com

Solved a. Using a 21 mux, create an inverter (a NOT gate) Design Xor Gate Using 2 1 Mux We often use symbol or symbol ‘+’ with circle around it to represent the xor operation. As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. First multiplexer will act as not gate which will provide. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. Design the 2:1 mux. Design Xor Gate Using 2 1 Mux.

From ar.inspiredpencil.com

2x1 Mux Schematic Design Xor Gate Using 2 1 Mux As we know, a 2:1 multiplexer selects between two inputs depending upon the value of its select input. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. First multiplexer will act as not gate which will provide. Generate rtl schematic and simulate the 2:1 mux using testbench. There is an alternate way to describe xor operation, which. Design Xor Gate Using 2 1 Mux.

From guidefixelois.z13.web.core.windows.net

Design 4x1 Mux Using 2x1 Mux Design Xor Gate Using 2 1 Mux Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. And, or, xor, nand, and nor. First multiplexer will act as not gate which will provide. What's the smallest combination of xor and/or maj gates (with inversions (not) possible at any point) that has the same truth. On an fpga using fewer resources is better and usually an. Design Xor Gate Using 2 1 Mux.

From projectiot123.com

Introduction to XOR Gate Design Xor Gate Using 2 1 Mux Generate rtl schematic and simulate the 2:1 mux using testbench. And, or, xor, nand, and nor. Implementation of nand, nor, xor and xnor gates requires two 2:1 mux. Design the 2:1 mux in verilog with all abstraction layers (modeling styles). First multiplexer will act as not gate which will provide. On an fpga using fewer resources is better and usually. Design Xor Gate Using 2 1 Mux.