Clock Cycles Per Instruction X86 . How many cycles an operation spends in the alu? What do you mean by latency? The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. The average number of core clock cycles per instruction for a series of independent instructions of the same. The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The amd k10 has a wider bus between the l1 instruction cache You might find this table useful:. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. °one way to define clock cycles:

from www.slideserve.com

The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). The average number of core clock cycles per instruction for a series of independent instructions of the same. °one way to define clock cycles: In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. The amd k10 has a wider bus between the l1 instruction cache What do you mean by latency? The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. How many cycles an operation spends in the alu?

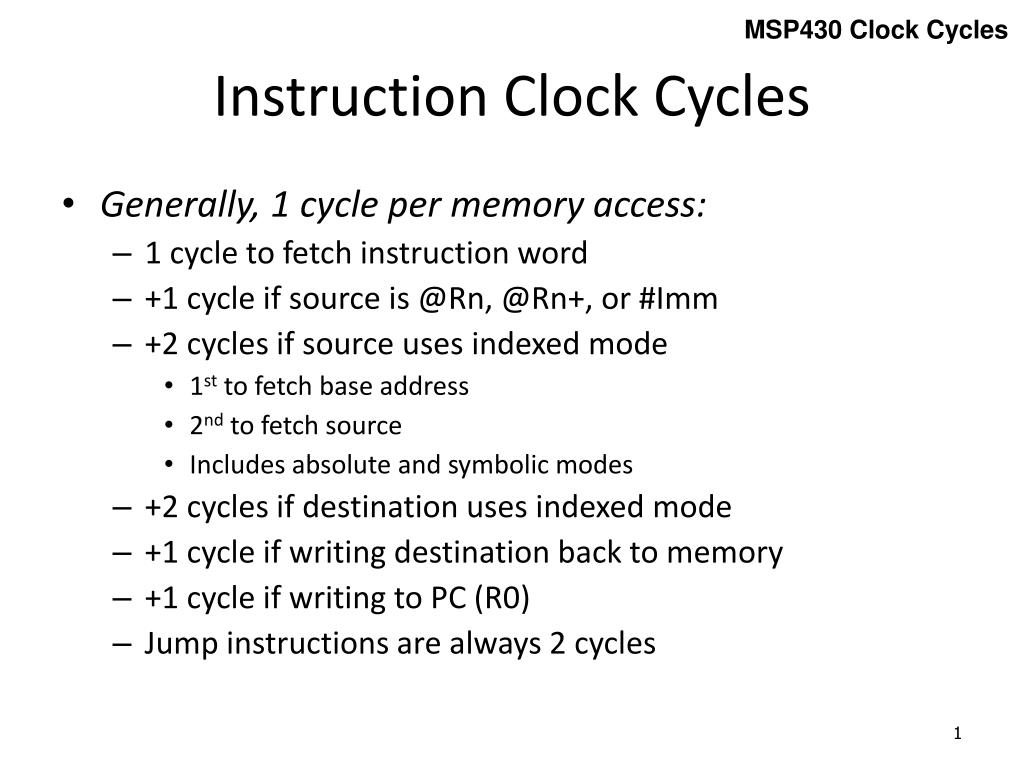

PPT Instruction Clock Cycles PowerPoint Presentation, free download ID4418310

Clock Cycles Per Instruction X86 °one way to define clock cycles: The average number of core clock cycles per instruction for a series of independent instructions of the same. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. You might find this table useful:. °one way to define clock cycles: The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. How many cycles an operation spends in the alu? What do you mean by latency? The amd k10 has a wider bus between the l1 instruction cache

From www.slideserve.com

PPT Two Notions of “Performance” PowerPoint Presentation, free download ID4604420 Clock Cycles Per Instruction X86 The average number of core clock cycles per instruction for a series of independent instructions of the same. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The amd k10 has a wider bus between the l1 instruction cache What do you mean by latency? Clock cycles for program = instructions. Clock Cycles Per Instruction X86.

From studylib.net

CPU Performance Evaluation Cycles Per Instruction (CPI) Clock Cycles Per Instruction X86 The average number of core clock cycles per instruction for a series of independent instructions of the same. The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. How many cycles an operation spends in the alu? You might find this table useful:. °one way to define clock cycles: The amd k10. Clock Cycles Per Instruction X86.

From 9to5answer.com

[Solved] How to count clock cycles with RDTSC in GCC x86? 9to5Answer Clock Cycles Per Instruction X86 In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. °one way to define clock cycles: The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). You might find this table useful:. The amd k10 has a wider bus. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. How many cycles an operation spends in the alu? In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. °one way to define clock cycles: The amd k10 has a wider bus. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT Chapter 4 PowerPoint Presentation, free download ID4745231 Clock Cycles Per Instruction X86 The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. What do you mean by latency? °one way to define clock cycles: The amd k10 has a wider bus. Clock Cycles Per Instruction X86.

From www.cgdirector.com

What is a CPU's IPC? Instructions per Cycle explained Clock Cycles Per Instruction X86 The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute,. Clock Cycles Per Instruction X86.

From www.chegg.com

Solved Evaluate the CPI(clock cycles per Instruction ), MIPS Clock Cycles Per Instruction X86 The average number of core clock cycles per instruction for a series of independent instructions of the same. The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). The amd k10 has a wider bus between the l1 instruction cache What do you mean by latency? You. Clock Cycles Per Instruction X86.

From calculator.academy

Clock Cycles Per Instruction Calculator Calculator Academy Clock Cycles Per Instruction X86 The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. °one way to define clock cycles: The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). The term clock cycles per instruction, which is the average number of clock. Clock Cycles Per Instruction X86.

From gallcolleenvirh.blogspot.com

Clock Cycle In Computer Architecture Concepts Of Pipelining Computer Architecture The Clock Cycles Per Instruction X86 The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. °one way to define clock cycles: The average number of core clock cycles per instruction for a series of. Clock Cycles Per Instruction X86.

From slideplayer.com

Fundamentals of Computer Design ppt download Clock Cycles Per Instruction X86 The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. What do you mean by latency? In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. You might find this table useful:. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. How many cycles an operation spends in the alu? The term clock cycles per instruction, which is the average. Clock Cycles Per Instruction X86.

From www.youtube.com

計算機組織 Chapter 1.6 Clock cycle per instruction (CPI) 朱宗賢老師 YouTube Clock Cycles Per Instruction X86 You might find this table useful:. What do you mean by latency? The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. The amd k10 has a wider bus between the l1 instruction cache Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT CPU Performance Evaluation Cycles Per Instruction (CPI) PowerPoint Presentation ID824794 Clock Cycles Per Instruction X86 You might find this table useful:. The average number of core clock cycles per instruction for a series of independent instructions of the same. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. What do you mean by latency? In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 You might find this table useful:. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The average number of core clock cycles per instruction for a series of independent instructions of the same. The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT CPU Design for Multiple Clock Cycles per instruction {CPI > 1} PowerPoint Presentation Clock Cycles Per Instruction X86 You might find this table useful:. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The amd k10 has a wider bus between the l1 instruction cache °one way to define clock cycles: The average number of core clock cycles per instruction for a series of independent instructions of the same. How. Clock Cycles Per Instruction X86.

From docslib.org

CPU Clock Cycles = Instruction Count X CPI CPU Execution Time = DocsLib Clock Cycles Per Instruction X86 The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. What do you mean by latency? Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT Performance PowerPoint Presentation, free download ID6972706 Clock Cycles Per Instruction X86 The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. °one way to define clock cycles: The average number of core clock cycles per instruction for a series of independent instructions of the same. You might find this table useful:. The amd k10 has a wider bus between the l1. Clock Cycles Per Instruction X86.

From www.slideshare.net

Lecture 3 Clock Cycles Per Instruction X86 You might find this table useful:. The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. °one way to define clock cycles: In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. What do you mean by latency? The l1 instruction cache. Clock Cycles Per Instruction X86.

From gallcolleenvirh.blogspot.com

Clock Cycle In Computer Architecture Concepts Of Pipelining Computer Architecture The Clock Cycles Per Instruction X86 The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The average number of core clock cycles per instruction for a series of independent instructions of the same. What do you mean. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. The average number of core clock cycles per instruction for a series of independent instructions of the same. You might find this table useful:. The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or. Clock Cycles Per Instruction X86.

From github.com

GitHub wainwrightmark/criterioncyclesperbyte `CyclesPerByte` measures clock cycles using Clock Cycles Per Instruction X86 °one way to define clock cycles: Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The amd k10 has a wider bus between the l1 instruction cache The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). The term. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The average number of core clock cycles per instruction for a series of independent instructions of the same. °one way to define clock cycles: The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute,. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT Computer Performance Evaluation Cycles Per Instruction (CPI) PowerPoint Presentation ID Clock Cycles Per Instruction X86 The average number of core clock cycles per instruction for a series of independent instructions of the same. How many cycles an operation spends in the alu? °one way to define clock cycles: You might find this table useful:. Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The clock cycles per. Clock Cycles Per Instruction X86.

From slideplayer.com

x86 Processor Architecture ppt download Clock Cycles Per Instruction X86 In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. How many cycles an operation spends in the alu? The amd k10 has a wider bus between the l1 instruction cache What do you mean by latency? The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the. Clock Cycles Per Instruction X86.

From technobyte.org

Timing diagrams and Machine cycles Learn with 8085 instructions Clock Cycles Per Instruction X86 Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. The average number of core. Clock Cycles Per Instruction X86.

From docplayer.net

CPU Performance Evaluation Cycles Per Instruction (CPI) Most computers run synchronously Clock Cycles Per Instruction X86 °one way to define clock cycles: The average number of core clock cycles per instruction for a series of independent instructions of the same. The amd k10 has a wider bus between the l1 instruction cache Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. You might find this table useful:. What. Clock Cycles Per Instruction X86.

From www.studocu.com

Performance 2 Clock Cycles per Instruction (CPI) Not all instructions take the same amount of Clock Cycles Per Instruction X86 The amd k10 has a wider bus between the l1 instruction cache Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. What do you mean by latency? °one way to define clock cycles: The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21. Clock Cycles Per Instruction X86.

From www.scribd.com

x86 Clock Cycles Per Instruction PDF Areas Of Computer Science Computer Engineering Clock Cycles Per Instruction X86 What do you mean by latency? The amd k10 has a wider bus between the l1 instruction cache How many cycles an operation spends in the alu? In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. Clock cycles for program = instructions for a program (called “instruction count ”) x average. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 What do you mean by latency? The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. You might find this table useful:. The average number of core clock cycles per instruction for. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT CPU Design for Multiple Clock Cycles per instruction {CPI > 1} PowerPoint Presentation Clock Cycles Per Instruction X86 You might find this table useful:. The amd k10 has a wider bus between the l1 instruction cache Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The average number of core clock cycles per instruction for a series of independent instructions of the same. In a cisc architecture (x86, 68000, vax). Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT Instruction Clock Cycles PowerPoint Presentation, free download ID4418310 Clock Cycles Per Instruction X86 The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The amd k10 has a wider bus between the l1 instruction cache The average number of core clock cycles. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT Instruction Cycle vs Clock Cycle PowerPoint Presentation, free download ID5771148 Clock Cycles Per Instruction X86 The term clock cycles per instruction, which is the average number of clock cycles each instruction takes to execute, is. °one way to define clock cycles: The clock cycles per instruction (cpi) metric is crucial in computer architecture for evaluating the efficiency of instruction. What do you mean by latency? The average number of core clock cycles per instruction for. Clock Cycles Per Instruction X86.

From slidetodoc.com

CPU Design for Multiple Clock Cycles per instruction Clock Cycles Per Instruction X86 You might find this table useful:. The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). °one way to define clock cycles: How many cycles an operation spends in the alu? The average number of core clock cycles per instruction for a series of independent instructions of. Clock Cycles Per Instruction X86.

From www.slideserve.com

PPT CS 5513 Computer Architecture Lecture 1 Introduction PowerPoint Presentation ID53440 Clock Cycles Per Instruction X86 In a cisc architecture (x86, 68000, vax) one instruction is powerful, but it takes multiple cycles to process. The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). Clock cycles for program = instructions for a program (called “instruction count ”) x average clock cycles. The amd. Clock Cycles Per Instruction X86.

From physicsteacher.in

The Timing Diagram of INR M instruction of 8085 Clock Cycles Per Instruction X86 The l1 instruction cache can provide only 16 bytes per clock, but 3 test r,i need 18 or 21 bytes (depending on register). You might find this table useful:. The average number of core clock cycles per instruction for a series of independent instructions of the same. What do you mean by latency? The clock cycles per instruction (cpi) metric. Clock Cycles Per Instruction X86.