Clock Enable Vhdl . configurable vhdl clock generator. i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. I need a clock divider. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. The full vhdl code for a variable functional clock: instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Below is an example vhdl code for generating. Here's a little example of what i'm looking for : Configurable frequency with 7 external switches of the fpga; so basically what i'm trying to do is to activate and deactivate a clock after a certain time.

from www.numerade.com

The full vhdl code for a variable functional clock: the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Below is an example vhdl code for generating. i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. configurable vhdl clock generator. Here's a little example of what i'm looking for : the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Configurable frequency with 7 external switches of the fpga; so basically what i'm trying to do is to activate and deactivate a clock after a certain time.

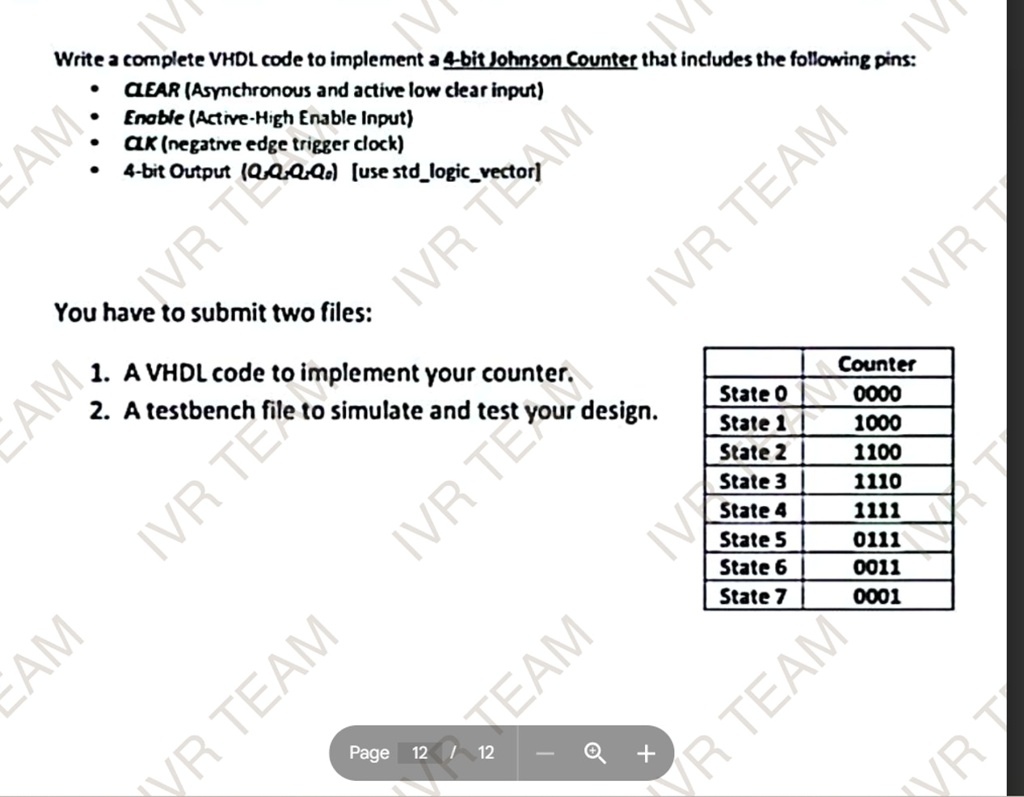

SOLVED Write a complete VHDL code to implement a 4bit Johnson Counter

Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is an example vhdl code for generating. Configurable frequency with 7 external switches of the fpga; the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. I need a clock divider. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. configurable vhdl clock generator. The full vhdl code for a variable functional clock: Here's a little example of what i'm looking for : i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal.

From www.researchgate.net

(a) Dflipflop. (b) Reset synchronicity. (c) Resetclock contest Clock Enable Vhdl The full vhdl code for a variable functional clock: Configurable frequency with 7 external switches of the fpga; so basically what i'm trying to do is to activate and deactivate a clock after a certain time. configurable vhdl clock generator. I need a clock divider. i have 100mhz system clock and i would like to have a. Clock Enable Vhdl.

From www.slideserve.com

PPT ECE 545—Digital System Design with VHDL Lecture 1 PowerPoint Clock Enable Vhdl Configurable frequency with 7 external switches of the fpga; Here's a little example of what i'm looking for : I need a clock divider. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential. Clock Enable Vhdl.

From www.youtube.com

VHDL with Xilinx LED Blink Tutorial YouTube Clock Enable Vhdl configurable vhdl clock generator. I need a clock divider. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is an example vhdl code for generating. Here's a little example of what i'm looking for : i have 100mhz system clock and i would like to have a 200hz. Clock Enable Vhdl.

From www.reddit.com

Help please When a button is pressed, the light should stay on for 10 Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. The full vhdl code for a variable functional clock: instead of creating another clock of 1khz, you should create a 1khz clock enable signal. i have 100mhz system clock and i would like to have a 200hz enable signal for. Clock Enable Vhdl.

From www.chegg.com

Solved Write the VHDL code for a 24 Decoder with an Enable Clock Enable Vhdl Here's a little example of what i'm looking for : configurable vhdl clock generator. i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. I need a clock divider. so basically. Clock Enable Vhdl.

From www.numerade.com

SOLVED HW2 Complete the VHDL model below of a synchronous clear load Clock Enable Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. Here's a. Clock Enable Vhdl.

From electronics.stackexchange.com

VHDL how to write data in FIFO (first in first out) and read data Clock Enable Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Configurable frequency with 7 external switches of the fpga; i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. The full vhdl code for a variable functional clock: Here's a. Clock Enable Vhdl.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. configurable vhdl clock generator. Configurable frequency with 7 external switches of the fpga; i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. Here's a little example of what i'm. Clock Enable Vhdl.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Clock Enable Vhdl so basically what i'm trying to do is to activate and deactivate a clock after a certain time. Here's a little example of what i'm looking for : Configurable frequency with 7 external switches of the fpga; the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is an example. Clock Enable Vhdl.

From www.engineersgarage.com

VHDL Tutorial 16 Design a D flipflop using VHDL Clock Enable Vhdl Configurable frequency with 7 external switches of the fpga; instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Here's a little example of what i'm looking for : The full vhdl code for a variable functional clock: the next thing we do when writing a vhdl testbench is generate a clock and. Clock Enable Vhdl.

From www.researchgate.net

(PDF) Verifying VHDL designs with multiple clocks in SMV Clock Enable Vhdl Here's a little example of what i'm looking for : i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. The full vhdl code for a variable functional clock: instead of creating another clock of 1khz, you should create a 1khz clock enable signal. the next thing. Clock Enable Vhdl.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Enable Vhdl instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Here's a little example of what i'm looking for : the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Below is an example vhdl code for generating. configurable vhdl clock generator. Configurable frequency. Clock Enable Vhdl.

From www.numerade.com

SOLVED Text Digital Logic Design The following circuit is a 4bit Clock Enable Vhdl configurable vhdl clock generator. Here's a little example of what i'm looking for : Below is an example vhdl code for generating. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. i have 100mhz system clock and i would like to have a 200hz enable signal for enabling. Clock Enable Vhdl.

From www.numerade.com

SOLVED Objectives Design and test a synchronous sequential circuit Clock Enable Vhdl The full vhdl code for a variable functional clock: I need a clock divider. Below is an example vhdl code for generating. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Here's a little. Clock Enable Vhdl.

From primehomeworkhelper.com

Part Consider Circuit Figure 1 4 Bit Synchronous Counter Uses Four T Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. The full vhdl code for a variable functional clock: Here's a little example of what i'm looking for : Configurable frequency with 7 external switches of the fpga; configurable vhdl clock generator. instead of creating another clock of 1khz, you. Clock Enable Vhdl.

From www.reddit.com

Counter value? Currently attempting to learn VHDL. Can anyone explain Clock Enable Vhdl Here's a little example of what i'm looking for : so basically what i'm trying to do is to activate and deactivate a clock after a certain time. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic. Clock Enable Vhdl.

From www.numerade.com

SOLVED Q1) Write a VHDL code for the following combinational circuit Clock Enable Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. configurable vhdl clock generator. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is. Clock Enable Vhdl.

From electronics.stackexchange.com

VHDL ALU, 8bit register Electrical Engineering Stack Exchange Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. configurable vhdl clock generator. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. I need a clock divider. Here's a little example of what i'm looking for : Below is an example vhdl code. Clock Enable Vhdl.

From www.pinterest.com.au

FPGA LED blink VHDL FPGA learn by Examples Ep02 VHDL clock divider Clock Enable Vhdl i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is an example vhdl code for generating. The full vhdl code for a variable functional clock: Here's a little example. Clock Enable Vhdl.

From electronics.stackexchange.com

How do we set time in vhdl simulation for an fpga kit having clock of Clock Enable Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. The full vhdl code for a variable functional clock: configurable vhdl clock generator. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. I need a clock divider. Below is an example vhdl code. Clock Enable Vhdl.

From vdocuments.mx

The Design of Digital Frequency Synthesizer Based On VHDL · K is Clock Enable Vhdl configurable vhdl clock generator. I need a clock divider. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Here's a little example of what i'm looking for : The full vhdl code for a. Clock Enable Vhdl.

From www.chegg.com

Solved 2.21 Implement the following VHDL code using these Clock Enable Vhdl i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. I need a clock divider. so basically what i'm trying to do is to activate and deactivate a clock after a certain. Clock Enable Vhdl.

From www.numerade.com

SOLVED Subject A SevenSegment Display Driver Chip with Shift Clock Enable Vhdl The full vhdl code for a variable functional clock: I need a clock divider. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is an example vhdl code for generating. Here's a little example of what i'm looking for : i have 100mhz system clock and i would like. Clock Enable Vhdl.

From www.youtube.com

How to Implement Register in VHDL using ModelSim YouTube Clock Enable Vhdl I need a clock divider. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. Configurable frequency with 7 external switches of the fpga; the next thing we do. Clock Enable Vhdl.

From lambdageeks.com

VHDL Tutorials 13 Important Concepts LAMBDAGEEKS Clock Enable Vhdl configurable vhdl clock generator. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. Configurable frequency with 7 external switches of the fpga; I need a clock divider. The full vhdl code for a variable functional clock: Here's a little example of what i'm looking for : i have. Clock Enable Vhdl.

From www.numerade.com

SOLVED Write a complete VHDL code to implement a 4bit Johnson Counter Clock Enable Vhdl i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. Below is an example vhdl code for generating. so basically what i'm trying to do is to activate and deactivate. Clock Enable Vhdl.

From electronics.stackexchange.com

timing Generation of non overlapping clocks on FPGA using VHDL Clock Enable Vhdl i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. The. Clock Enable Vhdl.

From electronics.stackexchange.com

What do i need to connect to clock_enable pin from VHDL box in Clock Enable Vhdl configurable vhdl clock generator. Here's a little example of what i'm looking for : Below is an example vhdl code for generating. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. I need. Clock Enable Vhdl.

From elsetyellette.pages.dev

When Do The Clocks Turn Back In 2025 Faydra Deerdre Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. configurable vhdl clock generator. Here's a little example of what i'm looking for : I need a clock divider. i have. Clock Enable Vhdl.

From stackoverflow.com

counter How to implement a clock enable in VHDL? Stack Overflow Clock Enable Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. Configurable frequency with 7 external switches of the fpga; Below is an example vhdl code for generating. The full vhdl code for a variable functional clock: I need a clock divider. i have 100mhz system clock and i would like. Clock Enable Vhdl.

From studylib.net

vhdl instructions Clock Enable Vhdl i have 100mhz system clock and i would like to have a 200hz enable signal for enabling the state machine. I need a clock divider. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. Here's a little example of what i'm looking for : The full vhdl code for a variable functional. Clock Enable Vhdl.

From jjmk.dk

5.2 Multiple Clock Clock Enable Vhdl instead of creating another clock of 1khz, you should create a 1khz clock enable signal. configurable vhdl clock generator. Configurable frequency with 7 external switches of the fpga; so basically what i'm trying to do is to activate and deactivate a clock after a certain time. Here's a little example of what i'm looking for : . Clock Enable Vhdl.

From www.numerade.com

SOLVED Draw a state diagram below for a 3bit binary even number up Clock Enable Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. configurable vhdl clock generator. instead of creating another clock of 1khz, you should create a 1khz clock enable signal. The full vhdl code for a variable functional clock: the next thing we do when writing a vhdl testbench is. Clock Enable Vhdl.

From jjmk.dk

5.2 Multiple Clock Clock Enable Vhdl Configurable frequency with 7 external switches of the fpga; the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic. I need a clock divider. so basically what i'm trying to do is to activate and deactivate a clock after a certain time. instead of creating another clock of 1khz, you. Clock Enable Vhdl.

From www.engineersgarage.com

VHDL Tutorial 5 Design, simulate and verify NAND, NOR, XOR and XNOR Clock Enable Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. The full vhdl code for a variable functional clock: Configurable frequency with 7 external switches of the fpga; configurable vhdl clock generator. the vast majority of vhdl designs uses clocked logic, also known as synchronous logic or sequential logic.. Clock Enable Vhdl.