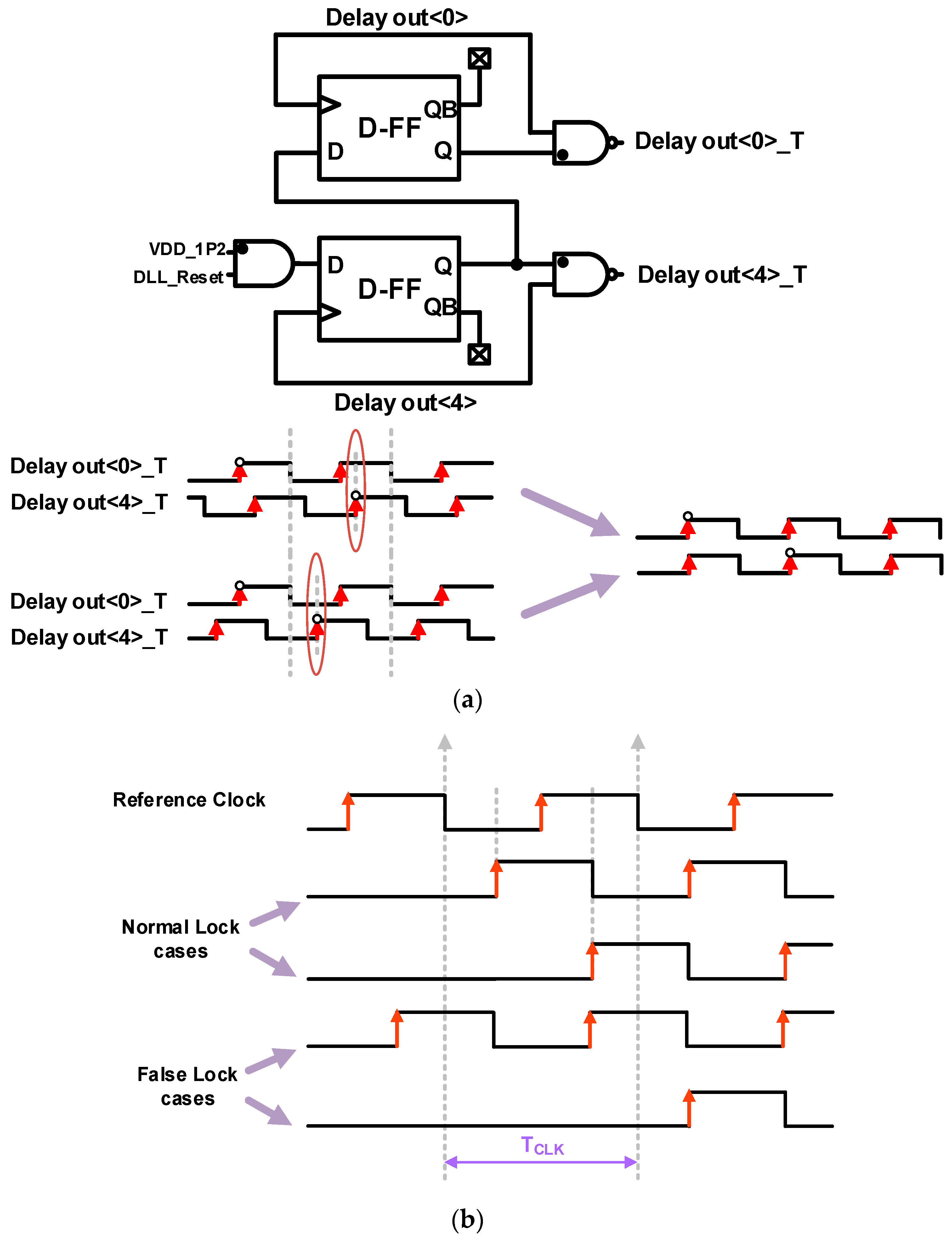

Digital Clock Doubler . This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. The trouble with it is that it relies on propagation delays in delay chains in order. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. Doublers are possible using digital circuits, the following diagram is one such example. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and.

from www.mdpi.com

This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. The trouble with it is that it relies on propagation delays in delay chains in order. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. Doublers are possible using digital circuits, the following diagram is one such example. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle?

Electronics Free FullText Design of a Clock Doubler Based on Delay

Digital Clock Doubler Doublers are possible using digital circuits, the following diagram is one such example. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. The trouble with it is that it relies on propagation delays in delay chains in order. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? Doublers are possible using digital circuits, the following diagram is one such example.

From www.eevblog.com

0Hz 600Hz 5v Square Wave Doubler circuit? Page 1 Digital Clock Doubler To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? Doublers are possible using digital. Digital Clock Doubler.

From www.semanticscholar.org

Figure 2 from A 1.0 /spl mu/m CMOS alldigital clock multiplier Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. The trouble with it is that it relies on propagation delays in delay chains in order. Is it possible. Digital Clock Doubler.

From www.researchgate.net

(PDF) A Highly Digital MDLLBased Clock Multiplier That Leverages a Digital Clock Doubler Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? Doublers are possible using digital circuits, the following diagram is one such example. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. The. Digital Clock Doubler.

From wirepartmonoclines.z14.web.core.windows.net

Digital Clock Circuit Diagram Logic Gates Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. The trouble with it is that it relies on propagation delays in delay chains in order. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. Doublers are possible. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? A digital clock frequency doubler. Digital Clock Doubler.

From www.amazon.com

ANJANK Digital Alarm Clock FM Radio Large LED Number Digital Clock Doubler Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. Doublers are possible using digital circuits, the following diagram is one such example. In this paper, we. Digital Clock Doubler.

From www.semanticscholar.org

Fully digital clock frequency doubler Semantic Scholar Digital Clock Doubler Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. In this paper, we have. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? The trouble with it is that it relies on propagation delays in delay chains in order. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time. Digital Clock Doubler.

From www.researchgate.net

(a) Crosscoupled voltage doubler and (b) its circuit operation in Digital Clock Doubler In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. The trouble with it is that it relies on propagation delays in delay chains in order. A digital. Digital Clock Doubler.

From www.electroniclinic.com

How to design digital clock using counters decoders and displays Digital Clock Doubler In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. The trouble with it is that it relies on propagation delays in delay chains in order. Doublers are possible using digital circuits, the following diagram is one such example.. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. A digital clock frequency doubler capable of handling large. Digital Clock Doubler.

From www.electroniclinic.com

How to design digital clock using counters decoders and displays Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. Doublers are possible using digital circuits, the following diagram is one such example. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. Doublers are possible using digital circuits, the following diagram is one such example. Is it possible to multiply the. Digital Clock Doubler.

From www.semanticscholar.org

A CLOCK FREQUENCY DOUBLER USING A PASSIVE COMPARATOR CIRCUIT INTEGRATOR Digital Clock Doubler In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. Doublers are possible using digital circuits, the following diagram is one such example. The trouble with it is. Digital Clock Doubler.

From giokmncdt.blob.core.windows.net

Digital Clock Frequency Multiplier at Jennie Fane blog Digital Clock Doubler To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. The trouble with it is that it relies on propagation delays in delay chains in order. Doublers are possible using digital circuits, the following diagram is one such example.. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. This fully digital clock frequency doubler can be used for. Digital Clock Doubler.

From www.fpgarelated.com

comp.arch.fpga Xilinx Clock Doubler Digital Clock Doubler In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. A digital clock frequency doubler capable of handling large. Digital Clock Doubler.

From www.semanticscholar.org

Figure 2 from A 6.4/3.2/1.6 Gb/s low power interface with all digital Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. The trouble with it is that it relies on propagation delays in delay chains in order. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. Is it possible to multiply. Digital Clock Doubler.

From lookmumnocomputer.discourse.group

Working Clock Multiplier/Divider/Phase Shifter with tolerance for Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. The trouble with it is that it relies on propagation delays in delay chains in order. Is it possible. Digital Clock Doubler.

From dqydj.com

How to Multiply The Frequency of Digital Logic Clocks Using a PLL Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. The trouble with it is that it. Digital Clock Doubler.

From www.researchgate.net

(PDF) An alldigital PLL clock multiplier Digital Clock Doubler The trouble with it is that it relies on propagation delays in delay chains in order. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay. Digital Clock Doubler.

From www.walmart.com

Mainstays Dual Black Digital Alarm Clock with LED Display Model Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. The trouble with it is that it relies on propagation delays in delay chains in order. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. A digital. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. The trouble with it is that it relies on propagation delays in delay chains in order. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. Doublers are possible using digital. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. The trouble with it is. Digital Clock Doubler.

From www.semanticscholar.org

Fully digital clock frequency doubler Semantic Scholar Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. Doublers are possible using digital circuits, the following diagram is one such example. The trouble with it is that. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? To double the clock frequency using only logic gates one can simply pass it. Digital Clock Doubler.

From www.researchgate.net

Frequency doubler circuit Download Scientific Diagram Digital Clock Doubler Doublers are possible using digital circuits, the following diagram is one such example. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. Is it possible to multiply the frequency of a digital signal using digital components alone, and. Digital Clock Doubler.

From www.semanticscholar.org

Fully digital clock frequency doubler Semantic Scholar Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. To double the clock frequency using only logic gates one can simply pass it through a buffer with. Digital Clock Doubler.

From www.multisim.com

Coincidence Gate Clock/Frequency Doubler Multisim Live Digital Clock Doubler Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve the duty cycle? In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. This fully digital clock frequency doubler can be used for wide digital applications requiring very high. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. Is it possible to multiply the frequency of a digital signal using digital components alone, and at the same time, preserve. Digital Clock Doubler.

From cmosedu.com

Lab Digital Clock Doubler The trouble with it is that it relies on propagation delays in delay chains in order. In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. Doublers are possible using digital circuits, the following diagram is one such example. This fully digital clock frequency doubler can be used for wide. Digital Clock Doubler.

From dqydj.com

Double Clock Frequency with Digital Logic How We Did it DQYDJ Digital Clock Doubler The trouble with it is that it relies on propagation delays in delay chains in order. Doublers are possible using digital circuits, the following diagram is one such example. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply.. Digital Clock Doubler.

From www.mdpi.com

Electronics Free FullText Design of a Clock Doubler Based on Delay Digital Clock Doubler This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on demand. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply. In this paper, we have designed a. Digital Clock Doubler.

From www.researchgate.net

Frequency doubler. (a) Block diagram. (b) Timing diagram. (c) DCC block Digital Clock Doubler In this paper, we have designed a clock frequency doubler circuit suitable to reduce power consumption in a clock distribution. A digital clock frequency doubler capable of handling large variation in input duty cycle and pvt (process, voltage and. This fully digital clock frequency doubler can be used for wide digital applications requiring very high speeds, robustness, and time on. Digital Clock Doubler.