Concurrency In Hardware Description Language . 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp captures the behavior of a hardware. Inherent concurrency (verilog) module cam. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),.

from slidetodoc.com

Inherent concurrency (verilog) module cam. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp captures the behavior of a hardware. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),.

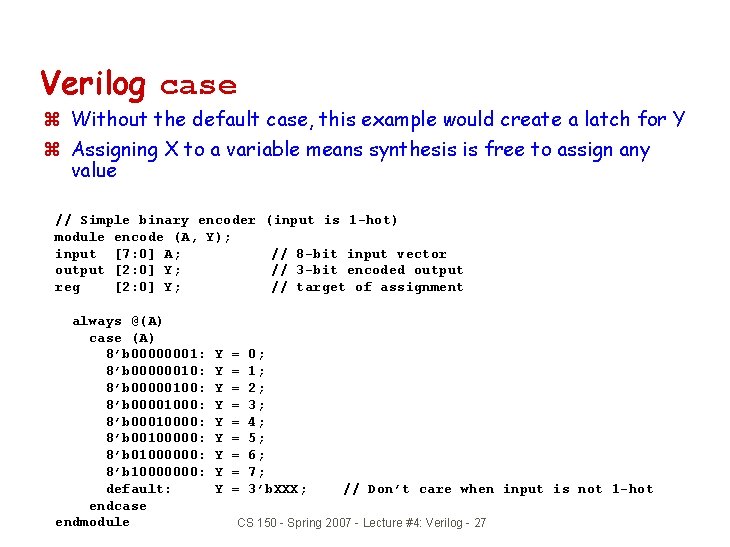

Hardware Description Languages Verilog z Verilog y Structural

Concurrency In Hardware Description Language A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. Inherent concurrency (verilog) module cam. Hopcp captures the behavior of a hardware. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the.

From www.slideserve.com

PPT AHDL Introduction PowerPoint Presentation, free download ID Concurrency In Hardware Description Language A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. In this article,. Concurrency In Hardware Description Language.

From www.scribd.com

Hardware Description Languages PDF Hardware Description Language Concurrency In Hardware Description Language The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. Hopcp captures the behavior of a hardware. Inherent concurrency (verilog) module cam.. Concurrency In Hardware Description Language.

From thecustomizewindows.com

Hardware Description Language Structure and Simulation Concurrency In Hardware Description Language In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT The Verilog Hardware Description Language PowerPoint Presentation Concurrency In Hardware Description Language Inherent concurrency (verilog) module cam. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. A hardware description language must. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Languages PowerPoint Presentation, free Concurrency In Hardware Description Language /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. Inherent concurrency (verilog) module cam. Hopcp captures the behavior of a hardware. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Hopcp. Concurrency In Hardware Description Language.

From www.scribd.com

Verilog Hardware Description Language Hardware Description Language Concurrency In Hardware Description Language We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. In this article, we discuss the application of. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Behavioral Hardware Description Languages PowerPoint Presentation Concurrency In Hardware Description Language Inherent concurrency (verilog) module cam. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. A hardware description language must be. Concurrency In Hardware Description Language.

From www.studypool.com

SOLUTION Hardware description language (HDL), Advance Digital Concept Concurrency In Hardware Description Language We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. Hopcp is a language for the specification,. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Language PowerPoint Presentation, free Concurrency In Hardware Description Language /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Hopcp captures the behavior of a hardware. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. A hardware description language must be able to simulate a. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Languages PowerPoint Presentation, free Concurrency In Hardware Description Language A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. Hopcp captures the behavior of a hardware. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Language (HDL) PowerPoint Presentation, free Concurrency In Hardware Description Language The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. Hopcp captures the behavior of a hardware. 8.1 traditional modelling of concurrent. Concurrency In Hardware Description Language.

From courses.cs.washington.edu

Hardware description languages Concurrency In Hardware Description Language Hopcp captures the behavior of a hardware. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. Inherent concurrency (verilog) module cam. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept. Concurrency In Hardware Description Language.

From www.youtube.com

Using Hardware Description Languages in TINACloud, part 1 Creating Concurrency In Hardware Description Language Hopcp captures the behavior of a hardware. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler. Concurrency In Hardware Description Language.

From www.youtube.com

Introduction to Hardware Description Languages Verilog HDL Part 1 Concurrency In Hardware Description Language 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Inherent concurrency (verilog) module cam. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. /* write functionality. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Language PowerPoint Presentation, free Concurrency In Hardware Description Language In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional. Concurrency In Hardware Description Language.

From www.mdpi.com

Electronics Free FullText SHDL—A Hardware Description Language and Concurrency In Hardware Description Language /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Inherent concurrency (verilog) module cam. Hopcp. Concurrency In Hardware Description Language.

From slidetodoc.com

Lab 1 and 2 Digital System Design Using Concurrency In Hardware Description Language We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp captures the behavior of a hardware. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. A hardware description language must be able to simulate. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Fundamentals of Hardware Description Language PowerPoint Concurrency In Hardware Description Language Hopcp captures the behavior of a hardware. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Inherent concurrency (verilog) module cam. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. Hopcp is a language for the specification,. Concurrency In Hardware Description Language.

From studylib.net

Hardware Description Languages M E 2202 Tutorial Sheet Concurrency In Hardware Description Language Hopcp is a language for the specification, simulation, and synthesis of hardware systems. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. A hardware description language must be able to simulate a. Concurrency In Hardware Description Language.

From einvoice.fpt.com.vn

PPT Hardware Description Language Introduction PowerPoint, 58 OFF Concurrency In Hardware Description Language Inherent concurrency (verilog) module cam. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling. Concurrency In Hardware Description Language.

From www.semanticscholar.org

Hardware description language Semantic Scholar Concurrency In Hardware Description Language We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. Inherent concurrency (verilog) module cam. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. Hopcp captures the behavior of a hardware. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp is a language for the specification, simulation, and synthesis of. Concurrency In Hardware Description Language.

From slideplayer.com

Hardware Description Language ppt download Concurrency In Hardware Description Language The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. Inherent concurrency (verilog) module cam. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. In this article, we discuss. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Languages Verilog PowerPoint Presentation Concurrency In Hardware Description Language We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Hopcp is a language for the specification, simulation,. Concurrency In Hardware Description Language.

From www.youtube.com

Overview of Hardware Description Language YouTube Concurrency In Hardware Description Language Hopcp captures the behavior of a hardware. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. We discuss how concurrency in hardware description languages (hdls) presents opportunities for. Concurrency In Hardware Description Language.

From www.esa.int

ESA Hardware Description Languages and Abstraction Levels Concurrency In Hardware Description Language Hopcp captures the behavior of a hardware. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the. Concurrency In Hardware Description Language.

From slidetodoc.com

Hardware Description Languages Verilog z Verilog y Structural Concurrency In Hardware Description Language Inherent concurrency (verilog) module cam. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. In this article, we discuss the application of. Concurrency In Hardware Description Language.

From dokumen.tips

(PDF) Hardware description language (HDL) A hardware description Concurrency In Hardware Description Language 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Hopcp captures the behavior of a hardware. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. We discuss how concurrency. Concurrency In Hardware Description Language.

From www.allaboutcircuits.com

What Is a Hardware Description Language (HDL)? Technical Articles Concurrency In Hardware Description Language We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. 8.1 traditional modelling of concurrent systems in hardware description languages. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware description languages PowerPoint Presentation, free Concurrency In Hardware Description Language /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. Inherent concurrency (verilog) module cam. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Languages PowerPoint Presentation, free Concurrency In Hardware Description Language Hopcp is a language for the specification, simulation, and synthesis of hardware systems. Hopcp captures the behavior of a hardware. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. A hardware description language must be able to simulate a system whose components have been designed to different levels of. Concurrency In Hardware Description Language.

From slideplayer.com

Verilog Digital System Design Z. Navabi, McGrawHill, ppt download Concurrency In Hardware Description Language 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. Hopcp captures the behavior of a hardware. Inherent. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Chapter5 Hardware Description Languages PowerPoint Presentation Concurrency In Hardware Description Language Hopcp captures the behavior of a hardware. Inherent concurrency (verilog) module cam. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. The modelling techniques of the concurrent control systems in hardware description. Concurrency In Hardware Description Language.

From www.youtube.com

Hardware Description Language YouTube Concurrency In Hardware Description Language A hardware description language must be able to simulate a system whose components have been designed to different levels of detail. We discuss how concurrency in hardware description languages (hdls) presents opportunities for expression reuse across. /* write functionality */ decoder write_dec(.inp_i(d.write_index_i),. Hopcp captures the behavior of a hardware. In this article, we discuss the application of compiler technology for. Concurrency In Hardware Description Language.

From stories.mlh.io

Hardware Description Languages; What are they and why should I care? Concurrency In Hardware Description Language 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. The modelling techniques of the concurrent control systems in hardware description languages (hdls) are presented in. In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. Hopcp captures the behavior of a hardware.. Concurrency In Hardware Description Language.

From www.slideserve.com

PPT Hardware Description Language Introduction PowerPoint Concurrency In Hardware Description Language In this article, we discuss the application of compiler technology for eliminating redundant computation in hardware simulation. 8.1 traditional modelling of concurrent systems in hardware description languages the traditional modelling concept relies on the behavior of the. Hopcp is a language for the specification, simulation, and synthesis of hardware systems. We discuss how concurrency in hardware description languages (hdls) presents. Concurrency In Hardware Description Language.