Clock Distribution In Vlsi Ppt . Traditionally, chip is surrounded by pad. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence. introduction to cmos vlsi design design for skew outline clock distribution clock. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • all clock pins are driven by a single clock source, which we considered ideal until now. Distinguish this from previous or next.

from www.slideserve.com

introduction to cmos vlsi design design for skew outline clock distribution clock. Traditionally, chip is surrounded by pad. • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Distinguish this from previous or next. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence.

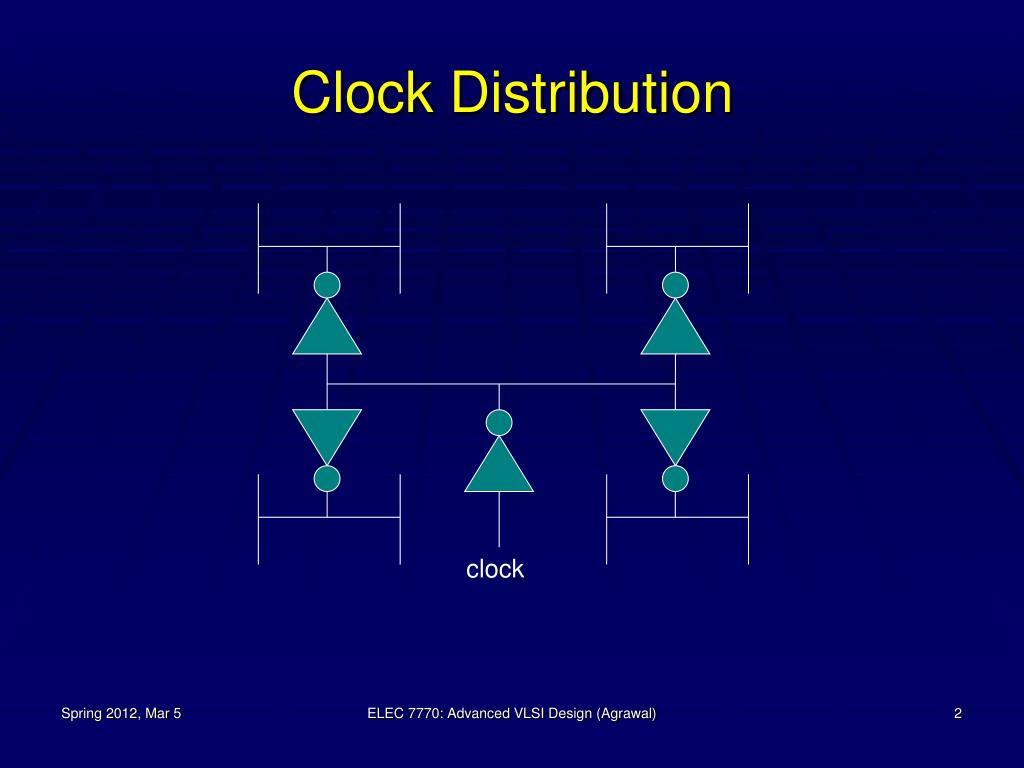

PPT ELEC 7770 Advanced VLSI Design Spring 2012 Gate Sizing PowerPoint Presentation ID3593719

Clock Distribution In Vlsi Ppt because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. Traditionally, chip is surrounded by pad. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence. introduction to cmos vlsi design design for skew outline clock distribution clock. Distinguish this from previous or next. • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well.

From studylib.net

A Low Power VLSI ETSPC based single phase clock distribution Clock Distribution In Vlsi Ppt because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. introduction to cmos vlsi design design for skew outline clock distribution clock. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Traditionally, chip is surrounded by pad. • all clock. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT ELEC 7770 Advanced VLSI Design Spring 2012 Gate Sizing PowerPoint Presentation ID3593719 Clock Distribution In Vlsi Ppt • we may have several clocks and some. • all clock pins are driven by a single clock source, which we considered ideal until now. Synchronous systems use a clock to keep operations in sequence. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. Distinguish this from previous or. Clock Distribution In Vlsi Ppt.

From www.youtube.com

Clock Distribution in Physical Design of VLSI YouTube Clock Distribution In Vlsi Ppt Synchronous systems use a clock to keep operations in sequence. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. • we may have several clocks and some. • all clock pins are driven by a single clock source, which we considered ideal until now. Distinguish this from previous or next.. Clock Distribution In Vlsi Ppt.

From www.semanticscholar.org

Figure 3 from Design of GHz VLSI clock distribution circuit Semantic Scholar Clock Distribution In Vlsi Ppt because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. Synchronous systems use a clock to keep operations in sequence. Traditionally, chip is surrounded by pad. • we may have several clocks and some. introduction to cmos vlsi design design for skew outline clock distribution clock. Distinguish this from previous. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID9436227 Clock Distribution In Vlsi Ppt Distinguish this from previous or next. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • all clock pins are driven by a single clock source, which we considered ideal until now. Synchronous systems use a clock to keep operations in sequence. • we may have several clocks and. Clock Distribution In Vlsi Ppt.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi Clock Distribution In Vlsi Ppt because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • all clock pins are driven by a single clock source, which we considered ideal until now. Distinguish this from previous or next. introduction to cmos vlsi design design for skew outline clock distribution clock. • we may have. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Clock Skewtolerant circuits PowerPoint Presentation ID Clock Distribution In Vlsi Ppt • all clock pins are driven by a single clock source, which we considered ideal until now. Traditionally, chip is surrounded by pad. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of. Clock Distribution In Vlsi Ppt.

From www.studypool.com

SOLUTION Vlsi technology application clock distribution using modified prescaler Studypool Clock Distribution In Vlsi Ppt the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Traditionally, chip is surrounded by pad. • we may have several clocks and some. • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches every cycle, cg charges and. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution In Vlsi Ppt • we may have several clocks and some. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. introduction to cmos vlsi design design for skew outline clock distribution clock. • all clock pins are driven by a single clock source, which we considered ideal until now. the. Clock Distribution In Vlsi Ppt.

From pdfslide.net

(PDF) A low power single phase clock distribution using VLSI technology Clock Distribution In Vlsi Ppt because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • all clock pins are driven by a single clock source, which we considered ideal until now. Traditionally, chip is surrounded by pad. • we may have several clocks and some. introduction to cmos vlsi design design for skew. Clock Distribution In Vlsi Ppt.

From www.academia.edu

(PDF) A Low Power Single Phase Clock Distribution Using VLSI Technology International Journal Clock Distribution In Vlsi Ppt introduction to cmos vlsi design design for skew outline clock distribution clock. Distinguish this from previous or next. Synchronous systems use a clock to keep operations in sequence. • all clock pins are driven by a single clock source, which we considered ideal until now. • we may have several clocks and some. the document provides an. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution In Vlsi Ppt Distinguish this from previous or next. • all clock pins are driven by a single clock source, which we considered ideal until now. Traditionally, chip is surrounded by pad. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • we may have several clocks and some. Synchronous systems use. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID4599510 Clock Distribution In Vlsi Ppt • all clock pins are driven by a single clock source, which we considered ideal until now. Traditionally, chip is surrounded by pad. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Distinguish this from previous or next. because the clock switches every cycle, cg charges and discharges every. Clock Distribution In Vlsi Ppt.

From www.slideshare.net

Low Power Clock Distribution Schemes in VLSI Design PDF Clock Distribution In Vlsi Ppt Distinguish this from previous or next. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. introduction to cmos vlsi design design for skew outline clock distribution clock. Traditionally, chip is surrounded by pad. Synchronous systems use a clock to keep operations in sequence. the document provides an overview. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Synchronization & Distribution in VLSI Circuits Project LH10MHI PowerPoint Clock Distribution In Vlsi Ppt introduction to cmos vlsi design design for skew outline clock distribution clock. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Distinguish this from previous or next. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • we may have. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution In Vlsi Ppt the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Synchronous systems use a clock to keep operations in sequence. Traditionally, chip is surrounded by pad. • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches every cycle, cg. Clock Distribution In Vlsi Ppt.

From www.youtube.com

PD Lec 52 CTS Algorithms CTS Clock Tree Synthesis VLSI Physical Design YouTube Clock Distribution In Vlsi Ppt Distinguish this from previous or next. Traditionally, chip is surrounded by pad. • we may have several clocks and some. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. introduction to cmos vlsi design design for skew outline clock distribution clock. • all clock pins are driven by a. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Using Systemona Chip as a Vehicle for VLSI Design Education PowerPoint Presentation Clock Distribution In Vlsi Ppt Traditionally, chip is surrounded by pad. introduction to cmos vlsi design design for skew outline clock distribution clock. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence. • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution In Vlsi Ppt the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Distinguish this from previous or next. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence. • all clock pins are driven by a single clock source, which we considered ideal until now.. Clock Distribution In Vlsi Ppt.

From www.researchgate.net

(PDF) Low Power at Different levels of VLSI Design an clock Distribution Schemes Clock Distribution In Vlsi Ppt • all clock pins are driven by a single clock source, which we considered ideal until now. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. introduction to cmos vlsi design. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution In Vlsi Ppt • we may have several clocks and some. • all clock pins are driven by a single clock source, which we considered ideal until now. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. introduction to cmos vlsi design design for skew outline clock distribution clock. Distinguish this from. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Clock Distribution In Vlsi Ppt because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • we may have several clocks and some. • all clock pins are driven by a single clock source, which we considered ideal until now. introduction to cmos vlsi design design for skew outline clock distribution clock. Distinguish this. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution In Vlsi Ppt • all clock pins are driven by a single clock source, which we considered ideal until now. introduction to cmos vlsi design design for skew outline clock distribution clock. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. • we may have several clocks and some. Synchronous systems use. Clock Distribution In Vlsi Ppt.

From www.studypool.com

SOLUTION Vlsi technology application clock distribution using modified prescaler Studypool Clock Distribution In Vlsi Ppt Synchronous systems use a clock to keep operations in sequence. • all clock pins are driven by a single clock source, which we considered ideal until now. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. because the clock switches every cycle, cg charges and discharges every cycle and. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT ADVANCED ANALOG VLSI DESIGN CENTER PowerPoint Presentation, free download ID193070 Clock Distribution In Vlsi Ppt introduction to cmos vlsi design design for skew outline clock distribution clock. • all clock pins are driven by a single clock source, which we considered ideal until now. Traditionally, chip is surrounded by pad. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. • we may have several. Clock Distribution In Vlsi Ppt.

From www.studypool.com

SOLUTION Vlsi technology application clock distribution using modified prescaler Studypool Clock Distribution In Vlsi Ppt Distinguish this from previous or next. Traditionally, chip is surrounded by pad. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Synchronous systems use a clock to keep operations in sequence. . Clock Distribution In Vlsi Ppt.

From siliconvlsi.com

ClockDistribution Techniques Siliconvlsi Clock Distribution In Vlsi Ppt • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. Traditionally, chip is surrounded by pad. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as. Clock Distribution In Vlsi Ppt.

From www.semanticscholar.org

[PDF] Design and analysis of a hierarchical clock distribution system for synchronous standard Clock Distribution In Vlsi Ppt Traditionally, chip is surrounded by pad. Distinguish this from previous or next. introduction to cmos vlsi design design for skew outline clock distribution clock. • we may have several clocks and some. Synchronous systems use a clock to keep operations in sequence. • all clock pins are driven by a single clock source, which we considered ideal until. Clock Distribution In Vlsi Ppt.

From vlsiconceptsforyou.blogspot.com

VLSI Concepts Different Types of Clock Tree Structure Clock Distribution In Vlsi Ppt the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Traditionally, chip is surrounded by pad. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. introduction to cmos vlsi design design for skew outline clock distribution clock. Synchronous systems use a. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT ELEC 7770 Advanced VLSI Design Spring 2008 Zero Skew Clock Routing PowerPoint Clock Distribution In Vlsi Ppt Traditionally, chip is surrounded by pad. • all clock pins are driven by a single clock source, which we considered ideal until now. Distinguish this from previous or next. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. introduction to cmos vlsi design design for skew outline clock distribution. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Clock Skewtolerant circuits PowerPoint Presentation ID Clock Distribution In Vlsi Ppt Traditionally, chip is surrounded by pad. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. introduction to cmos vlsi design design for skew outline clock distribution clock. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • all clock. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Presentation ID4771158 Clock Distribution In Vlsi Ppt Traditionally, chip is surrounded by pad. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Synchronous systems use a clock to keep operations in sequence. Distinguish this from previous or next. introduction to cmos vlsi design design for skew outline clock distribution clock. • we may have several clocks and. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution In Vlsi Ppt Distinguish this from previous or next. the document provides an overview of ideal clock signal properties and challenges in practical implementations, as well. Traditionally, chip is surrounded by pad. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. • we may have several clocks and some. introduction to. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT ELEC 7770 Advanced VLSI Design Spring 2007 Power Aware Microprocessors PowerPoint Clock Distribution In Vlsi Ppt introduction to cmos vlsi design design for skew outline clock distribution clock. • all clock pins are driven by a single clock source, which we considered ideal until now. Traditionally, chip is surrounded by pad. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. Synchronous systems use a. Clock Distribution In Vlsi Ppt.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Presentation ID4771158 Clock Distribution In Vlsi Ppt Distinguish this from previous or next. • we may have several clocks and some. Traditionally, chip is surrounded by pad. • all clock pins are driven by a single clock source, which we considered ideal until now. because the clock switches every cycle, cg charges and discharges every cycle and consumes significant amount of power. introduction to. Clock Distribution In Vlsi Ppt.