Virtual Clock Vlsi . Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. Key significance of virtual clock: A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. So how do we define a clock, if there is no clock in our design? The virtual clock is a clock that is not connected to. A virtual clock is a clock that exists but is not associated with any pin or port of the design. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. A virtual clock is used as a. It is used as a reference in timing analysis to specify the input and output delays relative to a. The answer is virtual clock.

from www.vlsiguru.com

A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. The answer is virtual clock. A virtual clock is a clock that exists but is not associated with any pin or port of the design. A virtual clock is used as a. It is used as a reference in timing analysis to specify the input and output delays relative to a. Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. The virtual clock is a clock that is not connected to. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. So how do we define a clock, if there is no clock in our design?

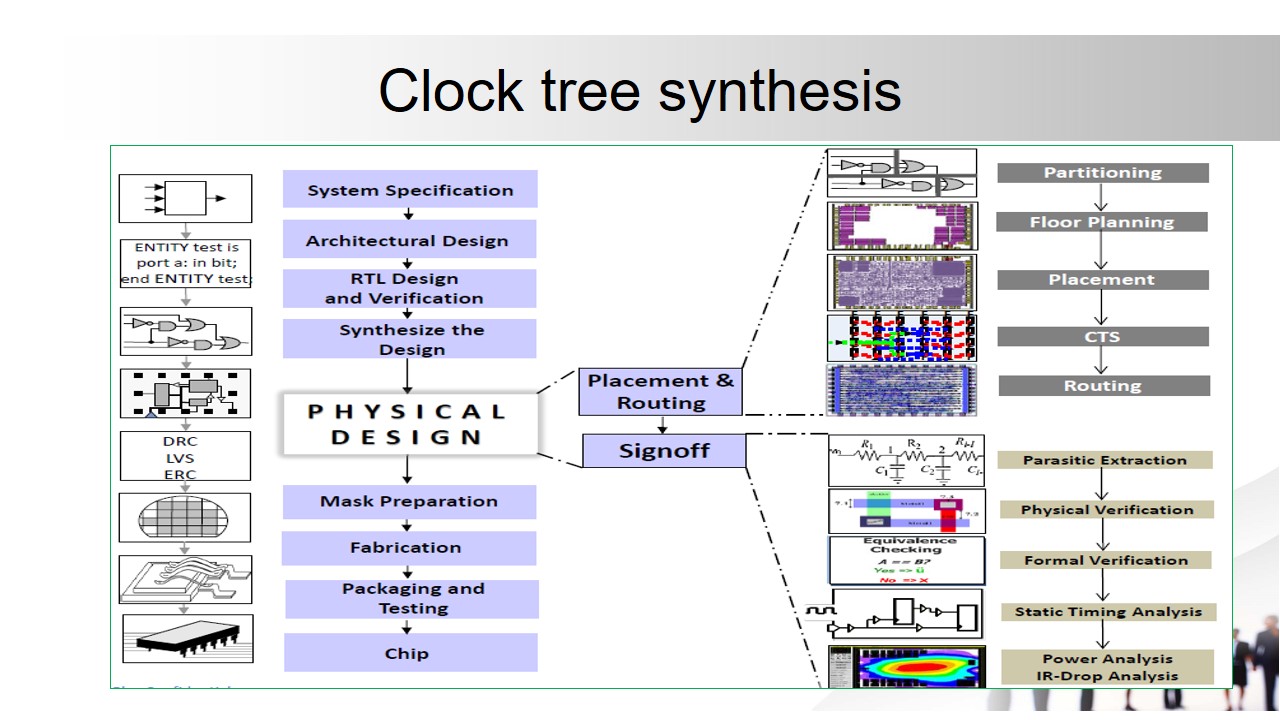

pdbasicsClocktreesynthesis vlsi

Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. It is used as a reference in timing analysis to specify the input and output delays relative to a. A virtual clock is a clock that exists but is not associated with any pin or port of the design. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. Key significance of virtual clock: A virtual clock is used as a. The answer is virtual clock. So how do we define a clock, if there is no clock in our design? The virtual clock is a clock that is not connected to.

From www.youtube.com

VLSI Physical Design Clock Tree Synthesis (CTS) YouTube Virtual Clock Vlsi The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. The answer is virtual clock. Key significance of virtual clock: So how do we define a clock,. Virtual Clock Vlsi.

From www.youtube.com

Integrated Clock Gating Cell ICG Cell in VLSI Clock Gating Cell Virtual Clock Vlsi Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. A virtual clock is a clock that exists but is not associated with any pin or port of the design. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before. Virtual Clock Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi Virtual Clock Vlsi A virtual clock is a clock that exists but is not associated with any pin or port of the design. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. It is used as a reference in timing analysis to specify the input and output delays relative to. Virtual Clock Vlsi.

From siliconvlsi.com

What is the generated clock and virtual clock? Siliconvlsi Virtual Clock Vlsi Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. Key significance of virtual clock: A virtual clock is a clock that exists but is not associated with any pin or port of the design. The virtual clock enables early timing analysis during the physical design phase, helping identify. Virtual Clock Vlsi.

From vlsiuniverse.blogspot.com

Virtual clock purpose and timing Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. It is used as a reference in timing analysis to specify the input and output delays relative to a. So how do we define a clock, if there is no clock in our design? Stating more. Virtual Clock Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Virtual Clock Vlsi The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. A virtual clock is a clock without a real source in the design, or a clock that. Virtual Clock Vlsi.

From www.youtube.com

Lecture6 VLSI System Testing Clock Skew Types YouTube Virtual Clock Vlsi The virtual clock is a clock that is not connected to. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. Key significance of virtual clock: The answer is virtual clock. Stating more clearly, a virtual clock is a clock that has been defined, but has not been. Virtual Clock Vlsi.

From tech.tdzire.com

What are virtual clocks and why they are needed ? TechnologyTdzire Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. A virtual clock is a clock that exists but is not associated with any pin or port of the design. It is used as a reference in timing analysis to specify the input and output delays. Virtual Clock Vlsi.

From www.youtube.com

Digital Clock VLSI Lab Columbia University YouTube Virtual Clock Vlsi The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. It is used as a reference in timing analysis to specify the input and output delays relative to a. Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with. Virtual Clock Vlsi.

From www.youtube.com

Virtual Clock Static Timing Analysis YouTube Virtual Clock Vlsi The answer is virtual clock. So how do we define a clock, if there is no clock in our design? It is used as a reference in timing analysis to specify the input and output delays relative to a. A virtual clock is a clock that exists but is not associated with any pin or port of the design. A. Virtual Clock Vlsi.

From www.youtube.com

PD Lec 59 Master, Generated and Virtual Clocks Type of clocks Virtual Clock Vlsi The answer is virtual clock. It is used as a reference in timing analysis to specify the input and output delays relative to a. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. The virtual clock enables early timing analysis during the physical design phase, helping. Virtual Clock Vlsi.

From www.youtube.com

Digital Clock VLSI Design Lab Columbia University 2016 YouTube Virtual Clock Vlsi So how do we define a clock, if there is no clock in our design? Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. The answer is virtual clock. A virtual clock is a clock that exists but is not associated with any pin or port of the. Virtual Clock Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Virtual Clock Vlsi It is used as a reference in timing analysis to specify the input and output delays relative to a. The virtual clock is a clock that is not connected to. So how do we define a clock, if there is no clock in our design? The answer is virtual clock. A virtual clock is a clock that exists but is. Virtual Clock Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi Virtual Clock Vlsi A virtual clock is a clock that exists but is not associated with any pin or port of the design. So how do we define a clock, if there is no clock in our design? Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. Stating more. Virtual Clock Vlsi.

From www.youtube.com

Understanding Clock Tree Synthesis (CTS) in VLSI A Comprehensive Guide Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. Key significance of virtual clock: Stating more clearly, a virtual clock is a. Virtual Clock Vlsi.

From siliconvlsi.com

What is the generated clock and virtual clock? Siliconvlsi Virtual Clock Vlsi So how do we define a clock, if there is no clock in our design? A virtual clock is used as a. The answer is virtual clock. Key significance of virtual clock: It is used as a reference in timing analysis to specify the input and output delays relative to a. A virtual clock is a clock that exists but. Virtual Clock Vlsi.

From www.youtube.com

synthesis constraints STA ,Create and Generated clock...VLSI YouTube Virtual Clock Vlsi Key significance of virtual clock: A virtual clock is a clock that exists but is not associated with any pin or port of the design. It is used as a reference in timing analysis to specify the input and output delays relative to a. So how do we define a clock, if there is no clock in our design? The. Virtual Clock Vlsi.

From vlsiuniverse.blogspot.com

Virtual clock STA VLSI n EDA Virtual Clock Vlsi Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. A virtual clock is a clock that exists but is not associated with any pin or port of the design. A virtual clock is a clock without a real source in the design, or a clock that. Virtual Clock Vlsi.

From vlsi-soc.blogspot.com

VLSI SoC Design Integrated Clock and Power Gating Virtual Clock Vlsi Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. The virtual clock enables early timing analysis during the physical design phase, helping. Virtual Clock Vlsi.

From mungfali.com

Clock Gating VLSI Virtual Clock Vlsi A virtual clock is used as a. Key significance of virtual clock: Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. So how do we define a clock, if there is no clock in our design? The answer is virtual clock. The virtual clock enables early timing analysis. Virtual Clock Vlsi.

From exomtfjnf.blob.core.windows.net

What Is Clock Latency In Vlsi at Shelly Hines blog Virtual Clock Vlsi The answer is virtual clock. Key significance of virtual clock: So how do we define a clock, if there is no clock in our design? A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. A virtual clock is a clock that exists but is not. Virtual Clock Vlsi.

From www.youtube.com

Pulse Synchronizer CDC Toggle Flop synchronization Fast to Slow Virtual Clock Vlsi It is used as a reference in timing analysis to specify the input and output delays relative to a. A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. Key significance of virtual clock: A virtual clock is used as a. A virtual clock is a. Virtual Clock Vlsi.

From loecbuzfo.blob.core.windows.net

How To Use Set_Clock_Groups at Norman Kubiak blog Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. A virtual clock is a clock that exists but is not associated with any pin or port of the design. The answer is virtual clock. So how do we define a clock, if there is no. Virtual Clock Vlsi.

From vlsimaster.com

Generated Clock and Virtual Clock VLSI Master Virtual Clock Vlsi The answer is virtual clock. Stating more clearly, a virtual clock is a clock that has been defined, but has not been associated with any pin/port. A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. A virtual clock is used as a. The virtual clock. Virtual Clock Vlsi.

From vlsi-freaks.blogspot.com

VLSI freaks virtual clocks and their usage Virtual Clock Vlsi It is used as a reference in timing analysis to specify the input and output delays relative to a. The virtual clock is a clock that is not connected to. So how do we define a clock, if there is no clock in our design? Understanding what a virtual clock in vlsi is and how to use it can prevent. Virtual Clock Vlsi.

From mungfali.com

Clock Gating VLSI Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. The virtual clock is a clock that is not connected to. The answer is virtual clock. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the. Virtual Clock Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Virtual Clock Vlsi A virtual clock is a clock that exists but is not associated with any pin or port of the design. A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. A virtual clock is used as a. Key significance of virtual clock: It is used as. Virtual Clock Vlsi.

From siliconvlsi.com

What is the generated clock and virtual clock? Siliconvlsi Virtual Clock Vlsi The virtual clock is a clock that is not connected to. It is used as a reference in timing analysis to specify the input and output delays relative to a. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. A virtual clock is a clock that. Virtual Clock Vlsi.

From vlsitutorials.com

Onchip Clock Controller VLSI Tutorials Virtual Clock Vlsi The answer is virtual clock. Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. The virtual clock is a clock that is not connected to. A virtual clock is used as a. So how do we define a clock, if there is no clock in our. Virtual Clock Vlsi.

From tech.tdzire.com

What are virtual clocks and why they are needed ? TechnologyTdzire Virtual Clock Vlsi The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. The answer is virtual clock. It is used as a reference in timing analysis to specify the input and output delays relative to a. So how do we define a clock, if there is no clock in our. Virtual Clock Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Virtual Clock Vlsi Key significance of virtual clock: It is used as a reference in timing analysis to specify the input and output delays relative to a. So how do we define a clock, if there is no clock in our design? Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall. Virtual Clock Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Clock Tree Synthesis (CTS) Virtual Clock Vlsi Understanding what a virtual clock in vlsi is and how to use it can prevent timing issues and improve the overall design process. The answer is virtual clock. So how do we define a clock, if there is no clock in our design? It is used as a reference in timing analysis to specify the input and output delays relative. Virtual Clock Vlsi.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Virtual Clock Vlsi A virtual clock is a clock that exists but is not associated with any pin or port of the design. It is used as a reference in timing analysis to specify the input and output delays relative to a. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical. Virtual Clock Vlsi.

From vlsitutorials.com

generatedclocks VLSI Tutorials Virtual Clock Vlsi It is used as a reference in timing analysis to specify the input and output delays relative to a. So how do we define a clock, if there is no clock in our design? A virtual clock is a clock that exists but is not associated with any pin or port of the design. The answer is virtual clock. Stating. Virtual Clock Vlsi.

From vlsitutorials.com

logicallyexclusiveclocksexample31 VLSI Tutorials Virtual Clock Vlsi A virtual clock is a clock without a real source in the design, or a clock that does not interact directly with the design. The virtual clock is a clock that is not connected to. The virtual clock enables early timing analysis during the physical design phase, helping identify and rectify timing violations before the physical implementation. Key significance of. Virtual Clock Vlsi.