Clock To Q Propagation Delay . This is the called the propagation delay of the flip flop and is. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq time after clock. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: When clk is ‘high’, “tr2” and “tr4” turns on.

from www.bartleby.com

T ccq time after clock edge that q might be unstable (i.e., start changing) ii. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. When clk is ‘high’, “tr2” and “tr4” turns on. This is the called the propagation delay of the flip flop and is. T pcq time after clock. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay:

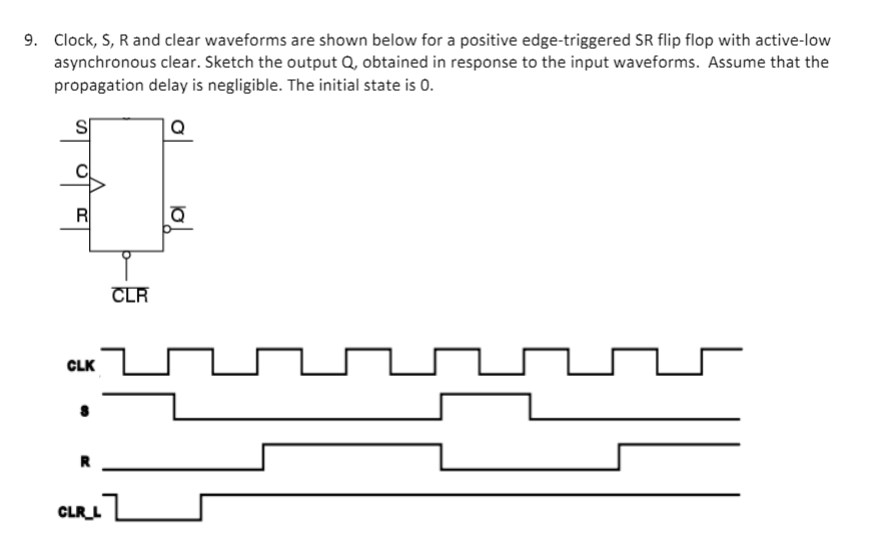

Answered Clock, S, R and clear waveforms are… bartleby

Clock To Q Propagation Delay When clk is ‘high’, “tr2” and “tr4” turns on. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T pcq time after clock. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. When clk is ‘high’, “tr2” and “tr4” turns on. This is the called the propagation delay of the flip flop and is. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay:

From www.numerade.com

SOLVED Consider the counter with parallelload capability in Fig. 5.24 Clock To Q Propagation Delay T ccq time after clock edge that q might be unstable (i.e., start changing) ii. When clk is ‘high’, “tr2” and “tr4” turns on. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: This is the called the propagation delay of the flip flop and is. The. Clock To Q Propagation Delay.

From www.numerade.com

SOLVED 20 Bonus Points) You are designing an adder for the blindingly Clock To Q Propagation Delay T pcq time after clock. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. This is the called the propagation delay of the. Clock To Q Propagation Delay.

From www.chegg.com

Solved A. 2 In th Tigure A.1 show function The tions s an Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the. Clock To Q Propagation Delay.

From www.pldworld.info

Clock to Q Propagation Delay Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the. Clock To Q Propagation Delay.

From www.numerade.com

Given the circuit in Figure 1, each 2input OR gate has a propagation Clock To Q Propagation Delay This is the called the propagation delay of the flip flop and is. T pcq time after clock. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. When clk is ‘high’, “tr2” and “tr4” turns on. T ccq time after clock edge that q might. Clock To Q Propagation Delay.

From www.youtube.com

Setup Time and Hold Time of Flip Flop Explained Digital Electronics Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T pcq time after clock. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. This is the called. Clock To Q Propagation Delay.

From www.chegg.com

Solved Consider the following circuit clk With these timing Clock To Q Propagation Delay T ccq time after clock edge that q might be unstable (i.e., start changing) ii. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: T pcq time after clock. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative. Clock To Q Propagation Delay.

From www.chegg.com

Solved a. (20 points) Figure 3 shows a schematic for a Clock To Q Propagation Delay T pcq time after clock. This is the called the propagation delay of the flip flop and is. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. The propagation delay of the flip flops means a small delay occurs between the clock. Clock To Q Propagation Delay.

From www.slideserve.com

PPT Overview PowerPoint Presentation, free download ID6010473 Clock To Q Propagation Delay T ccq time after clock edge that q might be unstable (i.e., start changing) ii. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming. Clock To Q Propagation Delay.

From www.chegg.com

Solved In the following circuit, the XOR gate has a delay in Clock To Q Propagation Delay T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq time after clock. This is the called the propagation delay of the flip flop and is. When clk is. Clock To Q Propagation Delay.

From www.chegg.com

Solved Each twoinput XOR gate has a propagation delay of Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. This is the called the propagation delay of the. Clock To Q Propagation Delay.

From www.birthofasynth.com

SM2010 System Clock Clock To Q Propagation Delay When clk is ‘high’, “tr2” and “tr4” turns on. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is. Clock To Q Propagation Delay.

From fadil-1.github.io

Permanent Clock Clock To Q Propagation Delay The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq time after clock. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: When clk is ‘high’, “tr2” and “tr4” turns on.. Clock To Q Propagation Delay.

From slideplayer.com

Registers and clocking issues ppt download Clock To Q Propagation Delay T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq time after clock. When clk is ‘high’, “tr2” and “tr4” turns on.. Clock To Q Propagation Delay.

From fadil-1.github.io

Permanent Clock Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T pcq time after clock. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq = time. Clock To Q Propagation Delay.

From www.chegg.com

Solved (3 Pts) Clock, And S, R Waveforms Are Shown Below Clock To Q Propagation Delay T pcq time after clock. This is the called the propagation delay of the flip flop and is. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. When clk is ‘high’, “tr2” and “tr4” turns on. Hence, input ‘qm’ (which is ‘d’ input from previous. Clock To Q Propagation Delay.

From www.numerade.com

The shift register shown below is intended to generate a copy of the Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. When clk is ‘high’, “tr2” and “tr4” turns on. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a. Clock To Q Propagation Delay.

From www.chegg.com

Question 25 Parameter Value clock to a contamination Clock To Q Propagation Delay T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: T ccq time after clock edge that q might be unstable (i.e., start changing) ii. T pcq time after clock. The propagation delay of the flip flops means a small delay occurs between the clock edge and the. Clock To Q Propagation Delay.

From www.chegg.com

Question 25 Parameter Value clock to a contamination Clock To Q Propagation Delay T ccq time after clock edge that q might be unstable (i.e., start changing) ii. This is the called the propagation delay of the flip flop and is. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq time after clock. Hence, input ‘qm’. Clock To Q Propagation Delay.

From www.numerade.com

SOLVED A 16input priority encoder can be built with four 4input Clock To Q Propagation Delay T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: T pcq time after clock. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the. Clock To Q Propagation Delay.

From www.chegg.com

Solved La 1 JO 아 Cik • DFF timing parameters setup and Clock To Q Propagation Delay This is the called the propagation delay of the flip flop and is. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: Hence,. Clock To Q Propagation Delay.

From www.numerade.com

SOLVED You are designing an adder for a fast 2bit processor. The Clock To Q Propagation Delay The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T ccq time after clock edge that q might. Clock To Q Propagation Delay.

From www.chegg.com

Assume a register clocktoQ propagation delay of Clock To Q Propagation Delay The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. This is the called the propagation delay of the flip flop and is. T pcq time after clock. When clk is ‘high’, “tr2” and “tr4” turns on. T ccq time after clock edge that q might. Clock To Q Propagation Delay.

From www.chegg.com

1. Given the circuit in Figure 1, each twoinput XOR Clock To Q Propagation Delay When clk is ‘high’, “tr2” and “tr4” turns on. T pcq time after clock. This is the called the propagation delay of the flip flop and is. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to. Clock To Q Propagation Delay.

From www.numerade.com

SOLVED The figure below shows a timing diagram for a pipeline stage Clock To Q Propagation Delay The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. T pcq time after clock. This is the called the propagation delay of the flip flop and is. Hence, input ‘qm’. Clock To Q Propagation Delay.

From slideplayer.com

Sequential Logic & FPGAs. ppt download Clock To Q Propagation Delay T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid. T ccq time after clock edge that q might be unstable (i.e., start changing). Clock To Q Propagation Delay.

From www.chegg.com

(c) Consider the circuit shown below. Let the Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. This is the called the propagation delay of the flip flop and is. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing). Clock To Q Propagation Delay.

From www.electroniclinic.com

Synchronous Counter in Digital Electronics with circuit Diagram Clock To Q Propagation Delay T pcq time after clock. This is the called the propagation delay of the flip flop and is. When clk is ‘high’, “tr2” and “tr4” turns on. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk). Clock To Q Propagation Delay.

From www.bartleby.com

Answered Clock, S, R and clear waveforms are… bartleby Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. When clk is ‘high’, “tr2” and “tr4” turns on. T pcq time after clock. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of. Clock To Q Propagation Delay.

From www.chegg.com

Solved Q1. In the following circuit each flipflop has 1. Clock To Q Propagation Delay T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: T pcq time after clock. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the. Clock To Q Propagation Delay.

From www.slideserve.com

PPT Chapter 07 Electronic Analysis of CMOS Logic Gates PowerPoint Clock To Q Propagation Delay When clk is ‘high’, “tr2” and “tr4” turns on. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: This is the called the propagation delay of the flip flop and is. Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’. Clock To Q Propagation Delay.

From www.oreilly.com

4. Sequential Logic Learning FPGAs [Book] Clock To Q Propagation Delay T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: When clk is ‘high’, “tr2” and “tr4” turns on. T pcq time after clock. The propagation delay of the flip flops means a small delay occurs between the clock edge and the flip flop output, q, becoming valid.. Clock To Q Propagation Delay.

From www.numerade.com

SOLVED A circuit implementation of a frequency divider is shown in the Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. When clk is ‘high’, “tr2” and “tr4” turns on. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: This is. Clock To Q Propagation Delay.

From www.chegg.com

f 0.3ns and a setup time ster has a clocktoQ Clock To Q Propagation Delay T ccq time after clock edge that q might be unstable (i.e., start changing) ii. This is the called the propagation delay of the flip flop and is. T pcq time after clock. T pcq = time after clock edge that the output q is guaranteed to be stable (i.e., to stop changing) contamination delay: The propagation delay of the. Clock To Q Propagation Delay.

From www.chegg.com

Label setup time, hold time, clocktoQ propagation Clock To Q Propagation Delay Hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the. T ccq time after clock edge that q might be unstable (i.e., start changing) ii. The propagation delay of the flip flops means a small delay occurs between the clock edge and the. Clock To Q Propagation Delay.