Verilog Clock Generator Task . A more typical way to generate your clock is this: Then it represents a clock oscillator on a board (the. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I want a clock of time period 10. See simulations and testbench examples for. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. I tested it on eda playground and it works fine,. I am trying to write a task that generates two clock signals, below is my code. Always #20 clk = ~clk; Put the clock generator in a module with one output port, and. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. It's a lot simpler to use a clock module that generates the clock. Actually, though, your original code might work. For implementing that i have done something. Change the duty cycle of the clock to 60/40 (2ns high/3ns low).

from www.slideserve.com

It's a lot simpler to use a clock module that generates the clock. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). See simulations and testbench examples for. Actually, though, your original code might work. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I am implementing a sequential circuit in verilog. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Then it represents a clock oscillator on a board (the. A more typical way to generate your clock is this: Always #20 clk = ~clk;

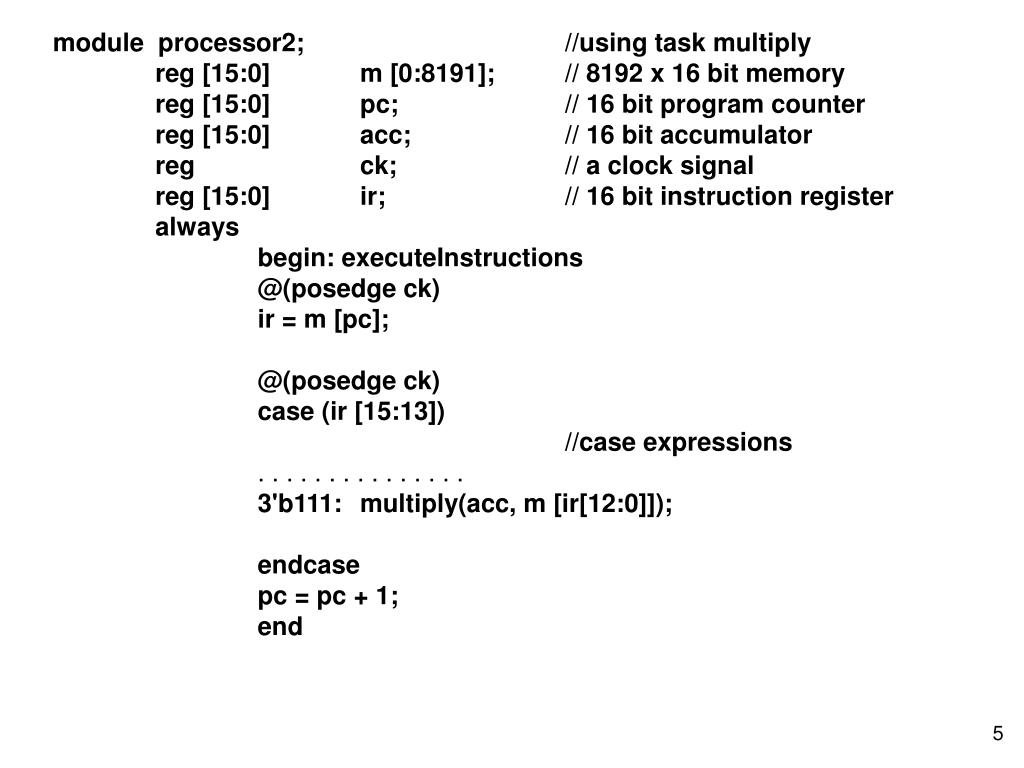

PPT Verilog Function, Task PowerPoint Presentation, free download

Verilog Clock Generator Task I tested it on eda playground and it works fine,. A more typical way to generate your clock is this: I want a clock of time period 10. I am implementing a sequential circuit in verilog. It's a lot simpler to use a clock module that generates the clock. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. Actually, though, your original code might work. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Put the clock generator in a module with one output port, and. Then it represents a clock oscillator on a board (the. I am trying to write a task that generates two clock signals, below is my code. See simulations and testbench examples for. For implementing that i have done something. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). I tested it on eda playground and it works fine,.

From www.slideserve.com

PPT Verilog Function, Task PowerPoint Presentation, free download Verilog Clock Generator Task See simulations and testbench examples for. Actually, though, your original code might work. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. It's a lot simpler to use a clock module that generates the clock. I am implementing a sequential circuit in verilog. Put the clock generator in a module with. Verilog Clock Generator Task.

From www.youtube.com

System Verilog Interview Question Write a task to generate a clock Verilog Clock Generator Task Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. For implementing that i have done something. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Then it represents a clock oscillator on a board (the. Actually, though, your original. Verilog Clock Generator Task.

From vir-us.tistory.com

[Verilog] Clock generator Verilog Clock Generator Task See simulations and testbench examples for. I am implementing a sequential circuit in verilog. Then it represents a clock oscillator on a board (the. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I tested it on eda playground and it works fine,. Always #20 clk = ~clk;. Verilog Clock Generator Task.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 09 Function and Task YouTube Verilog Clock Generator Task It's a lot simpler to use a clock module that generates the clock. See simulations and testbench examples for. I am implementing a sequential circuit in verilog. Always #20 clk = ~clk; Actually, though, your original code might work. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the. Verilog Clock Generator Task.

From www.chegg.com

Solved I need only the (verilog code) for clock module and Verilog Clock Generator Task See simulations and testbench examples for. It's a lot simpler to use a clock module that generates the clock. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. I want a clock of time period 10. For implementing that i have done something. I have used following code to generate clock. Verilog Clock Generator Task.

From www.electronicsforu.com

Software Project Clock Generator Using Verilog Modelsim Verilog Clock Generator Task I am implementing a sequential circuit in verilog. Then it represents a clock oscillator on a board (the. Put the clock generator in a module with one output port, and. I want a clock of time period 10. I am trying to write a task that generates two clock signals, below is my code. For implementing that i have done. Verilog Clock Generator Task.

From www.slideserve.com

PPT SystemVerilog basics PowerPoint Presentation, free download ID Verilog Clock Generator Task A more typical way to generate your clock is this: Always #20 clk = ~clk; I am trying to write a task that generates two clock signals, below is my code. Actually, though, your original code might work. See simulations and testbench examples for. Then it represents a clock oscillator on a board (the. In verilog, a clock generator is. Verilog Clock Generator Task.

From www.chegg.com

Solved Type up Verilog Verilog program and also create test Verilog Clock Generator Task Change the duty cycle of the clock to 60/40 (2ns high/3ns low). A more typical way to generate your clock is this: I am implementing a sequential circuit in verilog. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Learn how to create a clock generator module. Verilog Clock Generator Task.

From www.youtube.com

25 Verilog Clock Divider YouTube Verilog Clock Generator Task I want a clock of time period 10. For implementing that i have done something. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. Always #20 clk = ~clk; Put the clock generator in a module with one output port, and. I am implementing a sequential circuit in verilog. In verilog,. Verilog Clock Generator Task.

From www.youtube.com

21 Verilog Clock Generator YouTube Verilog Clock Generator Task Then it represents a clock oscillator on a board (the. For implementing that i have done something. I want a clock of time period 10. Put the clock generator in a module with one output port, and. Actually, though, your original code might work. I am trying to write a task that generates two clock signals, below is my code.. Verilog Clock Generator Task.

From www.allaboutcircuits.com

Creating Finite State Machines in Verilog Technical Articles Verilog Clock Generator Task Then it represents a clock oscillator on a board (the. For implementing that i have done something. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. It's a lot. Verilog Clock Generator Task.

From www.youtube.com

How to generate clock in Verilog HDL YouTube Verilog Clock Generator Task For implementing that i have done something. Then it represents a clock oscillator on a board (the. See simulations and testbench examples for. Always #20 clk = ~clk; I want a clock of time period 10. Put the clock generator in a module with one output port, and. Actually, though, your original code might work. It's a lot simpler to. Verilog Clock Generator Task.

From blog.csdn.net

Verilog基础:task和function的使用(一)_verilog taskCSDN博客 Verilog Clock Generator Task Always #20 clk = ~clk; I tested it on eda playground and it works fine,. I want a clock of time period 10. A more typical way to generate your clock is this: Change the duty cycle of the clock to 60/40 (2ns high/3ns low). Actually, though, your original code might work. Then it represents a clock oscillator on a. Verilog Clock Generator Task.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Verilog Clock Generator Task I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. A more typical way to generate your clock is this: Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. It's a lot simpler to use a clock module that. Verilog Clock Generator Task.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5709023 Verilog Clock Generator Task I am implementing a sequential circuit in verilog. I want a clock of time period 10. Then it represents a clock oscillator on a board (the. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. In verilog, a clock generator is a module or block of code that produces clock signals. Verilog Clock Generator Task.

From fercow.weebly.com

Clock divider mux verilog fercow Verilog Clock Generator Task Actually, though, your original code might work. Then it represents a clock oscillator on a board (the. I am trying to write a task that generates two clock signals, below is my code. Put the clock generator in a module with one output port, and. A more typical way to generate your clock is this: Learn how to create a. Verilog Clock Generator Task.

From www.youtube.com

Posedge detector using Verilog task YouTube Verilog Clock Generator Task It's a lot simpler to use a clock module that generates the clock. Put the clock generator in a module with one output port, and. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). For implementing that i have done something. Actually, though, your original code might work. I am implementing a sequential circuit in verilog. I. Verilog Clock Generator Task.

From www.youtube.com

23. Verilog HDL System Task and Compiler Directives YouTube Verilog Clock Generator Task I am implementing a sequential circuit in verilog. It's a lot simpler to use a clock module that generates the clock. I tested it on eda playground and it works fine,. Always #20 clk = ~clk; In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I am trying. Verilog Clock Generator Task.

From exojsfvro.blob.core.windows.net

Generating Clock In Verilog at John Saunders blog Verilog Clock Generator Task Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. I am implementing a sequential circuit in verilog. It's a lot simpler to use a clock module that generates the clock. I am trying to write a task that generates two clock signals, below is my code. A more typical way to. Verilog Clock Generator Task.

From www.youtube.com

How to generate clock in Verilog HDL Verilog code of clock generator Verilog Clock Generator Task I am trying to write a task that generates two clock signals, below is my code. I tested it on eda playground and it works fine,. Then it represents a clock oscillator on a board (the. Actually, though, your original code might work. I am implementing a sequential circuit in verilog. Learn how to create a clock generator module in. Verilog Clock Generator Task.

From www.chegg.com

Solved Create a clock generator module with Verilog which Verilog Clock Generator Task Always #20 clk = ~clk; I tested it on eda playground and it works fine,. I am trying to write a task that generates two clock signals, below is my code. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. See simulations and testbench examples for. A more. Verilog Clock Generator Task.

From www.shuzhiduo.com

verilog之task用法实例 Verilog Clock Generator Task I want a clock of time period 10. I tested it on eda playground and it works fine,. For implementing that i have done something. I am implementing a sequential circuit in verilog. I am trying to write a task that generates two clock signals, below is my code. Put the clock generator in a module with one output port,. Verilog Clock Generator Task.

From www.youtube.com

5 Ways To Generate Clock Signal In Verilog YouTube Verilog Clock Generator Task See simulations and testbench examples for. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). Actually, though, your original code might work. I am trying to write a task that generates two clock signals, below is my code. It's a lot simpler to use a clock module that generates the clock. In verilog, a clock generator is. Verilog Clock Generator Task.

From diagrampartunimparted.z21.web.core.windows.net

System Verilog Tutorial For Beginners Pdf Verilog Clock Generator Task Actually, though, your original code might work. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I want a clock of time period 10. I tested it on eda playground and it works fine,. For implementing. Verilog Clock Generator Task.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Verilog Clock Generator Task I want a clock of time period 10. Then it represents a clock oscillator on a board (the. Put the clock generator in a module with one output port, and. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. For implementing that i have done something. See. Verilog Clock Generator Task.

From www.chegg.com

Solved Create a clock generator module with Verilog which Verilog Clock Generator Task A more typical way to generate your clock is this: Actually, though, your original code might work. Put the clock generator in a module with one output port, and. I tested it on eda playground and it works fine,. Then it represents a clock oscillator on a board (the. I am trying to write a task that generates two clock. Verilog Clock Generator Task.

From www.slideserve.com

PPT Verilog 2 Design Examples PowerPoint Presentation, free Verilog Clock Generator Task I want a clock of time period 10. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I tested it on eda playground and it works fine,. See simulations and testbench examples for. I am trying to write a task that generates two clock signals, below is my. Verilog Clock Generator Task.

From www.researchgate.net

a Structure of the Clock selector. b PLL and clock controller Verilog Verilog Clock Generator Task For implementing that i have done something. It's a lot simpler to use a clock module that generates the clock. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. A more typical way to generate your clock is this: Put the clock generator in a module with. Verilog Clock Generator Task.

From poe.com

What is the method for generating a 100MHz clock in Verilog? Poe Verilog Clock Generator Task I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. A more typical way to generate your clock is this: I am trying to write a task that generates two clock signals, below is my code. Actually, though, your original code might work. I am implementing a sequential. Verilog Clock Generator Task.

From www.youtube.com

Verilog Code of Clock Generator with TB to generate CLK with Varying Verilog Clock Generator Task I am trying to write a task that generates two clock signals, below is my code. I want a clock of time period 10. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. For implementing that i have done something. I tested it on eda playground and it. Verilog Clock Generator Task.

From www.youtube.com

Mastering Verilog Code Essential VCD File Tasks EP20 YouTube Verilog Clock Generator Task In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. See simulations and testbench examples for. Always #20 clk = ~clk; Then it represents a clock oscillator on a board (the. Actually, though, your original code might work. Put the clock generator in a module with one output port,. Verilog Clock Generator Task.

From www.chegg.com

I need help setting up a system Verilog code for the Verilog Clock Generator Task Then it represents a clock oscillator on a board (the. Actually, though, your original code might work. See simulations and testbench examples for. It's a lot simpler to use a clock module that generates the clock. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). In verilog, a clock generator is a module or block of code. Verilog Clock Generator Task.

From www.researchgate.net

Figure A5. VerilogA code of the clock amplitudebased control Verilog Clock Generator Task For implementing that i have done something. Actually, though, your original code might work. See simulations and testbench examples for. Always #20 clk = ~clk; Put the clock generator in a module with one output port, and. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Change the. Verilog Clock Generator Task.

From blog.csdn.net

verilog GATED_CLOCK_gated clock rtlCSDN博客 Verilog Clock Generator Task I am trying to write a task that generates two clock signals, below is my code. Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. For implementing that i. Verilog Clock Generator Task.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube Verilog Clock Generator Task Learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. I want a clock of time period 10. For implementing that i have done something. Change the duty cycle of the clock to 60/40 (2ns high/3ns low). Put the clock generator in a module with one output port, and. In verilog, a. Verilog Clock Generator Task.