Define In Makefile . In the vast majority of cases, c or c++ files are compiled. These values are substituted by explicit. Let's say you want a replacement for #define mydef. These values are substituted by explicit. Most often, the makefile tells make how to compile and link a program. These values are substituted by explicit. But the newlines that separate the lines of the value in a define become part of. A variable is a name defined in a makefile to represent a string of text, called the variable's value. Tell make to export all. Other languages typically have their own tools. Makefiles are used to help decide which parts of a large program need to be recompiled. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. In your makefile you have the compiler command line, something like. Define a variable, overriding any previous definition, even one from the command line. The value in an ordinary assignment cannot contain a newline;

from diamantidis.github.io

In your makefile you have the compiler command line, something like. Makefiles are used to help decide which parts of a large program need to be recompiled. These values are substituted by explicit. These values are substituted by explicit. Let's say you want a replacement for #define mydef. A variable is a name defined in a makefile to represent a string of text, called the variable's value. Other languages typically have their own tools. But the newlines that separate the lines of the value in a define become part of. These values are substituted by explicit. Define a variable, overriding any previous definition, even one from the command line.

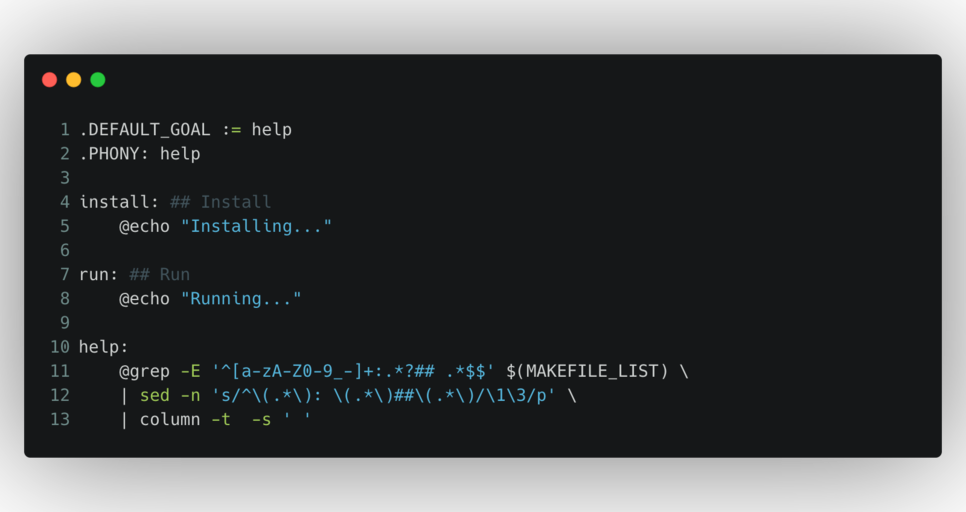

How to list all the targets on a Makefile

Define In Makefile Other languages typically have their own tools. These values are substituted by explicit. Makefiles are used to help decide which parts of a large program need to be recompiled. In your makefile you have the compiler command line, something like. Most often, the makefile tells make how to compile and link a program. These values are substituted by explicit. You need a file called a makefile to tell make what to do. Tell make to export all. But the newlines that separate the lines of the value in a define become part of. Other languages typically have their own tools. In the vast majority of cases, c or c++ files are compiled. Let's say you want a replacement for #define mydef. These values are substituted by explicit. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. The value in an ordinary assignment cannot contain a newline; Define a variable, overriding any previous definition, even one from the command line.

From www.slideserve.com

PPT Makefiles PowerPoint Presentation, free download ID5930 Define In Makefile Let's say you want a replacement for #define mydef. But the newlines that separate the lines of the value in a define become part of. In your makefile you have the compiler command line, something like. The value in an ordinary assignment cannot contain a newline; In the vast majority of cases, c or c++ files are compiled. Other languages. Define In Makefile.

From www.youtube.com

Makefile Variables Are Complicated Makefile assignment tutorial YouTube Define In Makefile These values are substituted by explicit. Define a variable, overriding any previous definition, even one from the command line. These values are substituted by explicit. In the vast majority of cases, c or c++ files are compiled. You need a file called a makefile to tell make what to do. Other languages typically have their own tools. A variable is. Define In Makefile.

From malithjayaweera.com

How to Write a Makefile with Ease Malith's Perspective Define In Makefile In the vast majority of cases, c or c++ files are compiled. Define a variable, overriding any previous definition, even one from the command line. Other languages typically have their own tools. But the newlines that separate the lines of the value in a define become part of. You need a file called a makefile to tell make what to. Define In Makefile.

From plugins.jetbrains.com

Makefile Language IntelliJ IDEs Plugin Marketplace Define In Makefile In your makefile you have the compiler command line, something like. Let's say you want a replacement for #define mydef. These values are substituted by explicit. Tell make to export all. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. Makefiles are used to help decide which parts of a. Define In Makefile.

From www.codemii.com

Tutorial 2 Makefiles, basics of C, compiling source code and dealing Define In Makefile These values are substituted by explicit. Makefiles are used to help decide which parts of a large program need to be recompiled. A variable is a name defined in a makefile to represent a string of text, called the variable's value. The value in an ordinary assignment cannot contain a newline; Most often, the makefile tells make how to compile. Define In Makefile.

From bytexd.com

How to Use make and makefile in Linux ByteXD Define In Makefile In your makefile you have the compiler command line, something like. Most often, the makefile tells make how to compile and link a program. But the newlines that separate the lines of the value in a define become part of. In the vast majority of cases, c or c++ files are compiled. These values are substituted by explicit. These values. Define In Makefile.

From earthly.dev

Building in Visual Studio Code with a Makefile Earthly Blog Define In Makefile But the newlines that separate the lines of the value in a define become part of. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. Let's say you want a replacement for #define mydef. These values are substituted by explicit. Most often, the makefile tells make how to compile and. Define In Makefile.

From www.youtube.com

How to create a simple Makefile YouTube Define In Makefile Define a variable, overriding any previous definition, even one from the command line. But the newlines that separate the lines of the value in a define become part of. A variable is a name defined in a makefile to represent a string of text, called the variable's value. A variable is a name defined in a makefile to represent a. Define In Makefile.

From noahloomans.com

Makefile tutorial 2.0 Noah Loomans Define In Makefile These values are substituted by explicit. But the newlines that separate the lines of the value in a define become part of. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. These values are substituted by explicit. In the vast majority of cases, c or c++ files are compiled. Define. Define In Makefile.

From www.slideserve.com

PPT Makefiles PowerPoint Presentation, free download ID5930 Define In Makefile In the vast majority of cases, c or c++ files are compiled. These values are substituted by explicit. Most often, the makefile tells make how to compile and link a program. A variable is a name defined in a makefile to represent a string of text, called the variable's value. But the newlines that separate the lines of the value. Define In Makefile.

From www.technicalfeeder.com

Makefile How to use variables defined in a config file Technical Feeder Define In Makefile But the newlines that separate the lines of the value in a define become part of. In the vast majority of cases, c or c++ files are compiled. A variable is a name defined in a makefile to represent a string of text, called the variable's value. These values are substituted by explicit. In your makefile you have the compiler. Define In Makefile.

From www.youtube.com

C++ How to define C++ preprocessor variable in Makefile YouTube Define In Makefile These values are substituted by explicit. Other languages typically have their own tools. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. These values are substituted by explicit. You need a. Define In Makefile.

From www.slideserve.com

PPT Compilation and Makefiles PowerPoint Presentation, free download Define In Makefile Most often, the makefile tells make how to compile and link a program. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. These values are substituted by explicit. Tell make to. Define In Makefile.

From www.youtube.com

How to Create a Simple Makefile Introduction to Makefiles YouTube Define In Makefile These values are substituted by explicit. These values are substituted by explicit. Tell make to export all. Most often, the makefile tells make how to compile and link a program. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. Let's say you want a replacement for #define mydef. These values. Define In Makefile.

From data-flair.training

Makefile in linux DataFlair Define In Makefile These values are substituted by explicit. Other languages typically have their own tools. But the newlines that separate the lines of the value in a define become part of. Tell make to export all. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. A variable is a name defined in. Define In Makefile.

From nerdyelectronics.com

Makefile and how it works NerdyElectronics Define In Makefile In the vast majority of cases, c or c++ files are compiled. Makefiles are used to help decide which parts of a large program need to be recompiled. Define a variable, overriding any previous definition, even one from the command line. You need a file called a makefile to tell make what to do. A variable is a name defined. Define In Makefile.

From www.slideserve.com

PPT Makefiles PowerPoint Presentation, free download ID5930 Define In Makefile Makefiles are used to help decide which parts of a large program need to be recompiled. A variable is a name defined in a makefile to represent a string of text, called the variable's value. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. You need a file called a. Define In Makefile.

From www.jetbrains.com

Makefile projects CLion Documentation Define In Makefile The value in an ordinary assignment cannot contain a newline; Other languages typically have their own tools. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. But the newlines that separate the lines of the value in a define become part of. A variable is a name defined in a. Define In Makefile.

From www.slideserve.com

PPT Makefile Brief Reference PowerPoint Presentation, free download Define In Makefile These values are substituted by explicit. Let's say you want a replacement for #define mydef. Other languages typically have their own tools. But the newlines that separate the lines of the value in a define become part of. Define a variable, overriding any previous definition, even one from the command line. A variable is a name defined in a makefile. Define In Makefile.

From medium.com

Why You Need a Makefile in Your Project by Andrew GrahamYooll Define In Makefile Makefiles are used to help decide which parts of a large program need to be recompiled. The value in an ordinary assignment cannot contain a newline; These values are substituted by explicit. Let's say you want a replacement for #define mydef. These values are substituted by explicit. Define a variable, overriding any previous definition, even one from the command line.. Define In Makefile.

From diamantidis.github.io

How to list all the targets on a Makefile Define In Makefile Makefiles are used to help decide which parts of a large program need to be recompiled. Most often, the makefile tells make how to compile and link a program. Define a variable, overriding any previous definition, even one from the command line. These values are substituted by explicit. But the newlines that separate the lines of the value in a. Define In Makefile.

From www.slideserve.com

PPT The Makefile Utility PowerPoint Presentation, free download ID Define In Makefile In the vast majority of cases, c or c++ files are compiled. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. Other languages typically have their own tools. A variable is a name defined in a makefile to represent a string of text, called the variable's value. These values are. Define In Makefile.

From www.youtube.com

How to create a MakeFile in Linux? YouTube Define In Makefile These values are substituted by explicit. A variable is a name defined in a makefile to represent a string of text, called the variable's value. But the newlines that separate the lines of the value in a define become part of. These values are substituted by explicit. You need a file called a makefile to tell make what to do.. Define In Makefile.

From blog.csdn.net

Makefile:使用函数_makefile defineCSDN博客 Define In Makefile Define a variable, overriding any previous definition, even one from the command line. Other languages typically have their own tools. These values are substituted by explicit. The value in an ordinary assignment cannot contain a newline; A variable is a name defined in a makefile to represent a string of text, called the variable’s value. In your makefile you have. Define In Makefile.

From stacktuts.com

How to define several include path in makefile? StackTuts Define In Makefile Makefiles are used to help decide which parts of a large program need to be recompiled. Define a variable, overriding any previous definition, even one from the command line. The value in an ordinary assignment cannot contain a newline; A variable is a name defined in a makefile to represent a string of text, called the variable’s value. Other languages. Define In Makefile.

From cselectricalandelectronics.com

How To Create Multiple Files And Makefile In VS Code On Windows Define In Makefile These values are substituted by explicit. The value in an ordinary assignment cannot contain a newline; You need a file called a makefile to tell make what to do. Makefiles are used to help decide which parts of a large program need to be recompiled. In your makefile you have the compiler command line, something like. Other languages typically have. Define In Makefile.

From www.codeproject.com

Makefiles in Linux An Overview CodeProject Define In Makefile Tell make to export all. In the vast majority of cases, c or c++ files are compiled. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. These values are substituted by explicit. Define a variable, overriding any previous definition, even one from the command line. Other languages typically have their. Define In Makefile.

From www.slideserve.com

PPT Makefile Tutorial CIS5027 PowerPoint Presentation, free download Define In Makefile You need a file called a makefile to tell make what to do. In the vast majority of cases, c or c++ files are compiled. These values are substituted by explicit. Most often, the makefile tells make how to compile and link a program. The value in an ordinary assignment cannot contain a newline; In your makefile you have the. Define In Makefile.

From mropengate.blogspot.com

簡單學 makefile:makefile 介紹與範例程式 Mr. Opengate Define In Makefile A variable is a name defined in a makefile to represent a string of text, called the variable’s value. In your makefile you have the compiler command line, something like. These values are substituted by explicit. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. In the vast majority of. Define In Makefile.

From www.slideserve.com

PPT The Makefile Utility PowerPoint Presentation, free download ID Define In Makefile In your makefile you have the compiler command line, something like. Define a variable, overriding any previous definition, even one from the command line. A variable is a name defined in a makefile to represent a string of text, called the variable's value. Most often, the makefile tells make how to compile and link a program. Makefiles are used to. Define In Makefile.

From www.youtube.com

How to create a Makefile (C/C++)? Makefile Tutorial Linux YouTube Define In Makefile Define a variable, overriding any previous definition, even one from the command line. A variable is a name defined in a makefile to represent a string of text, called the variable’s value. Other languages typically have their own tools. These values are substituted by explicit. In the vast majority of cases, c or c++ files are compiled. A variable is. Define In Makefile.

From www.youtube.com

7. Makefiles Part 1 Introduction to Embedded Systems Software and Define In Makefile These values are substituted by explicit. These values are substituted by explicit. But the newlines that separate the lines of the value in a define become part of. Other languages typically have their own tools. In your makefile you have the compiler command line, something like. A variable is a name defined in a makefile to represent a string of. Define In Makefile.

From tbekk.com

Visual Studio Code now supports Makefile DevStream Define In Makefile Most often, the makefile tells make how to compile and link a program. These values are substituted by explicit. Makefiles are used to help decide which parts of a large program need to be recompiled. In your makefile you have the compiler command line, something like. These values are substituted by explicit. In the vast majority of cases, c or. Define In Makefile.

From www.codeproject.com

Makefiles in Linux An Overview CodeProject Define In Makefile These values are substituted by explicit. In the vast majority of cases, c or c++ files are compiled. In your makefile you have the compiler command line, something like. But the newlines that separate the lines of the value in a define become part of. Tell make to export all. Other languages typically have their own tools. These values are. Define In Makefile.