Union Example In Sv . The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Typedef union { bit[15:0] salary; Union {list of elements} union_name. When unions are declared the memory is. There are three types of unions in systemverilog: For instance, a variable point can. Unions are like structures, but in a union, we can only access one element at a time. Unpacked unions, packed unions, and tagged unions. You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. Output:# the below figure shows the output of unpacked union.

from saylordotorg.github.io

Unions are like structures, but in a union, we can only access one element at a time. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Unpacked unions, packed unions, and tagged unions. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. For instance, a variable point can. There are three types of unions in systemverilog: You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. Union {list of elements} union_name. Typedef union { bit[15:0] salary; Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code.

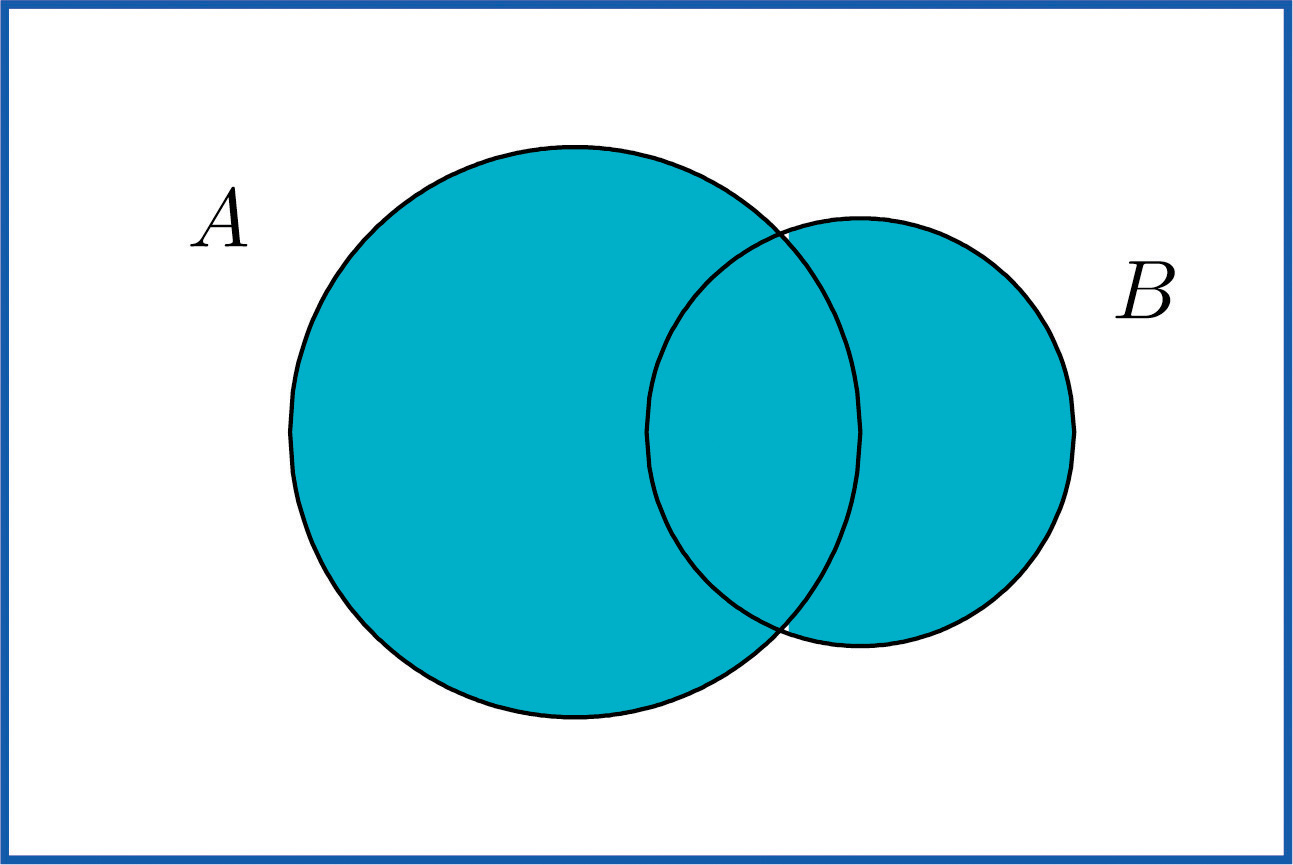

Complements, Intersections, and Unions

Union Example In Sv For instance, a variable point can. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Typedef union { bit[15:0] salary; Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. For instance, a variable point can. Union {list of elements} union_name. There are three types of unions in systemverilog: When unions are declared the memory is. Unpacked unions, packed unions, and tagged unions. You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. Unions are like structures, but in a union, we can only access one element at a time. Output:# the below figure shows the output of unpacked union.

From www.scribd.com

Sv Agreement Module Grammatical Number Plural Union Example In Sv Union {list of elements} union_name. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Output:# the below figure shows the output of unpacked union. Unpacked unions, packed unions,. Union Example In Sv.

From marketbusinessnews.com

What is a union? Definition and examples Market Business News Union Example In Sv Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Unpacked unions, packed unions, and tagged unions. For instance, a variable point can. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Output:# the below figure. Union Example In Sv.

From www.youtube.com

SQL Union Tutorial with Example (UNION ALL) YouTube Union Example In Sv Typedef union { bit[15:0] salary; Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. There are three types of unions in systemverilog: Union {list of elements} union_name. Unpacked unions, packed unions, and tagged unions. Unions are like structures, but in a union, we can only access one element at a time. You. Union Example In Sv.

From www.youtube.com

How to find the union and intersection of two sets YouTube Union Example In Sv The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. For instance, a variable point can. Typedef union { bit[15:0] salary; Output:# the below figure shows the output of unpacked union. There are three types of unions in systemverilog: Unions are like structures, but in a. Union Example In Sv.

From www.youtube.com

Union Rule Example (3 sets) YouTube Union Example In Sv Unions are like structures, but in a union, we can only access one element at a time. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Typedef union. Union Example In Sv.

From mavink.com

Venn Diagram Union Symbols Union Example In Sv Unpacked unions, packed unions, and tagged unions. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. For instance, a variable point can. The datatype union is. Union Example In Sv.

From www.youtube.com

Union of Sets YouTube Union Example In Sv The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. For instance, a variable point can. Union {list of elements} union_name. Unpacked unions, packed unions, and tagged unions. When unions are declared the memory is. The way this works is to declare with a typedef that. Union Example In Sv.

From www.youtube.com

Union set lesson 2 YouTube Union Example In Sv For instance, a variable point can. Unions are like structures, but in a union, we can only access one element at a time. Union {list of elements} union_name. When unions are declared the memory is. There are three types of unions in systemverilog: The datatype union is very similar to a structure, but only one of the fields will be. Union Example In Sv.

From wiringdatabaseinfo.blogspot.com

Venn Diagram Unions And Intersections Wiring Site Resource Union Example In Sv Unpacked unions, packed unions, and tagged unions. There are three types of unions in systemverilog: Typedef union { bit[15:0] salary; When unions are declared the memory is. Union {list of elements} union_name. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. The way this works. Union Example In Sv.

From learndiagram.com

Example Of Union Sets In Venn Diagram Learn Diagram Union Example In Sv You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. Unpacked unions, packed unions, and tagged unions. For instance, a variable point can. When unions are declared the memory is. There are three types of unions in systemverilog: Unions are like structures, but in a. Union Example In Sv.

From prateeksrivastav143.blogspot.com

Difference between structure and union. Prateek Srivastav Union Example In Sv Output:# the below figure shows the output of unpacked union. For instance, a variable point can. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. When unions are declared the memory is. Union {list of elements} union_name. You can think of a packed structure as. Union Example In Sv.

From www.slideserve.com

PPT Relational Algebra & Relational Calculus PowerPoint Presentation Union Example In Sv For instance, a variable point can. Output:# the below figure shows the output of unpacked union. There are three types of unions in systemverilog: You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. The datatype union is very similar to a structure, but only. Union Example In Sv.

From vohobu-marria.blogspot.com

35 venn diagram unions and intersections Diagram Resource Union Example In Sv Typedef union { bit[15:0] salary; There are three types of unions in systemverilog: For instance, a variable point can. When unions are declared the memory is. Unions are like structures, but in a union, we can only access one element at a time. The way this works is to declare with a typedef that it is a union and give. Union Example In Sv.

From saylordotorg.github.io

Complements, Intersections, and Unions Union Example In Sv Unpacked unions, packed unions, and tagged unions. There are three types of unions in systemverilog: Unions are like structures, but in a union, we can only access one element at a time. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Union {list. Union Example In Sv.

From www.someka.net

Union Venn Diagram Example [Free Template] Union Example In Sv When unions are declared the memory is. For instance, a variable point can. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. There are three types of unions in systemverilog: You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum. Union Example In Sv.

From vancexu.github.io

Intro to UnionFind Data Structure Union Example In Sv Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. When unions are declared the memory is. Union {list of elements} union_name. Output:# the below figure shows the. Union Example In Sv.

From www.qualitygurus.com

Union and Intersection in Probability Quality Gurus Union Example In Sv Output:# the below figure shows the output of unpacked union. For instance, a variable point can. Unions are like structures, but in a union, we can only access one element at a time. When unions are declared the memory is. The way this works is to declare with a typedef that it is a union and give it different identifiers. Union Example In Sv.

From 9to5answer.com

[Solved] Union of two columns in the same table 9to5Answer Union Example In Sv Unions are like structures, but in a union, we can only access one element at a time. Unpacked unions, packed unions, and tagged unions. You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. Typedef union { bit[15:0] salary; For instance, a variable point can.. Union Example In Sv.

From www.youtube.com

Graphing Unions and Intersections of Sets , Intermediate Algebra Union Example In Sv Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. When unions are declared the memory is. There are three types of unions in systemverilog: Unpacked unions, packed unions, and tagged unions. Unions are like structures, but in a union, we can only access one element at a time. For instance, a variable. Union Example In Sv.

From twinklsecondary.blog

Venn Diagram Notation Beyond GCSE Revision Union Example In Sv There are three types of unions in systemverilog: You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. Output:# the below figure shows the output of unpacked union. Typedef union { bit[15:0] salary; The way this works is to declare with a typedef that it. Union Example In Sv.

From www.tutorialgateway.org

SQL Union Operator Union Example In Sv Union {list of elements} union_name. Output:# the below figure shows the output of unpacked union. There are three types of unions in systemverilog: When unions are declared the memory is. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. For instance, a variable point can.. Union Example In Sv.

From slidetodoc.com

Basic Structures Sets Functions Sequences Sums and Matrices Union Example In Sv When unions are declared the memory is. The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Unions are like structures, but in a union, we can only access one element at a time. There are three types of unions in systemverilog: You can. Union Example In Sv.

From quyasoft.com

Union And Union All In Sql Server With Examples QuyaSoft Union Example In Sv Union {list of elements} union_name. There are three types of unions in systemverilog: When unions are declared the memory is. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of. Union Example In Sv.

From www.thedataschool.co.uk

Connecting Data Unions The Data School Union Example In Sv The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. There are three types of unions in systemverilog: For instance, a variable point can. You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum. Union Example In Sv.

From www.youtube.com

Union and intersection YouTube Union Example In Sv You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. Output:# the below figure shows the output of unpacked union. Unpacked unions, packed unions, and tagged unions. For instance, a variable point can. Union {list of elements} union_name. The datatype union is very similar to. Union Example In Sv.

From www.programiz.com

SQL UNION (With Examples) Union Example In Sv Output:# the below figure shows the output of unpacked union. When unions are declared the memory is. There are three types of unions in systemverilog: Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Typedef union { bit[15:0] salary; Unpacked unions, packed unions, and tagged unions. The way this works is to. Union Example In Sv.

From www.youtube.com

Generalized Union and Intersection YouTube Union Example In Sv The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. When unions are declared the memory is. Typedef union { bit[15:0] salary; Unpacked unions, packed unions, and tagged unions. Union {list of elements} union_name. You can think of a packed structure as an implicit. Union Example In Sv.

From www.youtube.com

Introduction to Unions in C YouTube Union Example In Sv When unions are declared the memory is. You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. There are three types of unions in systemverilog: Unpacked unions, packed unions, and tagged unions. Typedef union { bit[15:0] salary; Output:# the below figure shows the output of. Union Example In Sv.

From www.youtube.com

Algebra 3 Venn Diagrams, Unions, and Intersections YouTube Union Example In Sv Union {list of elements} union_name. Unpacked unions, packed unions, and tagged unions. Typedef union { bit[15:0] salary; The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. When unions are declared the memory is. Systemverilog struct and union are handy constructs that can encapsulate. Union Example In Sv.

From thirdspacelearning.com

Venn Diagram Union And Intersection GCSE Maths Union Example In Sv For instance, a variable point can. Union {list of elements} union_name. Unpacked unions, packed unions, and tagged unions. Typedef union { bit[15:0] salary; Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Unions are like structures, but in a union, we can only access one element at a time. When unions are. Union Example In Sv.

From www.pinterest.com

Figure 2 A Venn diagram of unions and intersections for two sets, A Union Example In Sv There are three types of unions in systemverilog: Unions are like structures, but in a union, we can only access one element at a time. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Output:# the below figure shows the output of unpacked union. Typedef union { bit[15:0] salary; Union {list of. Union Example In Sv.

From hantt.pages.labranet.jamk.fi

SQL basics 3 Databases [TTC2020] Union Example In Sv The way this works is to declare with a typedef that it is a union and give it different identifiers which you can use to refer. Union {list of elements} union_name. Unpacked unions, packed unions, and tagged unions. Output:# the below figure shows the output of unpacked union. For instance, a variable point can. Typedef union { bit[15:0] salary; There. Union Example In Sv.

From apurbasaitech.wixsite.com

Structures and Unions Union Example In Sv The datatype union is very similar to a structure, but only one of the fields will be valid at a given point of time. Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Unions are like structures, but in a union, we can only access one element at a time. Output:# the. Union Example In Sv.

From www.studypool.com

SOLUTION Difference between structure and union with examples Simple Union Example In Sv There are three types of unions in systemverilog: For instance, a variable point can. Unpacked unions, packed unions, and tagged unions. Typedef union { bit[15:0] salary; Systemverilog struct and union are handy constructs that can encapsulate data types and simplify your rtl code. Output:# the below figure shows the output of unpacked union. The way this works is to declare. Union Example In Sv.

From www.w3resource.com

SQL Union w3resource Union Example In Sv For instance, a variable point can. Unions are like structures, but in a union, we can only access one element at a time. Typedef union { bit[15:0] salary; You can think of a packed structure as an implicit packed union with a single bit vector whose length is the sum of all the. The datatype union is very similar to. Union Example In Sv.