Arm Interrupt Virtualization . The arm architecture virtualization extensions. Used to define the active and pending virtual. Arm generic interrupt controller v3 and v4 guide. Done so, you should read the learn the architecture: Arm gicv2 at a glance. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Some registers are banked per cpu (at the same memory address) distributor is the.

from microdigisoft.com

Done so, you should read the learn the architecture: Arm generic interrupt controller v3 and v4 guide. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Some registers are banked per cpu (at the same memory address) distributor is the. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Arm gicv2 at a glance. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Used to define the active and pending virtual. The arm architecture virtualization extensions.

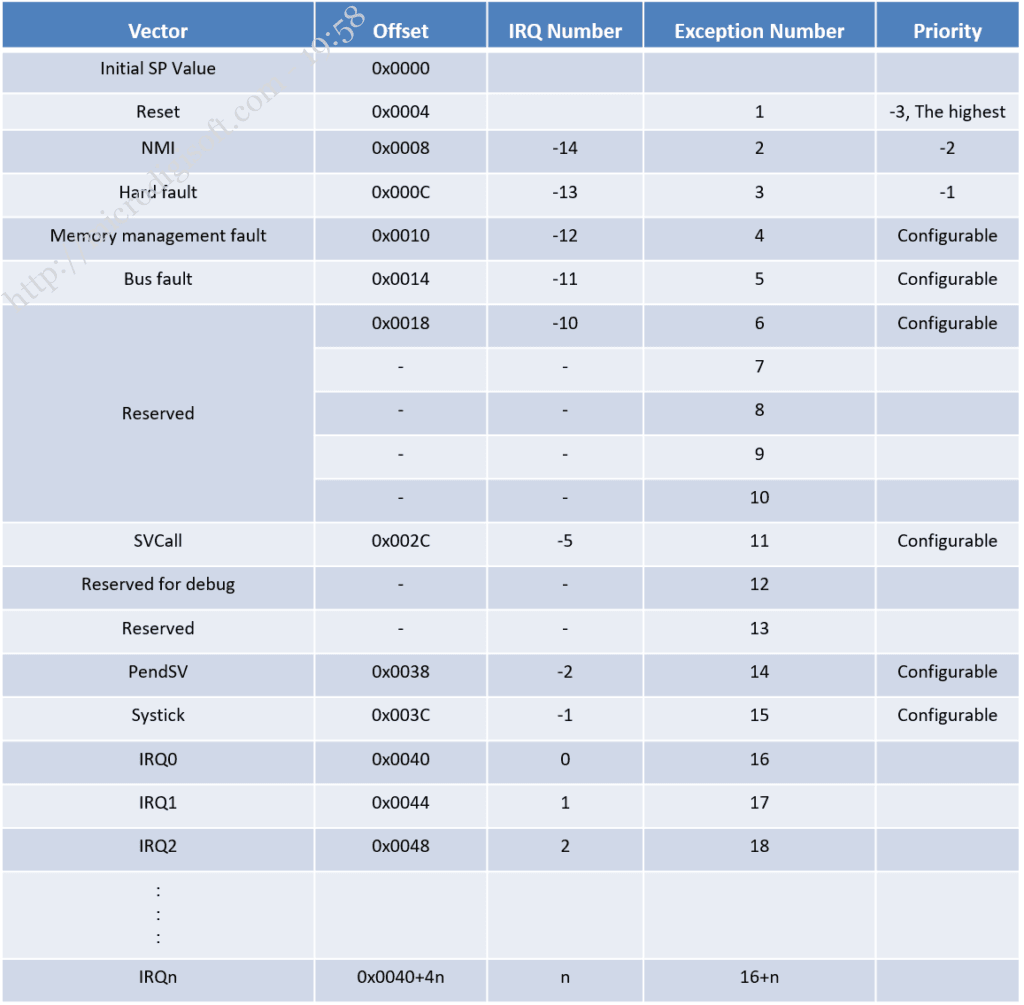

Interrupts Configuration of ARM Cortex Mx Microcontroller

Arm Interrupt Virtualization Done so, you should read the learn the architecture: The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The arm architecture virtualization extensions. Used to define the active and pending virtual. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Done so, you should read the learn the architecture: The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Some registers are banked per cpu (at the same memory address) distributor is the. Arm generic interrupt controller v3 and v4 guide. Arm gicv2 at a glance.

From electronics.stackexchange.com

arm Interrupt vector address in Program Counter? Electrical Arm Interrupt Virtualization The arm architecture virtualization extensions. Arm gicv2 at a glance. Arm generic interrupt controller v3 and v4 guide. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Used to define the active and pending virtual. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The hypervisor, or similar software, manages the. Arm Interrupt Virtualization.

From www.slideserve.com

PPT Lecture 42 ARM Interrupt PowerPoint Presentation, free download Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Used to define the active and pending virtual. Arm generic interrupt controller v3 and v4 guide. Some registers are banked per cpu (at the same memory address) distributor is the. Arm gicv2 at a glance. The hypervisor, or similar software, manages the gic. Arm Interrupt Virtualization.

From www.slideserve.com

PPT Embedded Hardware Foundation PowerPoint Presentation, free Arm Interrupt Virtualization Arm generic interrupt controller v3 and v4 guide. The arm architecture virtualization extensions. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Arm gicv2 at a glance. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Done so, you should read the learn the architecture: Some registers are banked per cpu (at the same. Arm Interrupt Virtualization.

From www.javacodegeeks.com

ARM Virtualization Extensions Memory and Interrupts (Part 2) Arm Interrupt Virtualization Used to define the active and pending virtual. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: The arm architecture virtualization extensions. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Some registers are banked per cpu (at the same memory address) distributor is the. Arm generic interrupt controller v3 and v4 guide. Done. Arm Interrupt Virtualization.

From roboticelectronics.in

ARM Interrupts ROBOTIC ELECTRONICS Arm Interrupt Virtualization The arm architecture virtualization extensions. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Arm generic interrupt controller v3 and v4 guide. Arm gicv2 at a glance. Used to define the active and pending virtual. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Some registers are banked per cpu (at. Arm Interrupt Virtualization.

From www.slideserve.com

PPT Lecture 4. ARM Instructions 1 PowerPoint Presentation, free Arm Interrupt Virtualization Arm gicv2 at a glance. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Used to define the active and pending virtual. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Arm generic interrupt controller v3 and v4 guide. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for. Arm Interrupt Virtualization.

From www.slideserve.com

PPT ARM interrupts and the VIC PowerPoint Presentation, free download Arm Interrupt Virtualization Arm generic interrupt controller v3 and v4 guide. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Used to define the active and pending virtual. Done so, you should read the learn the architecture: The arm architecture virtualization extensions. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: The generic interrupt controller (gic) enhances. Arm Interrupt Virtualization.

From virtualization-study.blogspot.com

Virtualization ARM Virtualization Extensions Arm Interrupt Virtualization Some registers are banked per cpu (at the same memory address) distributor is the. Arm gicv2 at a glance. Used to define the active and pending virtual. Done so, you should read the learn the architecture: The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt.. Arm Interrupt Virtualization.

From www.linux-kvm.org

File03x09AspenAndre PrzywaraARM Interrupt Virtualization.pdf KVM Arm Interrupt Virtualization The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Some registers are banked per cpu (at the same memory address) distributor is the. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Done so, you should read the learn the architecture: The arm architecture virtualization extensions. Arm generic interrupt controller v3 and v4 guide.. Arm Interrupt Virtualization.

From www.youtube.com

S14 Hypervisor&virtualization (ARM Interrupt&Timer Virtualization Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Arm generic interrupt controller v3 and v4 guide. The arm architecture virtualization extensions. Some registers are banked per cpu (at the same memory address) distributor is the. Arm gicv2 at a glance. Done. Arm Interrupt Virtualization.

From blog.csdn.net

Arm Generic Interrupt Controller v3 and v4 Virtualization_virtual Arm Interrupt Virtualization Some registers are banked per cpu (at the same memory address) distributor is the. Arm generic interrupt controller v3 and v4 guide. Used to define the active and pending virtual. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The arm architecture virtualization extensions. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Done. Arm Interrupt Virtualization.

From genode.org

Genode An indepth look into the ARM virtualization extensions Arm Interrupt Virtualization Done so, you should read the learn the architecture: Arm gicv2 at a glance. Some registers are banked per cpu (at the same memory address) distributor is the. Used to define the active and pending virtual. The arm architecture virtualization extensions. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Arm generic. Arm Interrupt Virtualization.

From developer.arm.com

Generic Interrupt Controllers Arm Developer Arm Interrupt Virtualization Arm generic interrupt controller v3 and v4 guide. Done so, you should read the learn the architecture: The arm architecture virtualization extensions. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Arm gicv2 at a glance. Used to define the active and pending virtual. The. Arm Interrupt Virtualization.

From www.youtube.com

ARM interrupts and execptions concept YouTube Arm Interrupt Virtualization Arm gicv2 at a glance. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Some registers are banked per cpu (at the same memory address) distributor is the. The arm architecture virtualization extensions. Used to define the active and pending virtual. Done so, you should read the learn the architecture: Arm generic interrupt controller v3. Arm Interrupt Virtualization.

From virtualization-study.blogspot.com

Virtualization ARM Virtualization Extensions Arm Interrupt Virtualization Done so, you should read the learn the architecture: Arm generic interrupt controller v3 and v4 guide. Arm gicv2 at a glance. Used to define the active and pending virtual. Some registers are banked per cpu (at the same memory address) distributor is the. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm. Arm Interrupt Virtualization.

From microcontrollerslab.com

Sequence of Interrupt Processing Steps ARM CortexM Microcontrollers Arm Interrupt Virtualization The arm architecture virtualization extensions. Arm generic interrupt controller v3 and v4 guide. Some registers are banked per cpu (at the same memory address) distributor is the. Used to define the active and pending virtual. Arm gicv2 at a glance. Done so, you should read the learn the architecture: The generic interrupt controller (gic) enhances processor efficiency and supports interrupt. Arm Interrupt Virtualization.

From www.slideserve.com

PPT Lecture 3. Virtual Platform and ARM Introduction PowerPoint Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The arm architecture virtualization extensions. Done so, you should read the learn the architecture: Some registers are banked per cpu (at the same memory address) distributor is the. The hypervisor, or similar software,. Arm Interrupt Virtualization.

From www.scribd.com

ARM Interrupt Processing PDF Arm Architecture Central Processing Unit Arm Interrupt Virtualization Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The arm architecture virtualization extensions. Arm gicv2 at a glance. Arm generic interrupt controller v3 and v4 guide. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Some registers are banked per cpu (at the same memory address) distributor is the. The. Arm Interrupt Virtualization.

From slideplayer.com

ARMvisor A KVM Based Hypervisor for ARM ppt download Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: The arm architecture virtualization extensions. Done so, you should read the learn the architecture: Some registers are banked per cpu (at the same memory address) distributor is the. Arm. Arm Interrupt Virtualization.

From www.slideserve.com

PPT Lecture 3. Virtual Platform and ARM Introduction PowerPoint Arm Interrupt Virtualization The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Used to define the active and pending virtual. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Some registers are banked per cpu (at the same memory address) distributor is the. Arm gicv2 at a glance. Arm generic. Arm Interrupt Virtualization.

From microdigisoft.com

Interrupts Configuration of ARM Cortex Mx Microcontroller Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The arm architecture virtualization extensions. Arm gicv2 at a glance. Done so, you should read the learn the architecture: Used to define the active and pending virtual. Arm generic interrupt controller v3 and. Arm Interrupt Virtualization.

From blog.csdn.net

Arm Generic Interrupt Controller v3 and v4 Virtualization_virtual Arm Interrupt Virtualization Arm generic interrupt controller v3 and v4 guide. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Done so, you should read the learn the architecture: Used to define the active and pending virtual. Some registers are banked per cpu (at the. Arm Interrupt Virtualization.

From www.javacodegeeks.com

ARM Virtualization Extensions Memory and Interrupts (Part 2) Arm Interrupt Virtualization Done so, you should read the learn the architecture: The arm architecture virtualization extensions. Arm gicv2 at a glance. Used to define the active and pending virtual. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Some registers. Arm Interrupt Virtualization.

From velog.io

ARM Interrupts (1) Arm Interrupt Virtualization The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Some registers are banked per cpu (at the same memory address) distributor is the. Done so, you should read the learn the architecture: Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Arm gicv2 at a glance. Arm generic interrupt controller v3 and v4 guide.. Arm Interrupt Virtualization.

From www.programmersought.com

PCIe driver Programmer Sought Arm Interrupt Virtualization Some registers are banked per cpu (at the same memory address) distributor is the. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Done so, you should read the learn the architecture: Arm gicv2 at a glance. Used to define the active. Arm Interrupt Virtualization.

From www.slideserve.com

PPT 虛擬化技術 Virtualization Technique PowerPoint Presentation ID1798056 Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: The arm architecture virtualization extensions. Done so, you should read the learn the architecture: Arm generic interrupt controller v3 and v4 guide. Enabling, disabling, and generating processor interrupts from. Arm Interrupt Virtualization.

From microcontrollerslab.com

Sequence of Interrupt Processing Steps ARM CortexM Microcontrollers Arm Interrupt Virtualization Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Some registers are banked per cpu (at the same memory address) distributor is the. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: The arm architecture virtualization extensions. Done so, you should read the learn the architecture: Used to define the active and pending virtual.. Arm Interrupt Virtualization.

From www.slideserve.com

PPT AMD Virtualization Technology Directions PowerPoint Presentation Arm Interrupt Virtualization Done so, you should read the learn the architecture: The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Some registers are banked per cpu (at the same memory address) distributor is the. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Arm generic interrupt controller v3 and. Arm Interrupt Virtualization.

From www.slideserve.com

PPT The ARM Architecture PowerPoint Presentation, free download ID Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Arm generic interrupt controller v3 and v4 guide. Done so, you should read the learn the architecture: Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Used to define the active and pending virtual. Arm gicv2 at a glance. The arm architecture. Arm Interrupt Virtualization.

From www.youtube.com

[2015] ARM interrupt virtualization by Andre Przywara YouTube Arm Interrupt Virtualization Some registers are banked per cpu (at the same memory address) distributor is the. Used to define the active and pending virtual. The arm architecture virtualization extensions. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Done so, you should read the learn the architecture: Arm generic interrupt controller v3 and v4 guide. Arm gicv2. Arm Interrupt Virtualization.

From blog.csdn.net

Arm Generic Interrupt Controller v3 and v4 Virtualization_virtual Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Arm generic interrupt controller v3 and v4 guide. Arm gicv2 at a glance. Done so, you should read the learn the architecture: Some registers are banked per cpu (at the same memory address). Arm Interrupt Virtualization.

From microcontrollerslab.com

Nested Vectored Interrupt Controller (NVIC) ARM CortexM Arm Interrupt Virtualization Arm generic interrupt controller v3 and v4 guide. The arm architecture virtualization extensions. Used to define the active and pending virtual. Some registers are banked per cpu (at the same memory address) distributor is the. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. Arm gicv2 at a glance. Enabling, disabling, and. Arm Interrupt Virtualization.

From slideplayer.com

ARMvisor A KVM Based Hypervisor for ARM ppt download Arm Interrupt Virtualization The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The arm architecture virtualization extensions. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Done so, you should read the learn the architecture: Arm generic interrupt controller v3. Arm Interrupt Virtualization.

From developer.arm.com

Architectures Secure virtualization Arm Developer Arm Interrupt Virtualization Arm gicv2 at a glance. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. The generic interrupt controller (gic) enhances processor efficiency and supports interrupt virtualization, offering solutions for arm cortex. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: The arm architecture virtualization extensions. Done so, you should read the learn the architecture:. Arm Interrupt Virtualization.

From www.youtube.com

ARM7 Interrupts and Exceptions Steps, ISR Address, and Overview ARM Arm Interrupt Virtualization Used to define the active and pending virtual. Enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt. Some registers are banked per cpu (at the same memory address) distributor is the. Arm generic interrupt controller v3 and v4 guide. The hypervisor, or similar software, manages the gic virtual interface control registers, consisting of: Arm gicv2 at a glance. The. Arm Interrupt Virtualization.