# **RF Agile Transceiver**

Data Sheet AD9361

#### **FEATURES**

RF 2 × 2 transceiver with integrated 12-bit DACs and ADCs

Band: 70 MHz to 6.0 GHz

**Supports TDD and FDD operation**

Tunable channel BW: <200 kHz to 56 MHz

Dual receivers: 6 differential or 12 single-ended inputs Superior receiver sensitivity with a noise figure < 2.5 dB

**RX** gain control

Real-time monitor and control signals for manual gain

Independent automatic gain control

Dual transmitters: 4 differential outputs

Highly linear broadband transmitter

TX EVM: ≤-40 dB

TX noise: ≤-157 dBm/Hz noise floor

TX monitor: ≥66 dB dynamic range with 1 dB accuracy

Integrated fractional-N synthesizers

2.5 Hz maximum local oscillator (LO) step size

Multichip synchronization CMOS/LVDS digital interface

## **APPLICATIONS**

Point to point communication systems Femtocell/picocell/microcell base stations General-purpose radio systems

### **GENERAL DESCRIPTION**

The AD9361 is a high performance, highly integrated RF Agile Transceiver™ designed for use in 3G and 4G base station applications. Its programmability and wideband capability make it ideal for a broad range of transceiver applications. The device combines an RF front end with a flexible mixed-signal baseband section and integrated frequency synthesizers, simplifying design-in by providing a configurable digital interface to a processor. The AD9361 operates in the 70 MHz to 6.0 GHz range, covering most licensed and unlicensed bands. Channel bandwidths from less than 200 kHz to 56 MHz are supported.

The two independent direct conversion receivers have state-of-the-art noise figure and linearity. Each receive (RX) subsystem includes independent automatic gain control (AGC), dc offset correction, quadrature correction, and digital filtering, thereby eliminating the need for these functions in the digital baseband. The AD9361 also has flexible manual gain modes that can be externally controlled. Two high dynamic range ADCs per channel digitize the received I and Q signals and pass them through con-

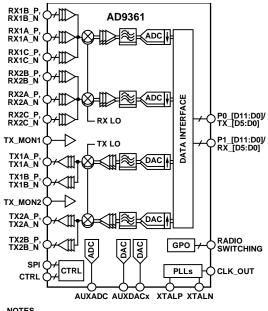

#### **FUNCTIONAL BLOCK DIAGRAM**

1. SPI, CTRL, P0\_[D11:D0]/TX\_[D5:D0], P1\_[D11:D0]/RX\_[D5:D0],

AND RADIO SWITCHING CONTAIN MULTIPLE PINS.

figurable decimation filters and 128-tap FIR filters to produce a 12-bit output signal at the appropriate sample rate.

The transmitters use a direct conversion architecture that achieves high modulation accuracy with ultralow noise. This transmitter design produces a best in class TX EVM of <-40 dB, allowing significant system margin for the external PA selection. The on-board transmit (TX) power monitor can be used as a power detector, enabling highly accurate TX power measurements.

The fully integrated phase-locked loops (PLLs) provide low power fractional-N frequency synthesis for all receive and transmit channels. Channel isolation, demanded by frequency division duplex (FDD) systems, is integrated into the design. All VCO and loop filter components are integrated.

The core of the AD9361 can be powered directly from a 1.3 V regulator. The IC is controlled via a standard 4-wire serial port and four real-time I/O control pins. Comprehensive power-down modes are included to minimize power consumption during normal use. The AD9361 is packaged in a  $10 \text{ mm} \times 10 \text{ mm}$ , 144-ball chip scale package ball grid array (CSP\_BGA).

To access the complete data sheet and design support package, download them from the AD9361 Integrated RF Agile Transceiver Resources.

AD9361 Data Sheet

**NOTES**