# Ultra-Low Power, High-Performance Arm Cortex-M4 with FPU Based Microcontroller for Wearables

### **General Description**

The MAX32630-MAX32632 are Arm® Cortex®-M4 with FPU-based microcontrollers, ideal for the emerging category of wearable medical and fitness applications. The architecture combines ultra-low power high-efficiency signal processing functionality with significantly reduced power consumption and ease of use. The device features four powerful and flexible power modes. A peripheral management unit (PMU) enables intelligent peripheral control with up to six channels to significantly reduce power consumption. Built-in dynamic clock gating and firmwarecontrolled power gating allows the user to optimize power for the specific application. Multiple SPI, UART and I2C serial interfaces, as well as 1-Wire® master and USB, allow for interconnection to a wide variety of external sensors. A four-input, 10-bit ADC with selectable references is available to monitor analog input from external sensors and meters.

The MAX32630–MAX32632 include a hardware AES engine. The MAX32631 is a secure version of the MAX32630. It incorporates a trust protection unit (TPU) with encryption and advanced security features. These features include a modular arithmetic accelerator (MAA) for fast ECDSA, and a true random number generator.

The MAX32632 provides additional security and lifecycle management by adding a secure bootloader to the MAX32631. Contact factory for ordering details.

### **Applications**

- Sports Watches

- Fitness Monitors

- Wearable Medical Patches

- Portable Medical Devices

- Sensor Hubs

Ordering Information appears at end of data sheet.

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- High-Efficiency Microcontroller for Wearable Devices

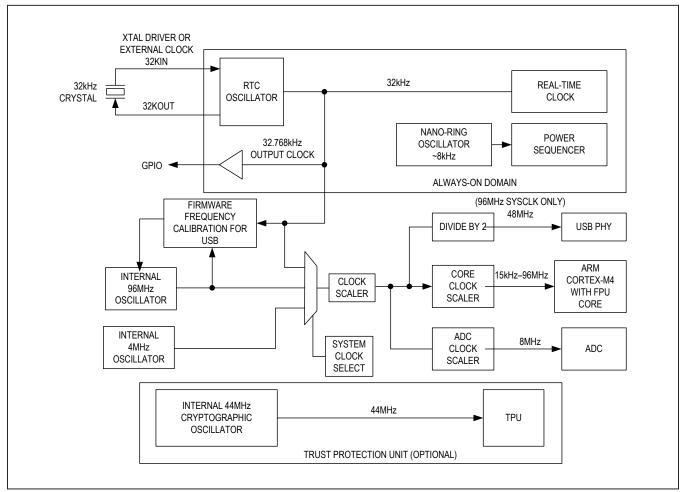

- Internal Oscillator Operates Up to 96MHz

- Low Power 4MHz Oscillator System Clock Option for Always-On Monitoring Applications

- · 2MB Flash Memory

- 512KB SRAM

- · 8KB Instruction Cache

- 1.2V Core Supply Voltage

- 1.8V to 3.3V I/O

- Optional 3.3V ±5% USB Supply Voltage

- Power Management Maximizes Uptime for Battery Applications

- 106µA/MHz Active Current Executing from Cache

- · Wakeup to 96MHz Clock or 4MHz Clock

- 600nA Low Power Mode (LP0) Current with RTC Enabled

- 3.5µW/MHz Ultra-Low Power Data Retention Sleep Mode (LP1) with Fast 5µs Wakeup to 96MHz

- Optimal Peripheral Mix Provides Platform Scalability

- SPIX Execute in Place (XIP) Engine for Memory Expansion with Minimal Footprint

- · Up to Three SPI Masters, One SPI Slave

- Four UARTs

- Up to Three I2C Masters, One I2C Slave

- · 1-Wire Master

- Full-Speed USB 2.0 Engine with Internal Transceiver

- · Sixteen Pulse Train (PWM) Engines

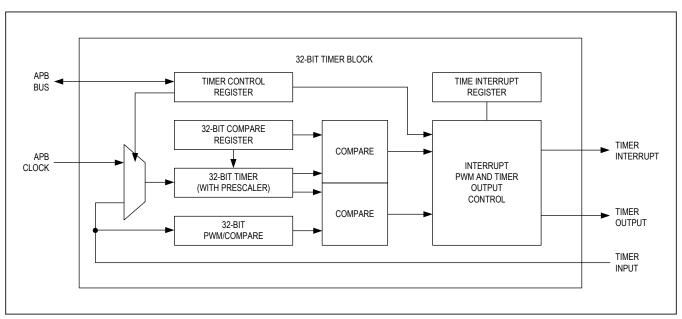

- Six 32-Bit Timers and 3 Watchdog Timers

- Up to 66 General-Purpose I/O Pins

- One 10-Bit Delta-Sigma ADC Operating at 7.8ksps

- AES-64, -128, -256

- · CMOS-Level 32kHz RTC Output

- Secure Valuable IP and Data with Robust Internal Hardware Security (MAX32631/MAX32632 Only)

- Trust Protection Unit (TPU) Including MAA Supports ECDSA and Modular Arithmetic

- True Random Number Generator

- Secure Boot Loader (MAX32632 Only)

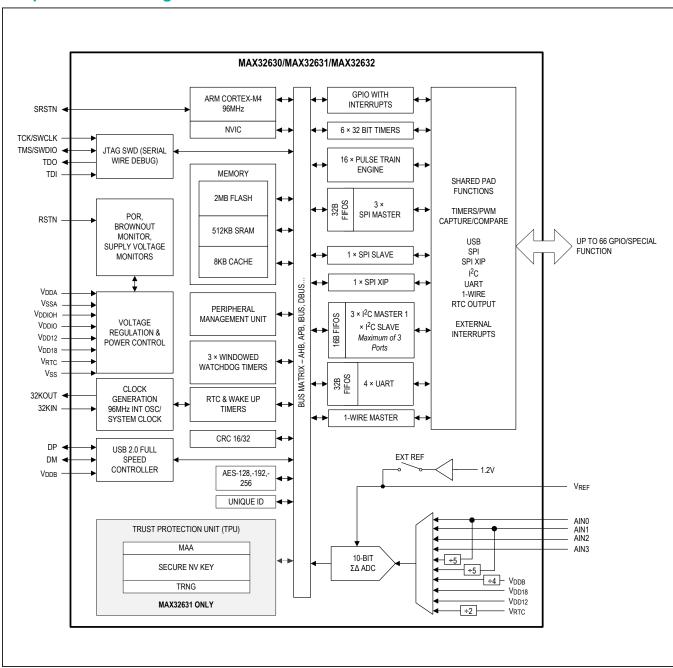

### **Simplified Block Diagram**

### Ultra-Low Power, High-Performance Arm Cortex-M4 with FPU Based Microcontroller for Wearables

### **Absolute Maximum Ratings**

| (All voltages with respect to V <sub>SS</sub> , unless otherwise | e noted.)     | AIN[3:2]                                                    | 0.3V to +3.6V   |

|------------------------------------------------------------------|---------------|-------------------------------------------------------------|-----------------|

| V <sub>DD18</sub> 0                                              | .3V to +1.89V | V <sub>DDIO</sub>                                           | 0.3V to +3.6V   |

| V <sub>DD12</sub> 0                                              | .3V to +1.26V | V <sub>DDIOH</sub>                                          | 0.3V to +3.6V   |

| V <sub>DDA</sub> relative to V <sub>SSA</sub> 0                  | .3V to +1.89V | Total Current into All V <sub>DD18</sub> Power Pins (sink). | 100mA           |

| V <sub>RTC</sub> 0                                               | .3V to +1.89V | Total Current into V <sub>SS</sub>                          | 100mA           |

| V <sub>DDB</sub>                                                 | 0.3V to +3.6V | Output Current (sink) by Any I/O Pin                        | 25mA            |

| V <sub>REF</sub>                                                 | 0.3V to +3.6V | Output Current (source) by Any I/O Pin                      | 25mA            |

| 32KIN, 32KOUT                                                    | 0.3V to +3.6V | Operating Temperature Range                                 | 20°C to +85°C   |

| RSTN, SRSTN, DP, DM, GPIO, JTAG                                  | 0.3V to +3.6V | Storage Temperature Range                                   | -65°C to +150°C |

| AIN[1:0]                                                         | 0.3V to +5.5V | Soldering Temperature (reflow)                              | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 100 WLP

| Package Code                                           | W1004D4+1                      |

|--------------------------------------------------------|--------------------------------|

| Outline Number                                         | 21-100043                      |

| Land Pattern Number                                    | Refer to Application Note 1891 |

| Thermal Resistance, Single-Layer Board                 |                                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | N/A                            |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |

| Thermal Resistance, Four-Layer Board                   |                                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 38.9°C/W                       |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to -20°C are guaranteed by design and are not production tested.)

| PARAMETER                                      | SYMBOL                 | CONDITIONS                                                                                                                                                                                                                                             | MIN  | TYP  | MAX  | UNITS  |  |

|------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|--|

|                                                | V <sub>DD18</sub>      |                                                                                                                                                                                                                                                        | 1.71 | 1.8  | 1.89 |        |  |

|                                                | V <sub>DD12</sub>      |                                                                                                                                                                                                                                                        | 1.14 | 1.2  | 1.26 |        |  |

| Cumply Voltage                                 | $V_{DDA}$              |                                                                                                                                                                                                                                                        | 1.71 | 1.8  | 1.89 | V      |  |

| Supply Voltage                                 | V <sub>RTC</sub>       |                                                                                                                                                                                                                                                        | 1.75 | 1.8  | 1.89 | V      |  |

|                                                | V <sub>DDIO</sub>      |                                                                                                                                                                                                                                                        | 1.71 | 1.8  | 3.6  |        |  |

|                                                | V <sub>DDIOH</sub>     | V <sub>DDIOH</sub> must be ≥ V <sub>DDIO</sub>                                                                                                                                                                                                         | 1.71 | 1.8  | 3.6  |        |  |

| Power Fail Reset<br>Voltage                    | V <sub>RST</sub>       | Monitors V <sub>DD18</sub>                                                                                                                                                                                                                             | 1.62 |      | 1.7  | V      |  |

| Power-On Reset Voltage                         | V <sub>POR</sub>       | Monitors V <sub>DD18</sub>                                                                                                                                                                                                                             |      | 1.5  |      | V      |  |

| RAM Data Retention Voltage                     | V <sub>DRV</sub>       |                                                                                                                                                                                                                                                        |      | 0.93 |      | V      |  |

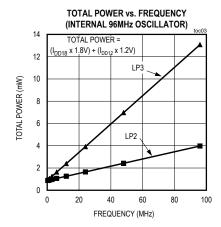

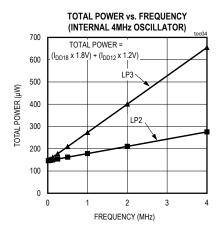

| V <sub>DD12</sub> Dynamic Current,<br>LP3 Mode | I <sub>DD12_DLP3</sub> | Measured on the $V_{DD12}$ pin and executing code from cache memory, all inputs are tied to $V_{SS}$ or $V_{DD18}$ , outputs do not source/sink any current, PMU disabled                                                                              |      | 106  |      | μΑ/MHz |  |

| V <sub>DD12</sub> Fixed Current,               |                        | Measured on the $V_{DD12}$ pin and executing code from cache memory, all inputs are tied to $V_{SS}$ or $V_{DD18}$ , outputs do not source/sink any current, 96MHz oscillator selected as system clock                                                 |      | 173  |      |        |  |

| LP3 Mode                                       | IDD12_FLP3             | Measured on the $V_{DD12}$ pin and executing code from cache memory, all inputs are tied to $V_{SS}$ or $V_{DD18}$ , outputs do not source/sink any current, 4MHz oscillator selected as system clock                                                  |      | 72   |      | - μΑ   |  |

| V <sub>DD18</sub> Fixed Current,               |                        | Measured on the V <sub>DD18</sub> + V <sub>DDA</sub> device pins and executing code from cache memory, all inputs are tied to V <sub>SS</sub> or V <sub>DD18</sub> , outputs do not source/sink any current, 96MHz oscillator selected as system clock |      | 366  |      |        |  |

| LP3 Mode                                       | I <sub>DD18</sub> FLP3 | Measured on the V <sub>DD18</sub> + V <sub>DDA</sub> device pins and executing code from cache memory, all inputs are tied to V <sub>SS</sub> or V <sub>DD18</sub> , outputs do not source/sink any current, 4MHz oscillator selected as system clock  |      | 33   |      | - μΑ   |  |

| V <sub>DD12</sub> Dynamic Current,<br>LP2 Mode | I <sub>DD12_DLP2</sub> | Measured on the V <sub>DD12</sub> pin, ARM in sleep mode, PMU with two channels active                                                                                                                                                                 |      | 27   |      | μΑ/MHz |  |

| V <sub>DD12</sub> Fixed Current,               | IDD40 ELBO             | Measured on the V <sub>DD12</sub> pin, ARM in sleep<br>mode, PMU with two channels active,<br>96MHz oscillator selected as system clock                                                                                                                |      | 173  |      |        |  |

| LP2 Mode                                       | IDD12_FLP2             | Measured on the V <sub>DD12</sub> pin, ARM in sleep mode, PMU with two channels active, 4MHz oscillator selected as system clock                                                                                                                       |      | 72   |      | - μΑ   |  |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to -20°C are guaranteed by design and are not production tested.)

| PARAMETER                                    | SYMBOL                       | CONDITIONS                                                                                                                                                   | MIN                        | TYP               | MAX                        | UNITS |

|----------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|----------------------------|-------|

| V <sub>DD18</sub> Fixed Current,             |                              | Measured on the V <sub>DD18</sub> + V <sub>DDA</sub> device pins, ARM in sleep mode, PMU with two channels active, 96MHz oscillator selected as system clock |                            | 366               |                            | μA    |

| LP2 Mode                                     | pins. ARM in sleep mode, PM  | Measured on the V <sub>DD18</sub> + V <sub>DDA</sub> device pins. ARM in sleep mode, PMU with two channels active, 4MHz oscillator selected as system clock  |                            | 33                |                            | μΛ    |

| V <sub>DD12</sub> Fixed Current,<br>LP1 Mode | I <sub>DD12_FLP1</sub>       | Standby state with full data retention                                                                                                                       |                            | 1.86              |                            | μΑ    |

| V <sub>DD18</sub> Fixed Current,<br>LP1 Mode | I <sub>DD18_FLP1</sub>       | Standby state with full data retention                                                                                                                       |                            | 120               |                            | nA    |

| V <sub>RTC</sub> Fixed Current,<br>LP1 Mode  | I <sub>DDRTC</sub> _<br>FLP1 | RTC enabled, retention regulator powered by V <sub>DD12</sub>                                                                                                |                            | 505               |                            | nA    |

| V <sub>DD12</sub> Fixed Current,<br>LP0 Mode | I <sub>DD12_FLP0</sub>       |                                                                                                                                                              |                            | 14                |                            | nA    |

| V <sub>DD18</sub> Fixed Current,<br>LP0 Mode | I <sub>DD18_FLP0</sub>       |                                                                                                                                                              |                            | 120               |                            | nA    |

| V <sub>RTC</sub> Fixed Current,              | I <sub>DDRTC</sub> _         | RTC enabled                                                                                                                                                  |                            | 505               |                            | nA    |

| LP0 Mode                                     | FLP0                         | RTC disabled                                                                                                                                                 |                            | 105               |                            | 10.0  |

| LP2 Mode Resume Time                         | t <sub>LP2_ON</sub>          |                                                                                                                                                              |                            | 0                 |                            | μs    |

| LP1 Mode Resume Time                         | t <sub>LP1_ON</sub>          |                                                                                                                                                              |                            | 5                 |                            | μs    |

| LP0 Mode Resume Time                         | t <sub>LP0_ON</sub>          | Polling flash ready                                                                                                                                          |                            | 11                |                            | μs    |

| JTAG                                         |                              |                                                                                                                                                              |                            |                   |                            |       |

| Input Low Voltage for TCK, TMS, TDI          | V <sub>IL</sub>              |                                                                                                                                                              |                            |                   | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input High Voltage for TCK,<br>TMS, TDI      | V <sub>IH</sub>              |                                                                                                                                                              | 0.7 x<br>V <sub>DDIO</sub> |                   |                            | V     |

| Output Low Voltage for TDO                   | V <sub>OL</sub>              |                                                                                                                                                              |                            | 0.2               | 0.4                        | V     |

| Output High Voltage for TDO                  | V <sub>OH</sub>              |                                                                                                                                                              | V <sub>DDIO</sub> - 0.4    |                   |                            |       |

| CLOCKS                                       |                              |                                                                                                                                                              |                            |                   |                            |       |

| System Clock Frequency                       | f <sub>CK</sub>              |                                                                                                                                                              | 0.001                      |                   | 98                         | MHz   |

| System Clock Period                          | t <sub>CK</sub>              |                                                                                                                                                              |                            | 1/f <sub>CK</sub> |                            | ns    |

| Internal Delevis Co. 20 5                    |                              | Factory default                                                                                                                                              | 94                         | 96                | 98                         |       |

| Internal Relaxation Oscillator Frequency     | fINTCLK                      | Firmware trimmed, required for USB compliance                                                                                                                | 95.76                      | 96                | 96.24                      | MHz   |

| Internal RC Oscillator<br>Frequency          | fRCCLK                       |                                                                                                                                                              | 3.9                        | 4                 | 4.1                        | MHz   |

| RTC Input Frequency                          | f <sub>32KIN</sub>           | 32kHz watch crystal                                                                                                                                          |                            | 32.768            |                            | kHz   |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to -20°C are guaranteed by design and are not production tested.)

| PARAMETER                                | SYMBOL                | CONDITIONS                                                                                                                                         | MIN                          | TYP  | MAX                         | UNITS    |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-----------------------------|----------|

| PTC Operating Current                    | I <sub>RTC_LP23</sub> | LP2 or LP3 mode                                                                                                                                    |                              | 0.7  |                             |          |

| RTC Operating Current                    | I <sub>RTC_LP01</sub> | LP0 or LP1 mode                                                                                                                                    |                              | 0.35 |                             | μA       |

| RTC Power-Up Time                        | t <sub>RTC_ON</sub>   |                                                                                                                                                    |                              | 250  |                             | ms       |

| GENERAL-PURPOSE I/O                      |                       |                                                                                                                                                    |                              |      |                             |          |

| Input Low Voltage for All                | V <sub>IL</sub>       | V <sub>DDIO</sub> selected as I/O supply                                                                                                           |                              |      | 0.3 ×<br>V <sub>DDIO</sub>  | V        |

| GPIO Pins                                | VIL.                  | V <sub>DDIOH</sub> selected as I/O supply                                                                                                          |                              |      | 0.3 ×<br>V <sub>DDIOH</sub> | V        |

| Input Low Voltage for RSTN               | V <sub>IL</sub>       |                                                                                                                                                    |                              |      | 0.3 x<br>V <sub>RTC</sub>   | V        |

| Input Low Voltage for SRSTN              | V <sub>IL</sub>       |                                                                                                                                                    |                              |      | 0.3 x<br>V <sub>DDIO</sub>  |          |

| Input High Voltage for All               | V <sub>IH</sub>       | V <sub>DDIO</sub> selected as I/O supply                                                                                                           | 0.7 ×<br>V <sub>DDIO</sub>   |      |                             | V        |

| GPIO Pins                                | VIH                   | V <sub>DDIOH</sub> selected as I/O supply                                                                                                          | 0.7 ×<br>V <sub>DDIOH</sub>  |      |                             | <b>v</b> |

| Input High Voltage for RSTN              | V <sub>IH</sub>       |                                                                                                                                                    | 0.7 x<br>V <sub>RTC</sub>    |      |                             | V        |

| Input High Voltage for SRSTN             | V <sub>IH</sub>       |                                                                                                                                                    | 0.7 x<br>V <sub>DDIO</sub>   |      |                             | V        |

| Input Hysteresis (Schmitt)               | V <sub>IHYS</sub>     |                                                                                                                                                    |                              | 300  |                             | mV       |

|                                          |                       | $V_{DDIO} = V_{DDIOH} = 1.71V$ , $V_{DDIO}$ selected as I/O supply, $I_{OL} = 4$ mA, normal drive configuration                                    |                              | 0.2  | 0.4                         |          |

| Output Low Voltage for All GPIO Pins     | V <sub>OL</sub>       | V <sub>DDIO</sub> = V <sub>DDIOH</sub> = 1.71V, V <sub>DDIO</sub> selected as I/O supply, I <sub>OL</sub> = 24mA, fast drive configuration         |                              | 0.2  | 0.4                         | ٧        |

|                                          |                       | V <sub>DDIO</sub> = 1.71V V <sub>DDIOH</sub> = 2.97V, V <sub>DDIOH</sub> selected as I/O supply, I <sub>OL</sub> = 300μA                           |                              | 0.2  | 0.45                        |          |

| Combined $I_{OL}$ , All GPIO Pins        | I <sub>OL_TOTAL</sub> |                                                                                                                                                    |                              |      | 48                          | mA       |

|                                          |                       | I <sub>OH</sub> = -2mA, V <sub>DDIO</sub> = V <sub>DDIOH</sub> = 1.71V,<br>V <sub>DDIO</sub> selected as I/O supply, normal drive<br>configuration | V <sub>DDIO</sub> - 0.4      |      |                             |          |

| Output High Voltage for All GPIO Pins    | V <sub>OH</sub>       | I <sub>OH</sub> = -8mA, V <sub>DDIO</sub> = V <sub>DDIOH</sub> = 1.71V,<br><sub>VDDIO</sub> selected as I/O supply, fast drive<br>configuration    | V <sub>DDIO</sub> - 0.4      |      |                             | V        |

|                                          |                       | I <sub>OH</sub> = -300μA, V <sub>DDIOH</sub> = 3.6V, V <sub>DDIOH</sub> selected as I/O supply                                                     | V <sub>DDIOH</sub><br>- 0.45 |      |                             |          |

| Ouput High Voltage for All<br>GPIO Pins  | V <sub>OH</sub>       | V <sub>DDIO</sub> = 1.71V, V <sub>DDIOH</sub> = 3.6V. V <sub>DDIO</sub> selected as I/O supply, I <sub>OH</sub> = -2mA                             | V <sub>DDIO</sub> - 0.45     |      |                             | V        |

| Combined $I_{\mbox{OH}}$ , All GPIO Pins | IOH_TOTAL             |                                                                                                                                                    |                              |      | -48                         | mA       |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to -20°C are guaranteed by design and are not production tested.)

| PARAMETER                                        | SYMBOL               | CONDITIONS                                                                                                                                      | MIN  | TYP | MAX  | UNITS   |

|--------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|---------|

| Input/Output Pin Capacitance for All Pins        | C <sub>IO</sub>      |                                                                                                                                                 |      | 3   |      | pF      |

| Input Leakage Current Low                        | I <sub>IL</sub>      | V <sub>DDIO</sub> = 1.89V, V <sub>DDIOH</sub> = 3.6V, V <sub>DDIOH</sub> selected as I/O supply, V <sub>IN</sub> = 0V, internal pullup disabled | -100 |     | +100 | nA      |

|                                                  | l <sub>IН</sub>      | $V_{\rm DDIO}$ = 1.89V, $V_{\rm DDIOH}$ = 3.6V, $V_{\rm DDIOH}$ selected as I/O supply, $V_{\rm IN}$ = 3.6V, internal pulldown disabled         | -100 |     | +100 | nA      |

| Input Leakage Current High                       | I <sub>OFF</sub>     | $V_{\rm DDIO}$ = 0V, $V_{\rm DDIOH}$ = 0V, $V_{\rm DDIO}$ selected as I/O supply, $V_{\rm IN}$ < 1.89V                                          | -1   |     | +1   |         |

|                                                  | I <sub>IH3V</sub>    | $V_{DDIO} = V_{DDIOH} = 1.71V$ , $V_{DDIO}$ selected as I/O supply, $V_{IN} = 3.6V$                                                             | -2   |     | +2   | μΑ      |

| Input Pullup Resistor RSTN, SRSTN, TMS, TCK, TDI | R <sub>PU</sub>      |                                                                                                                                                 |      | 25  |      | kΩ      |

| Input Pullup/Pulldown                            | R <sub>PU1</sub>     | Normal resistance                                                                                                                               |      | 25  |      | kΩ      |

| Resistor for All GPIO Pins                       | R <sub>PU2</sub>     | Highest resistance                                                                                                                              |      | 1   |      | ΜΩ      |

| FLASH MEMORY                                     |                      |                                                                                                                                                 |      |     |      |         |

| Page Size                                        |                      | 2MB flash                                                                                                                                       |      | 8   |      | kB      |

| Flash Erase Time                                 | t <sub>M_ERASE</sub> | Mass erase                                                                                                                                      |      | 30  |      | ms      |

| Flasii Elase IIIIle                              | t <sub>P_ERASE</sub> | Page erase                                                                                                                                      |      | 30  |      | 1115    |

| Flash Programming Time per Word                  | t <sub>PROG</sub>    |                                                                                                                                                 |      | 60  |      | μs      |

| Flash Endurance                                  |                      |                                                                                                                                                 | 10   |     |      | kcycles |

| Data Retention                                   | t <sub>RET</sub>     | T <sub>A</sub> = +85°C                                                                                                                          | 10   |     |      | years   |

#### **ADC Electrical Characteristics**

(Internal bandgap reference selected, ADC\_SCALE = ADC\_REFSCL = 1, unless otherwise specified. Specifications marked GBD are guaranteed by design and not production tested.)

| PARAMETER           | SYMBOL            | CONDITIONS                                   | MIN              | TYP                 | MAX                        | UNITS |

|---------------------|-------------------|----------------------------------------------|------------------|---------------------|----------------------------|-------|

| Resolution          |                   |                                              |                  | 10                  |                            | Bits  |

| ADC Clock Rate      | f <sub>ACLK</sub> |                                              | 0.1              |                     | 8                          | MHz   |

| ADC Clock Period    | tACLK             |                                              |                  | 1/f <sub>ACLK</sub> |                            | μs    |

|                     | V <sub>AIN</sub>  | AIN[3:0], ADC_CHSEL = 0-3,<br>BUF_BYPASS = 0 | 0.05             |                     | V <sub>DDA</sub> -<br>0.05 |       |

| Input Voltage Bange |                   | AIN[1:0], ADC_CHSEL = 4-5,<br>BUF_BYPASS = 0 | 0.05             |                     | 5.5                        | V     |

| Input Voltage Range |                   | AIN[3:0], ADC_CHSEL = 0-3,<br>BUF_BYPASS = 1 | V <sub>SSA</sub> |                     | V <sub>DDA</sub>           | V     |

|                     |                   | AIN[1:0], ADC_CHSEL = 4-5,<br>BUF_BYPASS = 1 | V <sub>SSA</sub> |                     | 5.5                        |       |

### **ADC Electrical Characteristics (continued)**

(Internal bandgap reference selected, ADC\_SCALE = ADC\_REFSCL = 1, unless otherwise specified. Specifications marked GBD are guaranteed by design and not production tested.)

| PARAMETER                           | SYMBOL               | CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNITS             |

|-------------------------------------|----------------------|--------------------------------------------------------------------------------------|------|------|------|-------------------|

| Input Impedance                     | R <sub>AIN</sub>     | AIN[1:0], ADC_CHSEL = 4-5, ADC active                                                |      | 45   |      | kΩ                |

| Input Dynamic Current               | Lene                 | Switched capactiance input current, ADC active, ADC buffer bypassed                  |      | 4.5  |      | μА                |

| input Bynamic Gurrent               | <sup>I</sup> AIN     | Switched capacitance input current, ADC active, ADC buffer enabled                   |      | 50   |      | nA                |

| Analog Input                        | C <sub>AIN</sub>     | Fixed capacitance to V <sub>SSA</sub>                                                |      | 1    |      | pF                |

| Capacitance                         | CAIN                 | Dynamically switched capacitance                                                     |      | 250  |      | fF                |

| Integral Nonlinearity               | INL                  |                                                                                      |      |      | ±2   | LSb               |

| Differential Nonlinearity           | DNL                  |                                                                                      |      |      | ±1   | LSb               |

| Offset Error                        | Vos                  |                                                                                      |      | ±1   |      | LSb               |

| Gain Error                          | GE                   |                                                                                      |      | ±2   |      | LSb               |

| Signal to Noise Ratio               | SNR                  |                                                                                      |      | 58.5 |      | dB                |

| Signal to Noise and Distortion      | SINAD                |                                                                                      |      | 58.5 |      | dB                |

| Total Harmonic<br>Distortion        | THD                  |                                                                                      |      | 68.5 |      | dB                |

| Spurious Free Dynamic<br>Range      | SFDR                 |                                                                                      |      | 74   |      | dB                |

| ADC Active Current                  | I <sub>ADC</sub>     | ADC active, reference buffer enabled, input buffer disabled                          |      | 240  |      | μА                |

| Input Buffer Active Current         | I <sub>INBUF</sub>   |                                                                                      |      | 53   |      | μA                |

| ADC Setup Time                      | <sup>t</sup> ADC SU  | Any powerup of: ADC clock, ADC bias, reference buffer or input buffer to CpuAdcStart |      |      | 10   | μs                |

|                                     |                      | Any power-up of: ADC clock or ADC bias to CpuAdcStart                                |      |      | 48   | t <sub>ACLK</sub> |

| ADC Output Latency                  | t <sub>ADC</sub>     |                                                                                      |      | 1025 |      | tACLK             |

| ADC Sample Rate                     | f <sub>ADC</sub>     |                                                                                      |      |      | 7.8  | ksps              |

| ADC Immut I calcage                 |                      | AIN0 or AIN1, ADC inactive or channel not selected                                   |      | 0.12 | 4    | - ^               |

| ADC Input Leakage                   | IADC_LEAK            | AIN2 or AIN3, ADC inactive or channel not selected.                                  |      | 0.02 | 1    | - nA              |

| AIN0/AIN1 Resistor<br>Divider Error |                      | ADC_CHSEL = 4 or 5, not including ADC offset/gain error                              |      | ±2   |      | LSb               |

| Full-Scale Voltage                  | V <sub>FS</sub>      | ADC code = 0x3FF                                                                     |      | 1.2  |      | V                 |

| External Reference Voltage          | V <sub>REF_EXT</sub> | ADC_XREF = 1                                                                         | 1.17 | 1.23 | 1.29 | V                 |

| Bandgap Temperature<br>Coefficient  | V <sub>TEMPCO</sub>  | Box method                                                                           |      | 30   |      | ppm               |

| Reference Dynamic Current           | I <sub>REF_EXT</sub> | ADC_XREF = 1, ADC active                                                             |      | 4.1  |      | μA                |

| Reference Input Capacitance         | C <sub>REFIN</sub>   | Dynamically switched capacitance, ADC_XREF = 1, ADC active                           |      | 250  |      | fF                |

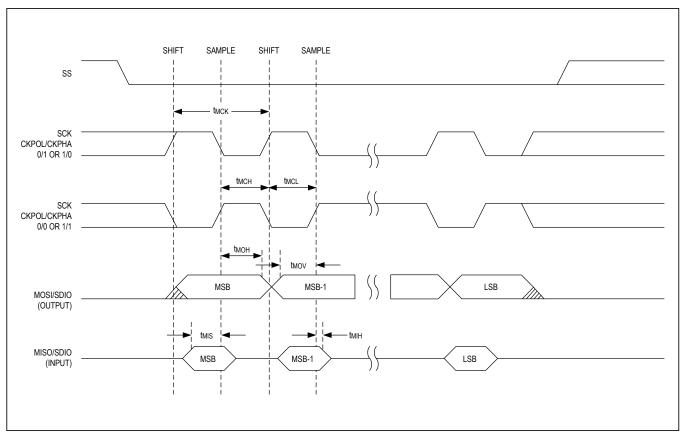

### **SPI MASTER/SPIX MASTER Electrical Characteristics**

(Guaranteed by design and not production tested.)

| PARAMETER                                       | SYMBOL                              | CONDITIONS | MIN                 | TYP                | MAX | UNITS |

|-------------------------------------------------|-------------------------------------|------------|---------------------|--------------------|-----|-------|

| Operating Frequency                             | f <sub>MCK</sub>                    |            |                     |                    | 48  | MHz   |

| SCLK Period                                     | t <sub>MCK</sub>                    |            |                     | 1/f <sub>MCK</sub> |     | ns    |

| SCLK Output Pulse-Width High/Low                | t <sub>MCH</sub> , t <sub>MCL</sub> |            | t <sub>MCK</sub> /2 |                    |     | ns    |

| MOSI Output Hold Time<br>After SCLK Sample Edge | <sup>t</sup> MOH                    |            | t <sub>MCK</sub> /2 |                    |     | ns    |

| MOSI Output Valid to<br>Sample Edge             | t <sub>MOV</sub>                    |            | t <sub>MCK</sub> /2 |                    |     | ns    |

| MISO Input Valid to SCLK<br>Sample Edge Setup   | t <sub>MIS</sub>                    |            | 3                   |                    |     | ns    |

| MISO Input to SCLK<br>Sample Edge               | t <sub>MIH</sub>                    |            |                     | 0                  |     | ns    |

Figure 1. SPI Master/SPIX Master Communications Timing Diagram

#### **USB Electrical Characteristics**

(Guaranteed by design and not production tested.)

| PARAMETER                                         | SYMBOL           | CONDITIONS                              | MIN   | TYP | MAX   | UNITS |

|---------------------------------------------------|------------------|-----------------------------------------|-------|-----|-------|-------|

| USB PHY Supply Voltage                            | $V_{DDB}$        |                                         | 2.97  | 3.3 | 3.63  | V     |

| Single-Ended Input High<br>Voltage DP, DM         | V <sub>IHD</sub> |                                         | 2     |     |       | V     |

| Single-Ended Input Low Voltage DP, DM             | V <sub>ILD</sub> |                                         |       |     | 0.8   | V     |

| Output Low Voltage DP, DM                         | V <sub>OLD</sub> | $R_L$ = 1.5kΩ from DP to 3.6V           |       |     | 0.3   | V     |

| Output High Voltage DP, DM                        | V <sub>OHD</sub> | $R_L$ = 15kΩ from DP and DM to $V_{SS}$ | 2.8   |     |       | V     |

| Differential Input Sensitivity DP, DM             | V <sub>DI</sub>  | DP to DM                                | 0.2   |     |       | V     |

| Common-Mode Voltage<br>Range                      | V <sub>CM</sub>  | Includes V <sub>DI</sub> range          | 0.8   |     | 2.5   | V     |

| Single-Ended Receiver<br>Threshold                | $V_{SE}$         |                                         | 0.8   |     | 2.0   | V     |

| Single-Ended Receiver<br>Hysteresis               | V <sub>SEH</sub> |                                         |       | 200 |       | mV    |

| Differential Output Signal<br>Cross-Point Voltage | V <sub>CRS</sub> | C <sub>L</sub> = 50pF                   | 1.3   |     | 2.0   | V     |

| DP, DM Off-State Input<br>Impedance               | R <sub>LZ</sub>  |                                         | 300   |     |       | kΩ    |

| Driver Output Impedance                           | R <sub>DRV</sub> | Steady-state drive                      | 28    |     | 44    | Ω     |

| DR Bull up Resister                               | D                | Idle                                    | 0.9   |     | 1.575 | kΩ    |

| DP Pull-up Resistor                               | R <sub>PU</sub>  | Receiving                               | 1.425 |     | 3.09  |       |

### **USB Timing Electrical Characteristics**

(AC Electrical Specifications are guaranteed by design and are not production tested,  $V_{DD18} = V_{RST}$  to 1.89V,  $V_{DDB} = 3.63$ V,  $T_{A} = -20$ °C to +85°C, Guaranteed by design and not production tested.)

| PARAMETER                          | SYMBOL                         | CONDITIONS            | MIN | TYP | MAX | UNITS |

|------------------------------------|--------------------------------|-----------------------|-----|-----|-----|-------|

| DP, DM Rise Time<br>(Transmit)     | t <sub>R</sub>                 | C <sub>L</sub> = 50pF | 4   |     | 20  | ns    |

| DP, DM Fall Time<br>(Transmit)     | t <sub>F</sub>                 | C <sub>L</sub> = 50pF | 4   |     | 20  | ns    |

| Rise/Fall Time Matching (Transmit) | t <sub>R</sub> ,t <sub>F</sub> | C <sub>L</sub> = 50pF | 90  |     | 110 | %     |

# Ultra-Low Power, High-Performance Arm Cortex-M4 with FPU Based Microcontroller for Wearables

### Electrical Characteristics—I<sup>2</sup>C BUS

(Guaranteed by design and not production tested.)

| PARAMETER                                          | SYMBOL                | CONDITIONS                                                                                                                                  | MIN                         | TYP | MAX                         | UNITS |

|----------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----------------------------|-------|

| SCI Clock Froguency                                | f                     | Standard mode                                                                                                                               |                             | 100 |                             | kHz   |

| SCL Clock Frequency                                | fscl                  | Fast mode                                                                                                                                   |                             | 400 |                             | KΠZ   |

|                                                    |                       | Fast mode, V <sub>DDIO</sub> selected as I/O supply                                                                                         | 0.7 ×<br>V <sub>DDIO</sub>  |     |                             |       |

| land the National                                  |                       | Fast mode, V <sub>DDIOH</sub> selected as I/O supply                                                                                        | 0.7 ×<br>V <sub>DDIOH</sub> |     |                             | V     |

| Input High Voltage                                 | V <sub>IH</sub> _I2C  | Standard mode, V <sub>DDIO</sub> selected as I/O supply                                                                                     | 0.7 ×<br>V <sub>DDIO</sub>  |     |                             | V     |

|                                                    |                       | Standard mode, V <sub>DDIOH</sub> selected as I/O supply                                                                                    | 0.7 ×<br>V <sub>DDIOH</sub> |     |                             |       |

|                                                    |                       | Fast mode, V <sub>DDIO</sub> selected as I/O supply                                                                                         |                             |     | 0.3 ×<br>V <sub>DDIO</sub>  |       |

| Input Low Voltage                                  |                       | Fast mode, V <sub>DDIOH</sub> selected as I/O supply                                                                                        |                             |     | 0.3 ×<br>V <sub>DDIOH</sub> | V     |

| input Low voitage                                  | V <sub>IL_I2C</sub>   | Standard mode, V <sub>DDIO</sub> selected as I/O supply                                                                                     |                             |     | 0.3 ×<br>V <sub>DDIO</sub>  | V     |

|                                                    |                       | Standard mode, V <sub>DDIOH</sub> selected as I/O supply                                                                                    |                             |     | 0.3 ×<br>V <sub>DDIOH</sub> |       |

| Input Hysteresis (Schmitt)                         | V <sub>IHYS_I2C</sub> | Fast-mode                                                                                                                                   |                             | 300 |                             | mV    |

| Output Logic-Low (Open<br>Drain or Open Collector) | V <sub>OL_I2C</sub>   | V <sub>DDIO</sub> = V <sub>DDIOH</sub> = 1.71V, V <sub>DDIO</sub> selected as I/O supply, I <sub>OL</sub> = 4mA, normal drive configuration |                             | 0.2 | 0.4                         | V     |

|                                                    |                       | V <sub>DDIO</sub> = 1.71V V <sub>DDIOH</sub> = 2.97V, V <sub>DDIOH</sub> selected as I/O supply, I <sub>OL</sub> = 300μA                    |                             | 0.2 | 0.45                        |       |

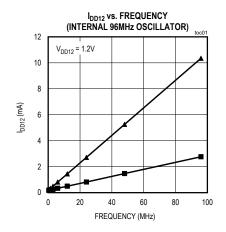

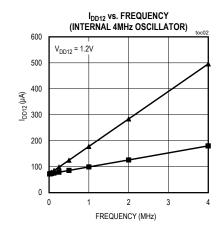

### **Typical Operating Characteristics**

$(V_{DD12} = 1.2V, V_{DD18} = 1.8V.)$

# **Pin Configuration**

### 100 WLP

| TO | P VIEW (BUMPS C | ON BOTTOM) |      |        |                   |      |      |      |                      |          |

|----|-----------------|------------|------|--------|-------------------|------|------|------|----------------------|----------|

|    | 1               | 2          | 3    | 4      | 5                 | 6    | 7    | 8    | 9                    | 10       |

| A  | N.C.            | (VDDIOH)   | Vssa | VREF   | AINO              | AIN1 | AIN2 | AIN3 | (V <sub>DD18</sub> ) | (N.C.    |

| В  | P8.1            | SRSTN      | RSTN | VDDA   | ТСК               | TMS  | TDO  | TDI  | (Vss)                | 32KIN    |

| С  | P8.0            | P0.1       | P0.0 | P6.0   | P5.7              | P5.5 | P5.4 | P5.2 | VRTC                 | (32KOUT) |

| D  | P7.7            | P0.4       | P0.5 | P0.3   | P0.2              | P5.6 | P5.3 | P5.0 | V <sub>DDB</sub>     | Vss      |

| E  | P7.6            | P1.0       | P0.7 | P0.6   | P1.1              | P1.5 | P3.1 | P5.1 | DP                   | VDDIO    |

| F  | P7.5            | (VDD12)    | P1.3 | (P1.2) | P1.4              | P3.0 | P3.5 | P3.7 | DM                   | P4.7     |

| G  | P7.4            | Vss        | P1.6 | P1.7   | P2.4              | P2.6 | P3.4 | P4.4 | P4.6                 | P4.5     |

| н  | (P7.3)          | VDDIO      | P2.1 | P2.2   | P2.5              | P2.7 | P3.2 | P4.1 | (P4.3)               | P4.2     |

| J  | P7.2            | Vss        | P2.0 | P2.3   | V <sub>DD18</sub> | Vss  | P3.3 | P3.6 | P4.0                 | P6.1     |

| К  | N.C.            | (P7.1)     | P7.0 | P6.7   | P6.6              | P6.5 | P6.4 | P6.3 | P6.2                 | N.C.     |

# **Bump Description**

| BUMP                   | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER PINS             | 1                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D9                     | V <sub>DDB</sub>   | USB Transceiver Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0 $\mu$ F capacitor as close as possible to the package.                                                                                                                                                                                                                                                                                                                                                            |

| F2                     | V <sub>DD12</sub>  | 1.2V Nominal Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0 $\mu$ F capacitor as close as possible to the package.                                                                                                                                                                                                                                                                                                                                                               |

| C9                     | V <sub>RTC</sub>   | RTC Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0 $\mu$ F capacitor as close as possible to the package.                                                                                                                                                                                                                                                                                                                                                                        |

| B4                     | V <sub>DDA</sub>   | Analog Supply Voltage. This pin must be bypassed to $V_{SSA}$ with a 1.0 $\mu$ F capacitor as close as possible to this pin.                                                                                                                                                                                                                                                                                                                                                                       |

| J5, A9                 | V <sub>DD18</sub>  | 1.8V Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0 $\mu$ F capacitor as close as possible to the package.                                                                                                                                                                                                                                                                                                                                                                       |

| H2, E10                | V <sub>DDIO</sub>  | I/O Supply Voltage. $1.8V \le V_{DDIO} \le 3.6V$ . See EC table for $V_{DDIO}$ specification. This pin must be bypassed to $V_{SS}$ with a $1.0\mu F$ capacitor as close as possible to the package.                                                                                                                                                                                                                                                                                               |

| A2                     | V <sub>DDIOH</sub> | I/O Supply Voltage, High. $1.8V \le V_{DDIOH} \le 3.6V$ , always with $V_{DDIOH} \ge V_{DDIO}$ . See EC table for $V_{DDIOH}$ specification. This pin must be bypassed to VSS with a $1.0\mu F$ capacitor as close as possible to the package.                                                                                                                                                                                                                                                     |

| A4                     | V <sub>REF</sub>   | ADC Reference. This pin must be left unconnected if an external reference is not used.                                                                                                                                                                                                                                                                                                                                                                                                             |

| B9, D10, G2,<br>J6, J2 | V <sub>SS</sub>    | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A3                     | V <sub>SSA</sub>   | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CLOCK PINS             |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C10                    | 32KOUT             | 32KHz Crystal Oscillator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B10                    | 32KIN              | 32kHz Crystal Oscillator Input. Connect a 6pF 32kHz crystal between 32KIN and 32KOUT for RTC operation. Optionally, an external clock source can be driven on 32KIN if the 32KOUT pin is left unconnected. A 32kHz crystal or external clock source is required for proper USB operation.                                                                                                                                                                                                          |

| USB PINS               |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E9                     | DP                 | USB DP Signal. This bidirectional pin carries the positive differential data or single-ended data. This pin is weakly pulled high internally when the USB is disabled.                                                                                                                                                                                                                                                                                                                             |

| F9                     | DM                 | USB DM Signal. This bidirectional pin carries the negative differential data or single-ended data. This pin is weakly pulled high internally when the USB is disabled.                                                                                                                                                                                                                                                                                                                             |

| JTAG PINS              |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B5                     | TCK/SWCLK          | JTAG Clock or Serial Wire Debug Clock. This pin has an internal 25K $\Omega$ pullup to $V_{DDIO}$ .                                                                                                                                                                                                                                                                                                                                                                                                |

| В6                     | TMS/SWDIO          | JTAG Test Mode Select or Serial Wire Debug I/O. This pin has an internal 25K $\Omega$ pullup to $V_{DDIO}$ .                                                                                                                                                                                                                                                                                                                                                                                       |

| B7                     | TDO                | JTAG Test Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B8                     | TDI                | JTAG Test Data Input. This pin has an internal 25kΩ pullup to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RESET PINS             |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B3 RSTN                |                    | Hardware Power Reset (Active-Low) Input. The device remains in reset while this pin is in its active state. When the pin transitions to its inactive state, the device performs a POR reset (resetting all logic on all supplies except for real-time clock circuitry) and begins execution. This pin is internally connected with an internal $25k\Omega$ pullup to the $V_{RTC}$ supply. This pin should be left unconnected if the system design does not provide a reset signal to the device. |

# **Bump Description (continued)**

| BUMP        | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B2          | SRSTN           | Software Reset, Active-Low Input/Output. The device remains in software reset while this pin is in its active state. When the pin transitions to its inactive state, the device performs a reset to the ARM core, digital registers and peripherals (resetting most of the core logic on the V <sub>DD12</sub> supply). This reset does not affect the POR only registers, RTC logic, ARM debug engine or JTAG debugger allowing for a soft reset without having to reconfigure all registers. |

|             |                 | After the device senses SRSTN as a logic 0, the pin automatically reconfigures as an output sourcing a logic 0. The device continues to output for 6 system clock cycles and then repeats the input sensing/output driving until SRSTN is sensed inactive.                                                                                                                                                                                                                                     |

|             |                 | This pin is internally connected with an internal $25k\Omega$ pullup to the $V_{DDIO}$ supply. This pin should be left unconnected if the system design does not provide a reset signal to the device.                                                                                                                                                                                                                                                                                         |

| GENERAL-PUR | POSE I/O AND SP | ECIAL FUNCTIONS (See the Applications Information section for GPIO Matrix)                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C3          | P0.0            | GPIO Port 0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C2          | P0.1            | GPIO Port 0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D5          | P0.2            | GPIO Port 0.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D4          | P0.3            | GPIO Port 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D2          | P0.4            | GPIO Port 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D3          | P0.5            | GPIO Port 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E4          | P0.6            | GPIO Port 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E3          | P0.7            | GPIO Port 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E2          | P1.0            | GPIO Port 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E5          | P1.1            | GPIO Port 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F4          | P1.2            | GPIO Port 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F3          | P1.3            | GPIO Port 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F5          | P1.4            | GPIO Port 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |