## Low-Power, Precision Instrumentation Amplifier with Programmable Gain

### **General Description**

The MAX41400 is a low-power, high-precision instrumentation amplifier with programmable gain through input pins.

Available in a space-saving, 9-bump wafer-level package (WLP) with a 0.4mm bump pitch, it is designed for use in portable medical and industrial sensor applications.

The device features internal EMI filters to protect from RF disturbances and EMI. The internal fixed gain can be selected from 10V/V to 250V/V. The gain-setting resistors are both inside the device, thus minimizing gain drift variations over the temperature range.

The MAX41400 features rail-to-rail CMOS inputs and outputs, a 28kHz -3dB bandwidth at just  $65\mu$ A (typ) supply current, and  $25\mu$ V (max) zero-drift input offset voltage over time and temperature. The zero-drift feature eliminates the high 1/f noise typically found in CMOS input amplifiers, making it useful for a wide variety of low-frequency measurement applications.

The MAX41400 operates from a 1.7V to 3.6V power supply voltage and is specified over the -40°C to +125°C automotive temperature range.

### **Applications**

- Low-Power Sensor Interface

- Pressure, Weigh, Force Sensors

- RTD Temperature Sensors

- Wearable Devices

- EKG Medical Devices

- Insulin and Infusion Pumps

#### **Benefits and Features**

- Supply Voltage Range: 1.7V to 3.6V

- Very Low 25μV (max) Input Offset Voltage

- Low 65µA Quiescent Current

- Rail-to-Rail Inputs and Outputs

- EMIRR

- >100dB at 1800MHz. 2400MHz

- >90dB at 400MHz, 900MHz

- 28kHz, -3dB Bandwidth

- Eight Input-Selectable Fixed-Gain Options

- 10V/V, 20V/V, 40V/V, 80V/V, 100V/V, 150V/V, 200V/V, and 250V/V

- Power-Saving Shutdown Mode

- Available in Tiny 1.26mm x 1.23mm, 9-Bump WLP and 2.5mm x 2mm, 10-Pin TDFN

Ordering Information appears at end of data sheet.

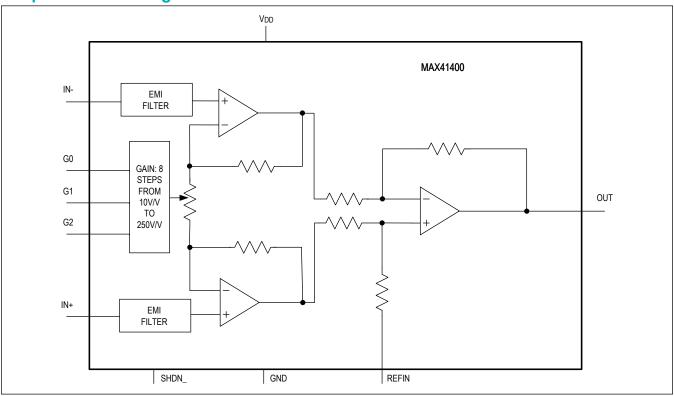

## **Simplified Block Diagram**

### **TABLE OF CONTENTS**

| General Description                                         | <br>1  |

|-------------------------------------------------------------|--------|

| Applications                                                | <br>1  |

| Benefits and Features                                       | <br>1  |

| Simplified Block Diagram                                    | <br>2  |

| Absolute Maximum Ratings                                    | <br>6  |

| Package Information                                         | <br>6  |

| Ultra-Thin WLP                                              | <br>6  |

| 10 TDFN                                                     | <br>6  |

| Electrical Characteristics                                  | <br>6  |

| Typical Operating Characteristics                           | <br>9  |

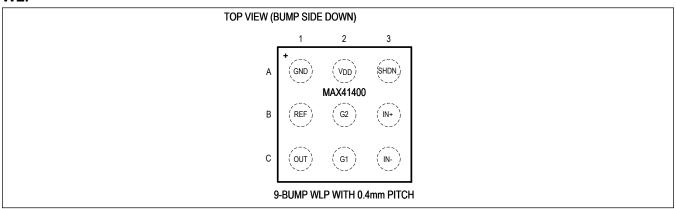

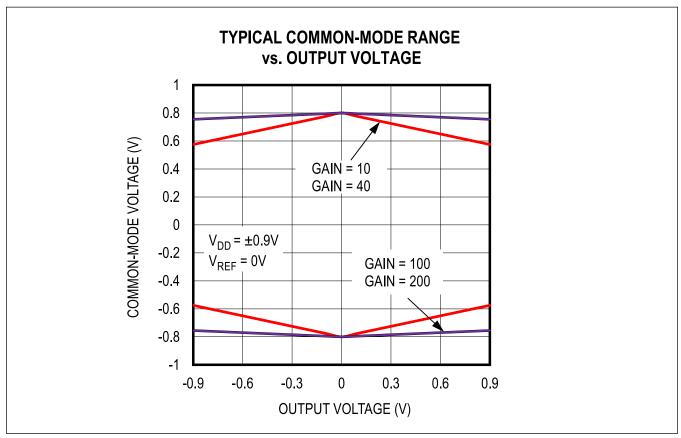

| Pin Configurations                                          | <br>12 |

| WLP                                                         | <br>12 |

| TDFN                                                        | <br>12 |

| Pin Description                                             | <br>12 |

| Detailed Description                                        | <br>13 |

| Gain-Selection Inputs                                       | <br>13 |

| Input Voltage Range                                         | <br>13 |

| Input Stage and Output Stage Gain Setting                   | <br>14 |

| Input Common-Mode Range vs. Output Voltage Characterization | <br>14 |

| Shutdown Mode                                               | <br>15 |

| External Noise Suppression in EMI Form                      | <br>15 |

| Input Offset Voltage                                        | <br>15 |

| External Offset Adjustment                                  | <br>15 |

| Applications Information                                    | <br>16 |

| Gain-Selection Input Logic                                  | <br>16 |

| Capacitive-Load Stability                                   | <br>16 |

| Power Supplies and Layout                                   | <br>16 |

| Transducer Applications                                     | <br>16 |

| Typical Application Circuits                                | <br>17 |

| Transducer Applications                                     | <br>17 |

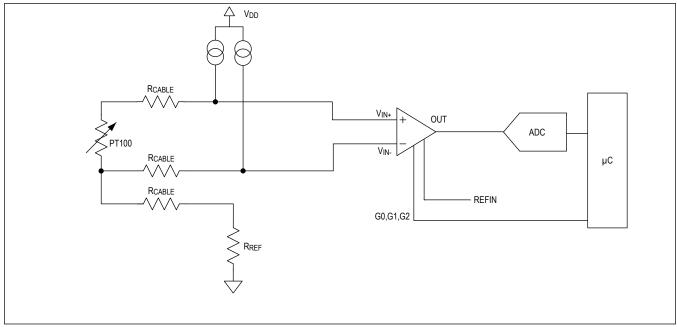

| PT100 Application                                           | <br>17 |

| Ordering Information                                        | <br>18 |

| Pavision History                                            | 10     |

# Low-Power, Precision Instrumentation Amplifier with Programmable Gain

| LIST OF FIGURES                                     |    |

|-----------------------------------------------------|----|

| Figure 1. MAX41400 Internal Configuration           |    |

| Figure 2. Common-Mode Input Range over Output Swing | 15 |

| Figure 3. Strain Gauge Connection to MAX41400       | 17 |

| Figure 4. Three-Wire PT100 Sensing Circuit          | 17 |

# Low-Power, Precision Instrumentation Amplifier with Programmable Gain

| LIST OF TABLES                             |      |

|--------------------------------------------|------|

| Table 1. Gain Selection (TDFN)             | . 13 |

| Table 2. Gain Selection (WLP)              | . 13 |

| Table 3. Input Stage and Output Stage Gain | . 14 |

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +4V                                                     | Continuous Power Dissipation (derate 11.91mW/°C above |

|---------------------------------------------------------------------------------------|-------------------------------------------------------|

| IN+ to IN0.3V to V <sub>DD</sub> + 0.3V                                               | +70°C)952.61mW                                        |

| OUT, REF to GND0.3V to V <sub>DD</sub> + 0.3V                                         | Operating Temperature Range40°C to +125°C             |

| IN+, IN-, G0, G1, G2, SHDN_ to GND0.3V to V <sub>DD</sub> + 0.3V                      | Junction Temperature+150°C                            |

| Continuous Current into any Input/Output Pin10mA                                      | Storage Temperature Range40°C to +150°C               |

| Output Short-Circuit Duration to Either $V_{\mbox{\scriptsize DD}}$ or GND Continuous | Soldering Temperature (reflow)+260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **Ultra-Thin WLP**

| Package Code                           | N91F1+1                        |  |  |

|----------------------------------------|--------------------------------|--|--|

| Outline Number                         | <u>21-100443</u>               |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |

| Thermal Resistance, Four-Layer Board:  |                                |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 83.98°C/W                      |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 24.60°C/W                      |  |  |

#### **10 TDFN**

| Package Code        | T102A2+2C        |

|---------------------|------------------|

| Outline Number      | <u>21-100013</u> |

| Land Pattern Number | 90-100007        |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(Global conditions unless otherwise stated:  $V_{DD}$  = 1.8V,  $V_{IN+}$  =  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ , G = 10V/V,  $R_{LOAD}$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $V_{SHDN}$  =  $V_{DD}$ , typical values at +25°C, -40°C ≤  $T_A$  ≤ +125°C)

| PARAMETER                  | SYMBOL            | CONDITIONS                         |                  | MIN | TYP | MAX                      | UNITS |

|----------------------------|-------------------|------------------------------------|------------------|-----|-----|--------------------------|-------|

| DC SPECIFICATIONS          |                   |                                    |                  |     |     |                          |       |

| Input Offset Voltage       | V/                | -40°C ≤ T <sub>A</sub> ≤ +85°C     | All gain options |     | 1   | 25                       | \     |

|                            |                   | -40°C ≤ T <sub>A</sub> ≤<br>+125°C | All gain options |     | 1   | 35                       | μV    |

| Input Offset Drift         | TCV <sub>OS</sub> |                                    |                  |     | 5   |                          | nV/°C |

|                            |                   | T <sub>A</sub> = +25°C             | Note 1           |     | 10  | 150                      |       |

| Input Bias Current         | Ι <sub>Β</sub>    | -40°C ≤ T <sub>A</sub> ≤<br>+125°C | Note 1           |     | 10  | 300                      | pА    |

| Input Offset Current       | los               | Note 1                             |                  |     | 10  |                          | pА    |

| Input Common-Mode<br>Range | V <sub>CM</sub>   | Guaranteed by CMRR                 |                  | 0.1 |     | V <sub>DD</sub> -<br>0.1 | V     |

## **Electrical Characteristics (continued)**

(Global conditions unless otherwise stated:  $V_{DD}$  = 1.8V,  $V_{IN+}$  =  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ , G = 10V/V,  $R_{LOAD}$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $V_{SHDN_-}$  =  $V_{DD}$ , typical values at +25°C, -40°C ≤  $T_A$  ≤ +125°C)

| PARAMETER                       | SYMBOL           | COND                                     | CONDITIONS                               |     | TYP                                                | MAX          | UNITS  |

|---------------------------------|------------------|------------------------------------------|------------------------------------------|-----|----------------------------------------------------|--------------|--------|

| Input ESD Protections           |                  | HBM, both IN+ and IN-                    |                                          |     | 2                                                  |              | kV     |

|                                 |                  |                                          | Gain = 10                                | 106 | 120                                                |              |        |

| Common-Mode<br>Rejection Ratio  | CMRR             | -40°C ≤ T <sub>A</sub> ≤<br>+125°C       | Gain = 40                                | 115 | 130                                                |              | dB     |

| Rejection Ratio                 |                  | 1123 0                                   | Gain = 100                               | 120 | 130                                                |              |        |

| Common Mode<br>Rejection Ratio  | CMRR             | -40°C ≤ T <sub>A</sub> ≤<br>+125°C       | Gain = 200                               | 120 | 130                                                |              | dB     |

|                                 |                  |                                          | Gain = 10                                | 98  | 110                                                |              |        |

| Power-Supply Rejection          | PSRR             | 1.7V ≤ V <sub>DD</sub> ≤ 3.6V            | Gain = 40                                | 110 | 120                                                |              | dB     |

| Ratio                           | PORK             | 1.7 V \( \text{VDD} \( \text{S} \) 3.6 V | Gain = 100                               | 113 | 130                                                |              | ] ub   |

|                                 |                  |                                          | Gain = 200                               | 113 | 130                                                |              |        |

| Range of Gain                   | G                |                                          |                                          | 10  | WLP:<br>40, 100,<br>200<br>TDFN:<br>20, 80,<br>150 | TDFN:<br>250 | V/V    |

| Gain Selection Settling<br>Time |                  | V <sub>OUT</sub> to settle within        | V <sub>OUT</sub> to settle within ±100mV |     | 20                                                 |              | μs     |

| Gain Error                      | GE               | -40°C ≤ T <sub>A</sub> ≤<br>+125°C       | All gain options                         |     | 0.05                                               | 0.18         | %      |

| Gain Error Tempco               | TC <sub>GE</sub> |                                          |                                          |     | 5                                                  |              | ppm/°C |

| Output Voltage Swing<br>High    | $V_{OH}$         | V <sub>DD</sub> - V <sub>OUT</sub>       | $R_{LOAD}$ = 10kΩ to $V_{DD}/2$          |     |                                                    | 50           | mV     |

| Output Voltage Swing<br>Low     | V <sub>OL</sub>  | V <sub>OUT</sub> - GND                   | $R_{LOAD}$ = 10kΩ to $V_{DD}/2$          |     |                                                    | 25           | mV     |

| INPUT REFERENCE                 |                  |                                          |                                          |     |                                                    |              |        |

| Input Reference Voltage Range   | $V_{REFIN}$      |                                          |                                          | 0   |                                                    | $V_{DD}$     | V      |

| AC SPECIFICATIONS               |                  |                                          |                                          |     |                                                    |              |        |

|                                 |                  | Gain = 10                                |                                          |     | 28                                                 |              |        |

| Bandwidth, -3dB                 |                  | Gain = 40                                |                                          |     | 28                                                 |              | kHz    |

|                                 |                  | Gain = 100                               |                                          |     | 10                                                 |              | KHZ    |

|                                 |                  | Gain = 200                               | Gain = 200                               |     | 5                                                  |              |        |

| Slew Rate                       | SR               |                                          |                                          |     | 0.08                                               |              | V/µs   |

## **Electrical Characteristics (continued)**

(Global conditions unless otherwise stated:  $V_{DD}$  = 1.8V,  $V_{IN+}$  =  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ , G = 10V/V,  $R_{LOAD}$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $V_{SHDN}$  =  $V_{DD}$ , typical values at +25°C, -40°C ≤  $T_A$  ≤ +125°C)

| WLP:<br>  G = 10V/V<br>  G = 40V/V<br>  G = 100V/V<br>  F = 10Hz, 1kHz, G = 200V/V<br>  G = 200V/V           | WLP:<br>54<br>38<br>41        |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|

| Density 10kHz TDFN: G = 20V/V G = 80V/V G = 150V/V G = 250V/V                                                | 36<br>TDFN:<br>47<br>46<br>43 |  |  |  |  |  |

| Input Voltage Noise 0.1Hz to 10Hz, gain = 10                                                                 | 1.3 µV <sub>P-I</sub>         |  |  |  |  |  |

| V <sub>RFPEAK</sub> = 100mV <sub>P-P</sub> , f = 400MH<br>900MHz, both IN+ and IN-                           | Hz, >90 dB                    |  |  |  |  |  |

| $V_{RFPEAK}$ = 100mV <sub>P-P</sub> , f = 1800M<br>2400MHz, both IN+ and IN-                                 | IHz, >100                     |  |  |  |  |  |

| Input Current-Noise Density I <sub>N</sub>                                                                   | 100 fA/√H                     |  |  |  |  |  |

| Capacitive Loading Stability C <sub>L</sub>                                                                  | 100 pF                        |  |  |  |  |  |

| POWER SUPPLY                                                                                                 |                               |  |  |  |  |  |

| Supply Voltage V <sub>DD</sub> Guaranteed by PSRR, -40°C ≤ T <sub>A</sub> +125°C                             | 1.7 3.6 V                     |  |  |  |  |  |

| Supply Current I <sub>DD</sub>                                                                               | 65 90 μA                      |  |  |  |  |  |

| Power-Up Time $t_{ON}$ $V_{OUT}$ to settle within 90% $v_{DD} = 0$ to $v_{DD} = 0$                           | 1.8V 100 μs                   |  |  |  |  |  |

| Shutdown Supply $I_{SHDN}$ $-40^{\circ}C \le T_{A} \le +125^{\circ}C$                                        | 0.1 1.3 μA                    |  |  |  |  |  |

| Turn-On Time $t_{ONSD}$ $v_{OUT}$ to settle within 90% $v_{SHDN} = 0$ to step in <1 $\mu$ step in <1 $\mu$ s | to 1.8V 100 μs                |  |  |  |  |  |

| LOGIC INPUTS DC CHARACTERISTICS                                                                              |                               |  |  |  |  |  |

| Input Low Level V <sub>IL</sub> Active level                                                                 | 0.3 x<br>V <sub>DD</sub> V    |  |  |  |  |  |

| Input High Level V <sub>IH</sub>                                                                             | 0.7 x<br>V <sub>DD</sub> V    |  |  |  |  |  |

| Input Leakage Current I <sub>L</sub>                                                                         | 18 nA                         |  |  |  |  |  |

Note 1: Guaranteed by design and characterization.

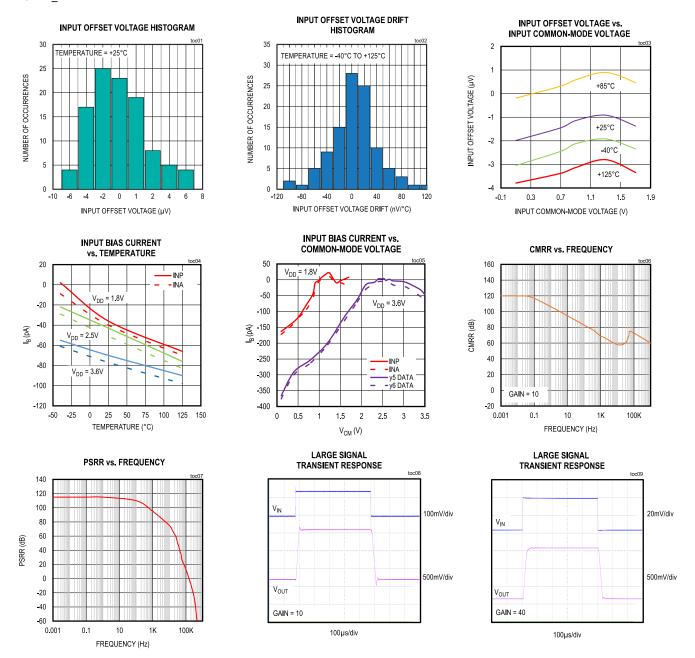

### **Typical Operating Characteristics**

(Global conditions unless otherwise stated:  $V_{DD}$  = 1.8V,  $V_{IN+}$  =  $V_{ID-}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $V_{SHDN}$  =  $V_{DD}$ , typical values at +25°C, -40°C ≤  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{$

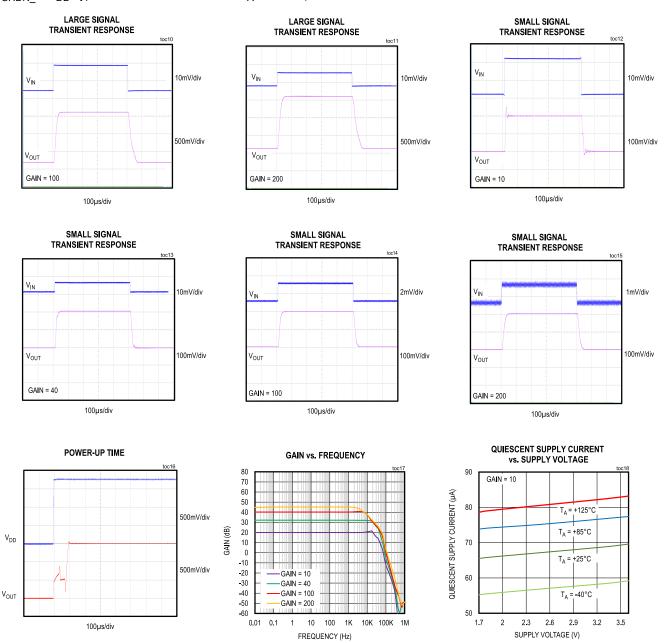

### **Typical Operating Characteristics (continued)**

(Global conditions unless otherwise stated:  $V_{DD}$  = 1.8V,  $V_{IN+}$  =  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ , G = 10V/V,  $R_{LOAD}$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $V_{SHDN}$  =  $V_{DD}$ , typical values at +25°C, -40°C ≤  $T_A$  ≤ +125°C)

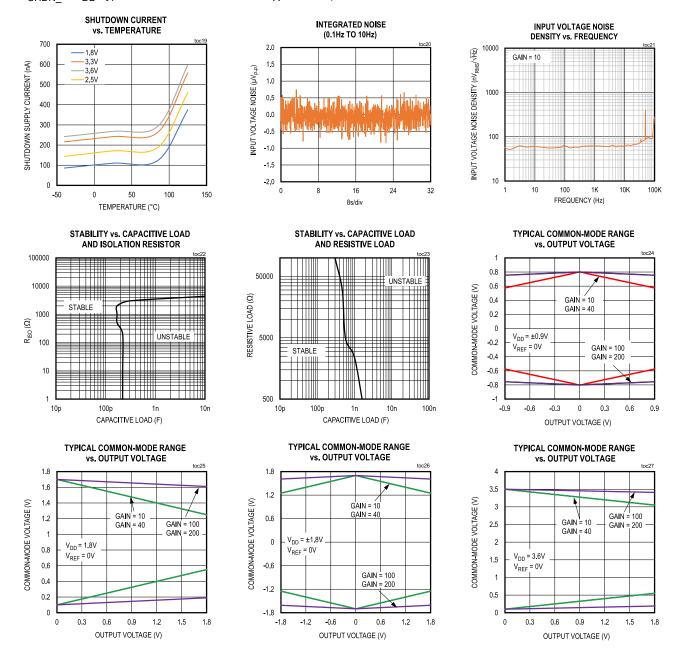

### **Typical Operating Characteristics (continued)**

(Global conditions unless otherwise stated:  $V_{DD}$  = 1.8V,  $V_{IN+}$  =  $V_{ID-}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $V_{SHDN}$  =  $V_{DD}$ , typical values at +25°C, -40°C ≤  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{CAD}$  = 1.8V,  $V_{IN+}$  =  $V_{DD}/2$ ,  $V_{REFIN}$  =  $V_{DD}/2$ ,  $V_{$

## **Pin Configurations**

#### **WLP**

### **TDFN**

## **Pin Description**

| Р   | IN   | NAME     | FUNCTION                                                                                                                                                                |  |

|-----|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WLP | TDFN | NAME     | FUNCTION                                                                                                                                                                |  |

| В3  | 3    | IN+      | Noninverting Input                                                                                                                                                      |  |

| A1  | 10   | GND      | Ground                                                                                                                                                                  |  |

| C3  | 4    | IN-      | Inverting Input                                                                                                                                                         |  |

| A2  | 1    | $V_{DD}$ | Positive Supply                                                                                                                                                         |  |

| C1  | 8    | OUT      | Output                                                                                                                                                                  |  |

| A3  | 2    | SHDN_    | Shutdown (active low)                                                                                                                                                   |  |

| B1  | 9    | REF      | Input Reference                                                                                                                                                         |  |

| _   | 7    | G0       | Gain Selection Input. Connect to either V <sub>DD</sub> or GND. The gain selection is bas on the appropriate gain selection table in the <u>Detailed Description</u> .  |  |

| C2  | 6    | G1       | Gain Selection Input. Connect to either V <sub>DD</sub> or GND. The gain selection is base on the appropriate gain selection table in the <u>Detailed Description</u> . |  |

| B2  | 5    | G2       | Gain Selection Input. Connect to either $V_{DD}$ or GND. The gain selection is based on the appropriate gain selection table in the <u>Detailed Description</u> .       |  |

### **Detailed Description**

The MAX41400 is a programmable-gain precision instrumentation amplifier based on a traditional three-amplifier topology. The input stage is composed of two operational amplifiers that together provide a high common-mode rejection ratio, low input bias current, and low input offset voltage. The output stage is a conventional differential amplifier that provides an overall common-mode rejection of 130dB (G = +10V/V).

The amplifier has on-chip gain-setting resistors and the gains are selectable through input pins. On-chip trimming of internal gain-setting resistors helps optimize gain error, CMRR, and offset. Since all gain-setting resistors are within the device, this minimizes gain drift variation over the temperature range and saves design time and space.

#### **Gain-Selection Inputs**

Three inputs are used to select the internal gain for the TDFN package option. Each input can be connected to either GND or  $V_{DD}$ .

The WLP option supports only two inputs that limits gain selection to four options.

**Table 1. Gain Selection (TDFN)**

| PACKAGE | G2                | G1       | G0                | GAIN (V/V) |

|---------|-------------------|----------|-------------------|------------|

|         | GND               | GND      | GND               | 10         |

|         | GND               | GND      | $V_{DD}$          | 20         |

|         | GND               | $V_{DD}$ | GND               | 40         |

| TDEN    | GND               | $V_{DD}$ | $V_{DD}$          | 80         |

| TDFN    | $V_{\mathrm{DD}}$ | GND      | GND               | 100        |

|         | V <sub>DD</sub>   | GND      | $V_{\mathrm{DD}}$ | 150        |

|         | V <sub>DD</sub>   | $V_{DD}$ | GND               | 200        |

|         | $V_{\mathrm{DD}}$ | $V_{DD}$ | $V_{\mathrm{DD}}$ | 250        |

Table 2. Gain Selection (WLP)

| PACKAGE | G2              | G1              | GAIN (V/V) |

|---------|-----------------|-----------------|------------|

| WLP     | GND             | GND             | 10         |

|         | GND             | V <sub>DD</sub> | 40         |

|         | $V_{DD}$        | GND             | 100        |

|         | V <sub>DD</sub> | V <sub>DD</sub> | 200        |

#### Input Voltage Range

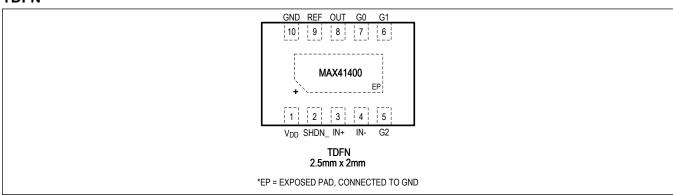

The common-mode input range for all of these amplifiers is  $(V_{SS} + 0.1V)$  to  $(V_{DD} - 0.1V)$ . Ideally, the instrumentation amplifier responds only to a differential voltage applied to its inputs, IN+ and IN-. If both inputs are at the same voltage, the output is  $V_{REF}$ . A differential voltage at IN+  $(V_{IN+})$  and IN-  $(V_{IN-})$  develops an identical voltage across the gain-setting resistor, causing a current (I<sub>G</sub>) to flow. This current also flows through the feedback resistors of the two input amplifiers A1 and A2, generating a differential voltage of:

$V_{OUT2} - V_{OUT1} = I_G x (R1 + R_G + R1)$

where  $V_{OUT1}$  and  $V_{OUT2}$  are the output voltages of A1 and A2,  $R_G$  is the gain-setting resistor, and R1 is the feedback resistor of the input amplifiers.

I<sub>G</sub> is determined by the following equation:

$I_G = (V_{IN+} - V_{IN-})/R_G$

The output voltage (V<sub>OUT</sub>) for the instrumentation amplifier is expressed in the following equation:

$$V_{OUT} = (V_{IN+} - V_{IN-} \times (2 \times \frac{R1}{R_G} + 1) \times \frac{R3}{R2}$$

The common-mode input range is a function of the amplifier's output voltage and the supply voltage. With a power supply of  $V_{DD}$ , the largest output signal swing can be obtained with REF tied to  $V_{DD}/2$ . This results in an output-voltage swing of  $\pm V_{DD}/2$ . An output-voltage swing less than full scale increases the common-mode input range.

Figure 1. MAX41400 Internal Configuration

#### Input Stage and Output Stage Gain Setting

When R2 and R3 are not equally set at the output stage, the MAX41400's gain is determined by both gain of input stage (A1) and output stage (A2) amplifiers. At a different gain setting, internal R1,  $R_G$ , R2, and R3 are selected respectively. Table 3 shows the input and output stage gain settings with respect to the total gain of the MAX41400.

| Table 3   | Innut S  | Stage and C | Dutnut 9 | Stage ( | ain  |

|-----------|----------|-------------|----------|---------|------|

| I able 5. | IIIDUL V | Jiauc anu v | Julbul   | Jiaut ( | Jani |

|          |                 | •               |                   |                    |      |

|----------|-----------------|-----------------|-------------------|--------------------|------|

| G2       | G1              | G0              | GAIN1 INPUT STAGE | GAIN2 OUTPUT STAGE | GAIN |

| GND      | GND             | GND             | 5                 | 2                  | 10   |

| GND      | GND             | $V_{DD}$        | 10                | 2                  | 20   |

| GND      | V <sub>DD</sub> | GND             | 20                | 2                  | 40   |

| GND      | V <sub>DD</sub> | V <sub>DD</sub> | 8                 | 10                 | 80   |

| $V_{DD}$ | GND             | GND             | 10                | 10                 | 100  |

| $V_{DD}$ | GND             | $V_{DD}$        | 15                | 10                 | 150  |

| $V_{DD}$ | $V_{DD}$        | GND             | 20                | 10                 | 200  |

| $V_{DD}$ | V <sub>DD</sub> | $V_{DD}$        | 25                | 10                 | 250  |

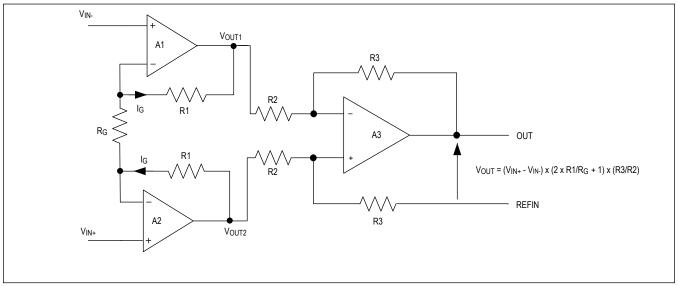

#### Input Common-Mode Range vs. Output Voltage Characterization

Common-Mode Input Range over Output Swing illustrates the MAX41400's typical common-mode input voltage range over the output voltage swing at a different gain. Although the common-mode input range for all three amplifiers is  $V_{SS}$  + 0.1V) to ( $V_{DD}$  - 0.1V), the common-mode input voltage range of MAX41400 is changed with the amplifier's output voltage and gain setting. The reason is, as the input stage's operational amplifiers A1 and A2 amplify the differential input voltage, the common-mode input voltage range of the MAX41400 is limited by the output stage differential amplifier's linear input range. For example, with gain = 10, when the output voltage is 0.9V, the MAX41400's common-mode input

voltage range is determined by the input range of the output amps ( $\pm 0.8V$ ) minus the amplified differential input amplitude at the output amps ( $\pm 0.225V$ ). For a higher gain configuration, the  $V_{CM}$  range will increase, since a smaller differential voltage is necessary for the given output voltage.

Figure 2. Common-Mode Input Range over Output Swing

#### **Shutdown Mode**

The MAX41400 features a low-power shutdown mode. When the shutdown pin  $(\overline{SHDN})$  is pulled low, the internal amplifiers are switched off and the supply current drops to  $0.1\mu A$ , typ. This disables the instrumentation amplifier and puts its output in a high-impedance state. Pulling  $\overline{SHDN}$  high enables the instrumentation amplifier.

#### **External Noise Suppression in EMI Form**

The MAX41400 has input EMI filters to prevent effects of radio frequency interference on the output. The EMI filters comprise passive devices that present significantly higher impedance to higher frequency signals.

#### **Input Offset Voltage**

The MAX41400 features a chop structure, which reduces input offset voltage and 1/f noise while reducing the output ripple typically associated with chopping circuits. The output stage resistor bridge is carefully trimmed to reduce the offset introduced by the mismatch of the resistor network.

#### **External Offset Adjustment**

If necessary, external offset can be adjusted by applying a voltage at the REF pin. The voltage applied at the REF pin is required to have a low output impedance (i.e., lower than  $10\Omega$ ) in order to provide high common-mode rejection.

### **Applications Information**

#### **Gain-Selection Input Logic**

The MAX41400 features a digitally adjustable gain-selection input (G0,G1,G2), which allows changing the instrumentation amplifier gain without an external gain setting resistor, thus minimizing gain drift variation over the temperature range and saving design time and space.

Input low level  $(V_{IL})$  and input high level  $(V_{IH})$  determine the threshold for gain-selection input to recognize a valid logic state. With three gain-selection inputs (TDFN) and two gain-selection inputs (WLP) available, the MAX41400 supports eight gain settings (TDFN) and four gain settings (WLP) respectively.

The logic state of the gain-selection input can be achieved by connecting the input pin to either GND or  $V_{DD}$  or can be controlled by a microcontroller. Note that the logic threshold is referred to the negative supply rail of the MAX41400 for dual-supply operation.

#### **Capacitive-Load Stability**

The MAX41400 is stable for capacitive loads up to 100pF. Applications that require greater capacitive-load driving capability can use an isolation resistor between the output and the capacitive load to reduce ringing on the output signal. However, this alternative reduces gain accuracy because R<sub>ISO</sub> forms a potential divider with the load resistor.

#### **Power Supplies and Layout**

The MAX41400 operates either with s single supply from +1.7V to +3.6V with respect to ground or with dual supplies from ±0.85V to ±1.8V. For best performance, bypass each power supply to ground with a separate 0.1µF capacitor.

Good layout technique optimizes performance by decreasing the amount of stray capacitance at the instrumentation amplifier's input. Excess capacitance will produce peaking in the amplifier's frequency response. To decrease stray capacitance, minimize trace lengths by placing external components as close to the instrumentation amplifier as possible.

#### **Transducer Applications**

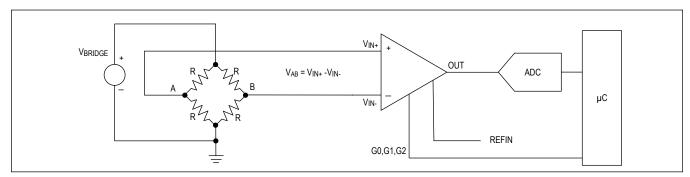

The MAX41400 can be used in various signal-conditioning circuits for thermocouples, PT100s, strain gauges (displacement sensors), piezoresistive transducers (PRTs), flow sensors, and bioelectrical applications. Figure 3 shows a simplified example of how to attach four strain gauges (two identical two-element strain gauges) to the inputs of the MAX41400. The bridge contains four resistors, two of which increase and two of which decrease by the same ratio.

With a fully balanced bridge, points A (IN+) and B (IN-) see half of the the excitation voltage ( $V_{BRIDGE}$ ). The low impedance ( $120\Omega$  to  $350\Omega$ ) of the strain gauges, however, could cause significant voltage drop contributions by the wires leading to the bridge, which would cause excitation variations. The output voltage  $V_{OUT}$  can be calculated as follows:

$V_{OLIT} = V_{AB} \times G$

where G is the gain of the MAX41400.

## **Typical Application Circuits**

### **Transducer Applications**

Figure 3. Strain Gauge Connection to MAX41400

## PT100 Application

Figure 4. Three-Wire PT100 Sensing Circuit

## **Ordering Information**

| PART NUMBER    | TEMP RANGE      | PIN-PACKAGE | TOP MARKING |

|----------------|-----------------|-------------|-------------|

| MAX41400ANL+   | -40°C to +125°C | 9 WLP       | +AAS        |

| MAX41400ANL+T  | -40°C to +125°C | 9 WLP       | +AAS        |

| MAX41400ATB+*  | -40°C to +125°C | 10 TDFN     | +AZN        |

| MAX41400ATB+T* | -40°C to +125°C | 10 TDFN     | +AZN        |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T = tape-and-reel.

<sup>\*</sup> Future product—contact factory for availability.

# Low-Power, Precision Instrumentation Amplifier with Programmable Gain

### **Revision History**

| REVISION NUMBE |       | DESCRIPTION       | PAGES<br>CHANGED |

|----------------|-------|-------------------|------------------|

| 0              | 10/20 | Release for intro | _                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.