# 24-Bit, 8.5 mW, 109 dB, 128 kSPS/64 kSPS/32 kSPS ADCs

## **FEATURES**

- Oversampled successive approximation (SAR) architecture

- ▶ High performance ac and dc accuracy, low power

- ▶ 115.5 dB dynamic range, 32 kSPS (AD7766-2)

- ▶ 112.5 dB dynamic range, 64 kSPS (AD7766-1)

- ▶ 109.5 dB dynamic range, 128 kSPS (AD7766)

- ▶ -112 dB THD

- ► Exceptionally low power

- ▶ 8.5 mW, 32 kSPS (AD7766-2)

- ▶ 10.5 mW, 64 kSPS (AD7766-1)

- ▶ 15 mW, 128 kSPS (AD7766)

- High dc accuracy

- ▶ 24 bits, no missing codes (NMC)

- ▶ INL: ±6 ppm (typical), ±15 ppm (maximum)

- ▶ Low temperature drift

- ► Zero error drift: 15 nV/°C

- ▶ Gain error drift: 0.4 ppm/°C

- ▶ On-chip low-pass FIR filter

- ▶ Linear phase response

- ▶ Pass-band ripple: ±0.005 dB

- Stop-band attenuation: 100 dB

- ≥ 2.5 V supply with 1.8 V/2.5 V/3 V/3.6 V logic interface options and 5 V reference

- ► Flexible interfacing options

- Synchronization of multiple devices

- ▶ Daisy-chain capability

- ▶ Power-down function

- ► Temperature range: -40°C to +105°C

- ▶ Available in 4.4 mm × 5 mm, 16-lead TSSOP

## **APPLICATIONS**

- ▶ Low power PCI/USB data acquisition systems

- Low power wireless acquisition systems

- ▶ Vibration analysis

- Instrumentation

- ▶ High precision medical acquisition

## **RELATED DEVICES**

Table 1. 24-Bit ADCs

| Part No. | Description                                                          |

|----------|----------------------------------------------------------------------|

| AD7760   | 2.5 MSPS, 100 dB dynamic range, 1 on-board differential amp and      |

|          | reference buffer, parallel, variable decimation                      |

| AD7762/  | 625 kSPS, 109 dB dynamic range, 1 on-board differential amp and      |

| AD7763   | reference buffer, parallel/serial, variable decimation               |

| AD7764   | 312 kSPS, 109 dB dynamic range, 1 on-board differential amp and      |

|          | reference buffer, variable decimation (pin)                          |

| AD7765   | 156 kSPS, 112 dB dynamic range, 1 on-board differential amp and      |

|          | reference buffer, variable decimation (pin)                          |

| AD7767   | 128 kSPS, 109.5 dB, <sup>1</sup> 15 mW, 18-bit INL, serial interface |

| AD7767-1 | 64 kSPS 112.5 dB, 1 10.5 mW, 18-bit INL, serial interface            |

| AD7767-2 | 32 kSPS, 115.5 dB, <sup>1</sup> 8.5 mW, 18-bit INL, serial interface |

Dynamic range at maximum output data rate.

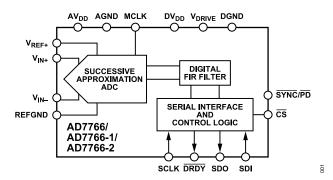

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

**Data Sheet**

# **TABLE OF CONTENTS**

| Features1                                           | AD7766/AD7766-1/AD77662-2 Interface    | 17 |

|-----------------------------------------------------|----------------------------------------|----|

| Applications1                                       | Initial Power-Up                       | 17 |

| Related Devices1                                    | Reading Data                           | 17 |

| Functional Block Diagram1                           | Power-Down, Reset, and Synchronization | 17 |

| General Description3                                | Daisy Chaining                         |    |

| Specifications4                                     | Reading Data in Daisy-Chain Mode       | 18 |

| Timing Specifications 6                             | Choosing the SCLK Frequency            | 18 |

| Timing Diagrams7                                    | Daisy-Chain Mode Configuration and     |    |

| Absolute Maximum Ratings8                           | Timing Diagrams                        | 19 |

| ESD Caution8                                        | Driving the AD7766/AD7766-1/AD7766-2   |    |

| Pin Configuration and Function Descriptions 9       | Differential Signal Source             | 20 |

| Typical Performance Characteristics                 | Single-Ended Signal Source             | 20 |

| Terminology14                                       | Antialiasing                           |    |

| Theory of Operation15                               | Power Dissipation                      |    |

| AD7766/AD7766-1/AD7766-2 Transfer                   | V <sub>REF+</sub> Input Signal         | 22 |

| Function15                                          | Multiplexing Analog Input Channels     |    |

| Converter Operation15                               | Outline Dimensions                     | 23 |

| Analog Input Structure16                            | Ordering Guide                         | 23 |

| Supply and Reference Voltages16                     | Evaluation Boards                      | 23 |

| REVISION HISTORY                                    |                                        |    |

| 6/2024—Rev. C to Rev. D                             |                                        |    |

| Changed Master to Main (Throughout)                 |                                        |    |

| Changes to Features Section                         |                                        |    |

| Moved General Description Section                   |                                        |    |

| Change to Specifications Section                    |                                        |    |

| Changes to Group Delay Parameter and Settling Tir   |                                        |    |

| Changes to t <sub>SETTLING</sub> Parameter, Table 3 |                                        |    |

| Change to Typical Performance Characteristics Sec   |                                        |    |

| Changes to Table 7                                  |                                        | 17 |

analog.com Rev. D | 2 of 23

## **GENERAL DESCRIPTION**

The AD7766/AD7766-1/AD7766-2 are high performance, 24-bit, oversampled SAR analog-to-digital converters (ADCs). The AD7766/AD7766-1/AD7766-2 combine the benefits of a large dynamic range and input bandwidth, consuming 15 mW, 10.5 mW, and 8.5 mW power, respectively, and are contained in a 16-lead TSSOP package.

Ideal for ultralow power data acquisition (such as PCI- and USB-based systems), the AD7766/AD7766-1/AD7766-2 provide 24-bit resolution. The combination of exceptional SNR, wide dynamic range, and outstanding dc accuracy make the AD7766/AD7766-1/AD7766-2 ideally suited for measuring small signal changes over a wide dynamic range. This is particularly suitable for applications where small changes on the input are measured on larger ac or dc signals. In such an application, the AD7766/AD7766-1/AD7766-2 accurately gather both ac and dc information.

The AD7766/AD7766-1/AD7766-2 include an on-board digital filter (complete with linear phase response) that acts to eliminate out-of-band noise by filtering the oversampled input voltage. The oversampled architecture also reduces front-end antialias requirements. Other features of the AD7766/AD7766-1/AD7766-2 include a \$\overline{\text{SYNC/PD}}\$ (synchronization/power-down) pin, allowing the synchronization of multiple AD7766/AD7766-1/AD7766-2 devices. The addition of an SDI pin provides the option of daisy chaining multiple AD7766/AD7766-1/AD7766-2 devices.

The AD7766/AD7766-1/AD7766-2 operate from a 2.5 V supply using a 5 V reference. The devices operate from −40°C to +105°C.

analog.com Rev. D | 3 of 23

# **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 2.5 \text{ V} \pm 5\%$ ,  $V_{DRIVE} = 1.8 \text{ V}$  to 3.6 V,  $V_{REF+} = 5 \text{ V}$ , MCLK = 1.024 MHz, common-mode input =  $V_{REF+}/2$ ,  $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , unless otherwise noted.

Table 2.

| Parameter                                       | Test Conditions/Comments               | Min                       | Тур                  | Max                       | Unit     |

|-------------------------------------------------|----------------------------------------|---------------------------|----------------------|---------------------------|----------|

| OUTPUT DATA RATE (ODR)                          |                                        |                           | -                    |                           |          |

| AD7766                                          | Decimate by 8                          |                           |                      | 128                       | kHz      |

| AD7766-1                                        | Decimate by 16                         |                           |                      | 64                        | kHz      |

| AD7766-2                                        | Decimate by 32                         |                           |                      | 32                        | kHz      |

| ANALOG INPUT <sup>1</sup>                       | ,                                      |                           |                      |                           |          |

| Differential Input Voltage                      | V <sub>IN+</sub> - V <sub>IN-</sub>    |                           |                      | $\pm V_{REF+}$            | V p-p    |

| Absolute Input Voltage                          | V <sub>IN+</sub>                       | -0.1                      |                      | +V <sub>REF+</sub> + 0.1  | \v''     |

| 1 3                                             | V <sub>IN</sub> -                      | -0.1                      |                      | +V <sub>REF+</sub> + 0.1  | V        |

| Common-Mode Input Voltage                       | "                                      | V <sub>REF+</sub> /2 - 5% | V <sub>REF+</sub> /2 | V <sub>REF+</sub> /2 + 5% | V        |

| Input Capacitance                               |                                        | IXELL                     | 22                   | KLI                       | pF       |

| DYNAMIC PERFORMANCE                             |                                        |                           |                      |                           | <u>'</u> |

| AD7766                                          | Decimate by 8, ODR = 128 kHz           |                           |                      |                           |          |

| Dynamic Range <sup>2</sup>                      | Shorted inputs                         | 108                       | 109.5                |                           | dB       |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>        | Full-scale input amplitude, 1 kHz tone | 107                       | 108.5                |                           | dB       |

| Spurious-Free Dynamic Range (SFDR) <sup>2</sup> | Full-scale input amplitude, 1 kHz tone |                           | -128                 | -116                      | dB       |

| Total Harmonic Distortion (THD) <sup>2</sup>    | Full-scale input amplitude, 1 kHz tone |                           | -112                 | -103                      | dB       |

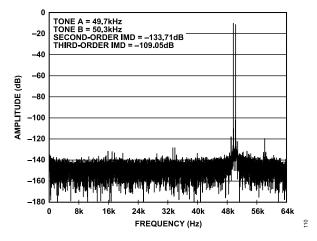

| Intermodulation Distortion (IMD) <sup>2</sup>   | Tone A = 49.7 kHz, Tone B = 50.3 kHz   |                           |                      |                           |          |

| Second-Order Terms                              | ,                                      |                           | -133                 |                           | dB       |

| Third-Order Terms                               |                                        |                           | -109                 |                           | dB       |

| AD7766-1                                        | Decimate by 16, ODR = 64 kHz           |                           |                      |                           |          |

| Dynamic Range <sup>2</sup>                      | Shorted inputs                         | 111                       | 112.5                |                           | dB       |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>        | Full-scale input amplitude, 1 kHz tone | 110                       | 111.5                |                           | dB       |

| Spurious-Free Dynamic Range (SFDR) <sup>2</sup> | Full-scale input amplitude, 1 kHz tone |                           | -128                 | -116                      | dB       |

| Total Harmonic Distortion (THD) <sup>2</sup>    | Full-scale input amplitude, 1 kHz tone |                           | -112                 | -103                      | dB       |

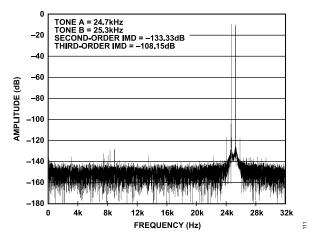

| Intermodulation Distortion (IMD) <sup>2</sup>   | Tone A = 24.7 kHz, Tone B = 25.3 kHz   |                           |                      |                           | dB       |

| Second-Order Terms                              |                                        |                           | -133                 |                           | dB       |

| Third-Order Terms                               |                                        |                           | -108                 |                           | dB       |

| AD7766-2                                        | Decimate by 32, ODR = 32 kHz           |                           |                      |                           |          |

| Dynamic Range <sup>2</sup>                      | Shorted inputs                         | 114                       | 115.5                |                           | dB       |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>        | Full-scale input amplitude, 1 kHz tone | 112                       | 113.5                |                           | dB       |

| Spurious-Free Dynamic Range (SFDR) <sup>2</sup> | Full-scale input amplitude, 1 kHz tone |                           | -128                 | -116                      | dB       |

| Total Harmonic Distortion (THD) <sup>2</sup>    | Full-scale input amplitude, 1 kHz tone |                           | -112                 | -103                      | dB       |

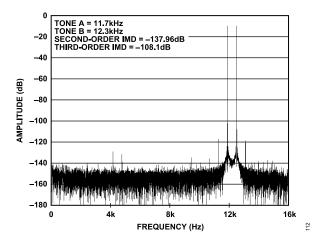

| Intermodulation Distortion (IMD) <sup>2</sup>   | Tone A = 11.7 kHz, Tone B = 12.3 kHz   |                           |                      |                           | dB       |

| Second-Order Terms                              |                                        |                           | -137                 |                           | dB       |

| Third-Order Terms                               |                                        |                           | -108                 |                           | dB       |

| DC ACCURACY <sup>1</sup>                        | For all devices                        |                           |                      |                           |          |

| Resolution                                      | No missing codes                       | 24                        |                      |                           | Bits     |

| Differential Nonlinearity <sup>2</sup>          | Guaranteed monotonic to 24 bits        |                           |                      |                           |          |

| Integral Nonlinearity <sup>2</sup>              | 16-bit linearity                       |                           | ±6                   | ±15                       | ppm      |

| Zero Error <sup>2</sup>                         |                                        |                           | 20                   |                           | μV       |

| Gain Error <sup>2</sup>                         |                                        |                           | 0.0075               | 0.075                     | % FS     |

| Zero Error Drift <sup>2</sup>                   |                                        |                           | 15                   | •                         | nV/°C    |

| Gain Error Drift <sup>2</sup>                   |                                        |                           | 0.4                  |                           | ppm/°C   |

| Common-Mode Rejection Ratio <sup>2</sup>        | 50 Hz tone                             |                           | -110                 |                           | dB       |

analog.com Rev. D | 4 of 23

# **SPECIFICATIONS**

Table 2. (Continued)

| Parameter                                  | Test Conditions/Comments                    | Min                      | Тур         | Max                       | Unit   |

|--------------------------------------------|---------------------------------------------|--------------------------|-------------|---------------------------|--------|

| DIGITAL FILTER RESPONSE <sup>1</sup>       |                                             |                          |             |                           |        |

| Group Delay                                |                                             |                          | 37/ODR      |                           |        |

| Settling Time (Latency)                    | Complete settling                           |                          | 74/ODR      |                           |        |

| Pass-Band Ripple                           |                                             |                          |             | ±0.005                    | dB     |

| Pass Band                                  |                                             |                          | 0.453 × ODR |                           | Hz     |

| −3 dB Bandwidth                            |                                             |                          | 0.49 × ODR  |                           | Hz     |

| Stop-Band Frequency                        |                                             |                          | 0.547 × ODR |                           | Hz     |

| Stop-Band Attenuation                      |                                             | 100                      |             |                           | dB     |

| REFERENCE INPUT <sup>1</sup>               |                                             |                          |             |                           | "-     |

| V <sub>REF+</sub> Input Voltage            |                                             | 2.4                      |             | 2 × AV <sub>DD</sub>      | V      |

| DIGITAL INPUTS (Logic Levels) <sup>1</sup> |                                             | 2.7                      |             | 2 / (۷ DD                 | V      |

| V <sub>IL</sub>                            |                                             | -0.3                     |             | +0.3 × V <sub>DRIVE</sub> | V      |

|                                            |                                             |                          |             |                           | V      |

| V <sub>IH</sub>                            |                                             | 0.7 × V <sub>DRIVE</sub> |             | $V_{DRIVE} + 0.3$         |        |

| Input Leakage Current                      |                                             |                          | _           | ±1                        | μA/pin |

| Input Capacitance                          |                                             |                          | 5           | 4.004                     | pF     |

| Main Clock Rate                            |                                             |                          |             | 1.024                     | MHz    |

| Serial Clock Rate                          |                                             |                          |             | 1/t <sub>8</sub>          | Hz     |

| DIGITAL OUTPUTS <sup>1</sup>               |                                             |                          |             |                           |        |

| Data Format                                | Serial 24 bits, twos complement (MSB first) |                          |             |                           |        |

| $V_{OL}$                                   | I <sub>SINK</sub> = +500 μA                 |                          |             | 0.4                       | V      |

| V <sub>OH</sub>                            | I <sub>SOURCE</sub> = -500 μA               | V <sub>DRIVE</sub> – 0.3 |             |                           | V      |

| POWER REQUIREMENTS <sup>1</sup>            |                                             |                          |             |                           |        |

| $AV_DD$                                    | ± 5%                                        |                          | 2.5         |                           | V      |

| $DV_DD$                                    | ± 5%                                        |                          | 2.5         |                           | V      |

| $V_{DRIVE}$                                |                                             | 1.7                      | 2.5         | 3.6                       | V      |

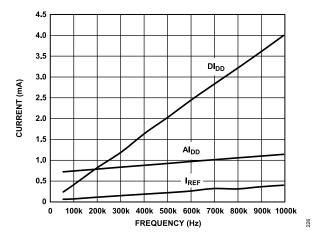

| CURRENT SPECIFICATIONS                     | MCLK = 1.024 MHz                            |                          |             |                           |        |

| AD7766 Operational Current                 | 128 kHz output data rate                    |                          |             |                           |        |

| Al <sub>DD</sub>                           |                                             |                          | 1.3         | 1.5                       | mA     |

| DI <sub>DD</sub>                           |                                             |                          | 3.9         | 4.8                       | mA     |

| I <sub>REF</sub>                           |                                             |                          | 0.35        | 0.425                     | mA     |

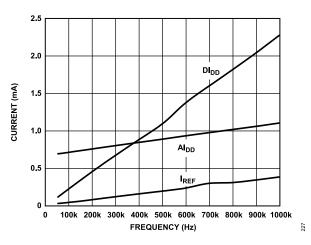

| AD7766-1 Operational Current               | 64 kHz output data rate                     |                          |             |                           |        |

| Al <sub>DD</sub>                           | 0.1.1.12 03.14.13.13.13.13                  |                          | 1.3         | 1.5                       | mA     |

| DI <sub>DD</sub>                           |                                             |                          | 2.2         | 2.85                      | mA     |

| I <sub>REF</sub>                           |                                             |                          | 0.35        | 0.425                     | mA     |

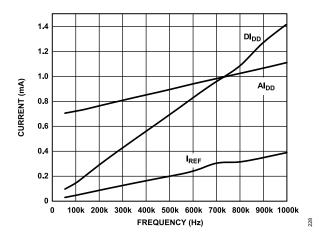

| AD7766-2 Operational Current               | 32 kHz output data rate                     |                          | 0.00        | 0.120                     | 110    |

| Al <sub>DD</sub>                           | 32 KHZ Output data rate                     |                          | 1.3         | 1.5                       | mA     |

|                                            |                                             |                          | 1.37        | 1.86                      | mA     |

| DI <sub>DD</sub>                           |                                             |                          |             |                           |        |

| I <sub>REF</sub>                           | For all desires                             |                          | 0.35        | 0.425                     | mA     |

| Static Current with MCLK Stopped           | For all devices                             |                          |             |                           |        |

| Al <sub>DD</sub>                           |                                             |                          | 0.9         | 1                         | mA     |

| $DI_DD$                                    |                                             |                          | 1           | 93                        | μA     |

| Power-Down Mode Current                    | For all devices                             |                          |             |                           |        |

| $AI_DD$                                    |                                             |                          | 0.1         | 6                         | μA     |

| DI <sub>DD</sub>                           |                                             |                          | 1           | 93                        | μA     |

| POWER DISSIPATION                          | MCLK = 1.024 MHz                            |                          |             |                           |        |

| AD7766 Operational Power                   | 128 kHz output data rate                    |                          | 15          | 18                        | mW     |

| AD7766-1 Operational Power                 | 64 kHz output data rate                     |                          | 10.5        | 13                        | mW     |

| AD7766-2 Operational Power                 | 32 kHz output data rate                     |                          | 8.5         | 10.5                      | mW     |

analog.com Rev. D | 5 of 23

# **SPECIFICATIONS**

# **TIMING SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 2.5 \text{ V} \pm 5\%$ ,  $V_{DRIVE} = 1.7 \text{ V}$  to 3.6 V,  $V_{REF+} = 5 \text{ V}$ , common-mode input =  $V_{REF+}/2$ ,  $T_A = -40^{\circ}\text{C}$  ( $T_{MIN}$ ) to  $+105^{\circ}\text{C}$  ( $T_{MAX}$ ), unless otherwise noted. Sample tested during initial release to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of  $DV_{DD}$ ) and timed from a voltage level of 1.7 V.

Table 3.

| Parameter                      | Limit at t <sub>MIN</sub> , t <sub>MAX</sub> | Unit              | Description                                                                                       |

|--------------------------------|----------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------|

| DRDY OPERATION                 |                                              |                   |                                                                                                   |

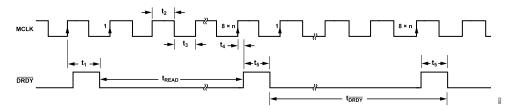

| t <sub>1</sub>                 | 510                                          | ns typ            | MCLK rising edge to DRDY falling edge                                                             |

| $t_2^1$                        | 100                                          | ns min            | MCLK high pulse width                                                                             |

| t <sub>3</sub> 1               | 900                                          | ns max            | MCLK low pulse width                                                                              |

| t <sub>4</sub>                 | 265                                          | ns typ            | MCLK rising edge to DRDY rising edge (AD7766)                                                     |

| ·                              | 128                                          | ns typ            | MCLK rising edge to $\overline{DRDY}$ rising edge (AD7766-1)                                      |

|                                | 71                                           | ns typ            | MCLK rising edge to DRDY rising edge (AD7766-2)                                                   |

| t <sub>5</sub>                 | 294                                          | ns typ            | DRDY pulse width (AD7766)                                                                         |

|                                | 435                                          | ns typ            | DRDY pulse width (AD7766-1)                                                                       |

|                                | 492                                          | ns typ            | DRDY pulse width (AD7766-2)                                                                       |

| t <sub>READ</sub> <sup>2</sup> | t <sub>DRDY</sub> - t <sub>5</sub>           | ns typ            | DRDY low period, read data during this period                                                     |

| $t_{\overline{DRDY}^2}$        | n × 8 × t <sub>MCLK</sub>                    | ns typ            | DRDY period                                                                                       |

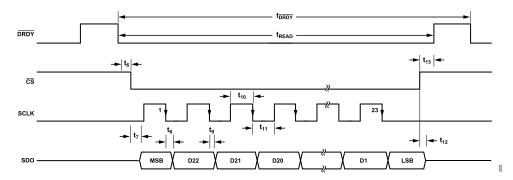

| READ OPERATION                 |                                              |                   |                                                                                                   |

| $t_6$                          | 0                                            | ns min            | DRDY falling edge to CS setup time                                                                |

| t <sub>7</sub>                 | 6                                            | ns max            | CS falling edge to SDO tristate disabled                                                          |

| t <sub>8</sub>                 | 60                                           | ns max            | Data access time after SCLK falling edge (V <sub>DRIVE</sub> = 1.7 V)                             |

|                                | 50                                           | ns max            | Data access time after SCLK falling edge (V <sub>DRIVE</sub> = 2.3 V)                             |

|                                | 25                                           | ns max            | Data access time after SCLK falling edge (V <sub>DRIVE</sub> = 2.7 V)                             |

|                                | 24                                           | ns max            | Data access time after SCLK falling edge (V <sub>DRIVE</sub> = 3.0 V)                             |

| t <sub>9</sub>                 | 10                                           | ns min            | SCLK falling edge to data valid hold time (V <sub>DRIVE</sub> = 3.6 V)                            |

| t <sub>10</sub>                | 10                                           | ns min            | SCLK high pulse width                                                                             |

| t <sub>11</sub>                | 10                                           | ns min            | SCLK low pulse width                                                                              |

| t <sub>SCLK</sub>              | 1/t <sub>8</sub>                             | sec min           | Minimum SCLK period                                                                               |

| t <sub>12</sub>                | 6                                            | ns max            | Bus relinquish time after $\overline{\text{CS}}$ rising edge                                      |

| t <sub>13</sub>                | 0                                            | ns min            | CS rising edge to DRDY rising edge                                                                |

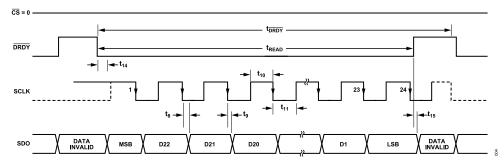

| READ OPERATION WITH CS LOW     |                                              |                   |                                                                                                   |

| t <sub>14</sub>                | 0                                            | ns min            | DRDY falling edge to data valid setup time                                                        |

| t <sub>15</sub>                | 0                                            | ns max            | DRDY rising edge to data valid hold time                                                          |

| DAISY-CHAIN OPERATION          |                                              |                   |                                                                                                   |

| t <sub>16</sub>                | 1                                            | ns min            | SDI valid to SCLK falling edge setup time                                                         |

| t <sub>17</sub>                | 2                                            | ns max            | SCLK falling edge to SDI valid hold time                                                          |

| SYNC/PD OPERATION              |                                              |                   |                                                                                                   |

| t <sub>18</sub>                | 1                                            | ns typ            | SYNC/PD falling edge to MCLK rising edge                                                          |

| t <sub>19</sub>                | 20                                           | ns typ            | MCLK rising edge to $\overline{DRDY}$ rising edge going into $\overline{SYNC}/\overline{PD}$ mode |

| t <sub>20</sub>                | 1                                            | ns min            | SYNC/PD rising edge to MCLK rising edge                                                           |

| t <sub>21</sub>                | 510                                          | ns typ            | MCLK rising edge to DRDY falling edge coming out of SYNC/PD mode                                  |

| t <sub>SETTLING</sub>          | 590                                          | t <sub>MCLK</sub> | Filter settling time after a reset or power-down (AD7766)                                         |

|                                | 1180                                         | t <sub>MCLK</sub> | Filter settling time after a reset or power-down (AD7766-1)                                       |

|                                | 2357                                         | t <sub>MCLK</sub> | Filter settling time after a reset or power-down (AD7766-2)                                       |

analog.com Rev. D | 6 of 23

<sup>&</sup>lt;sup>1</sup> Specifications are for all devices, AD7766, AD7766-1, and AD7766-2.

<sup>&</sup>lt;sup>2</sup> See the Terminology section.

## **SPECIFICATIONS**

t<sub>2</sub> and t<sub>3</sub> allow a ~90% to 10% duty cycle to be used for the MCLK input, where the minimum is 10% for the clock high time and 90% for MCLK low time. The maximum MCLK frequency is 1.024 MHz.

## **TIMING DIAGRAMS**

Figure 2.  $\overline{DRDY}$  vs. MCLK Timing Diagram, n = 1 for AD7766 (Decimate by 8), n = 2 for AD7766-1 (Decimate by 16), n = 4 for AD7766-2 (Decimate by 32)

Figure 3. Serial Timing Diagram, Reading Data Using CS

Figure 4. Serial Timing Diagram, Reading Data Setting CS Logic Low

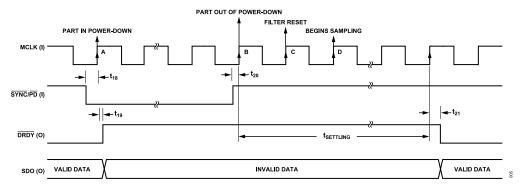

Figure 5. Reset, Synchronization, and Power-Down Timing (For More Information, See the Power-Down, Reset, and Synchronization Section)

analog.com Rev. D | 7 of 23

$<sup>^{2}</sup>$  n = 1 for AD7766, n = 2 for the AD7766-1, n = 4 for the AD7766-2.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 4

| Parameter                                             | Rating                               |  |  |

|-------------------------------------------------------|--------------------------------------|--|--|

| AV <sub>DD</sub> to AGND                              | -0.3 V to +3 V                       |  |  |

| DV <sub>DD</sub> to DGND                              | -0.3 V to +3 V                       |  |  |

| $AV_{DD}$ to $DV_{DD}$                                | -0.3 V to +0.3 V                     |  |  |

| V <sub>REF+</sub> to REFGND                           | -0.3 V to +7 V                       |  |  |

| REFGND to AGND                                        | -0.3 V to +0.3 V                     |  |  |

| V <sub>DRIVE</sub> to DGND                            | -0.3 V to +6 V                       |  |  |

| V <sub>IN+</sub> , V <sub>IN</sub> to AGND            | -0.3 V to V <sub>REF+</sub> + 0.3 V  |  |  |

| Digital Inputs to DGND                                | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |  |  |

| Digital Outputs to DGND                               | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |  |  |

| AGND to DGND                                          | -0.3 V to +0.3 V                     |  |  |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                               |  |  |

| Operating Temperature Range                           | -40°C to +105°C                      |  |  |

| Storage Temperature Range                             | -65°C to +150°C                      |  |  |

| Junction Temperature                                  | 150°C                                |  |  |

| TSSOP Package                                         |                                      |  |  |

| θ <sub>JA</sub> Thermal Impedance                     | 150.4°C/W                            |  |  |

| θ <sub>JC</sub> Thermal Impedance                     | 27.6°C/W                             |  |  |

| Lead Temperature, Soldering                           |                                      |  |  |

| Vapor Phase (60 sec)                                  | 215°C                                |  |  |

| Infrared (15 sec)                                     | 220°C                                |  |  |

| ESD                                                   | 1 kV                                 |  |  |

<sup>&</sup>lt;sup>1</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. D | 8 of 23

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6. 16-Lead TSSOP Pin Configuration

Table 5. Pin Function Descriptions

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AV <sub>DD</sub>   | +2.5 V Analog Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2       | V <sub>REF+</sub>  | Reference Input for the AD7766/AD7766-1/AD7766-2. An external reference must be applied to this input pin. The V <sub>REF+</sub> input can range from 2.4 V to 5 V. The reference voltage input is independent of the voltage magnitude applied to the AV <sub>DD</sub> pin.                                                                                                                                                                                                                                                                                                                                                       |

| 3       | REFGND             | Reference Ground. Ground connection for the reference voltage. The input reference voltage (V <sub>REF+</sub> ) should be decoupled to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1       | V <sub>IN+</sub>   | Positive Input of the Differential Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5       | V <sub>IN</sub> -  | Negative Input of the Differential Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6       | AGND               | Power Supply Ground for Analog Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7       | SYNC/PD            | Synchronization and Power-Down Input Pin. This pin has dual functionality. It can be used to synchronize multiple AD7766/AD7766-1/AD7766-2 devices and/or to put the AD7766/AD7766-1/AD7766-2 devices into power-down mode. See the Power-Down, Reset, and Synchronization section for further details.                                                                                                                                                                                                                                                                                                                            |

| 8       | DV <sub>DD</sub>   | 2.5 V Digital Power Supply Input. In cases where a logic voltage of 2.5 V for interfacing is used, (2.5 V applied to V <sub>DRIVE</sub> pin), the DV <sub>DD</sub> and V <sub>DRIVE</sub> pins may be connected to the same voltage supply rail.                                                                                                                                                                                                                                                                                                                                                                                   |

| 9       | V <sub>DRIVE</sub> | Logic Power Supply Input, 1.8 V to 3.6 V. The voltage supplied at this pin determines the operating voltage of the digital logic interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10      | SDO                | Serial Data Output. The conversion result from the AD7766/AD7766-1/AD7766-2 is output on the SDO pin as a 24-bit, twos complement, MSE first, serial data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11      | DGND               | Digital Logic Power Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12      | DRDY               | Data Ready Output. A falling edge on the DRDY signal indicates that a new conversion data result is available in the output register of the AD7766/AD7766-1/AD7766-2. See the AD7766/AD7766-1/AD77662-2 Interface section for further details.                                                                                                                                                                                                                                                                                                                                                                                     |

| 13      | SCLK               | Serial Clock Input. The SCLK input provides the serial clock for all serial data transfers with the AD7766/AD7766-1/AD7766-2 devices. See the AD7766/AD7766-1/AD77662-2 Interface section for further details.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14      | MCLK               | Main Clock Input. The sampling frequency of the AD7766/AD7766-1/AD7766-2 is equal to the MCLK frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15      | SDI                | Serial Data Input. This is the daisy-chain input of the AD7766/AD7766-1/AD7766-2. See the Daisy Chaining section for further details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16      | CS                 | Chip Select Input. The $\overline{CS}$ input selects a specific AD7766/AD7766-1/AD7766-2 device and acts as an enable on the SDO pin. In cases where $\overline{CS}$ is used, the MSB of the conversion result is clocked onto the SDO line on the $\overline{CS}$ falling edge. The $\overline{CS}$ input allows multiple AD7766/AD7766-1/AD7766-2 devices to share the same SDO line. This allows the user to select the appropriate device by supplying it with a logic low $\overline{CS}$ signal, which enables the SDO pin of the device concerned. See the AD7766/AD7766-1/AD77662-2 Interface section for further details. |

analog.com Rev. D | 9 of 23

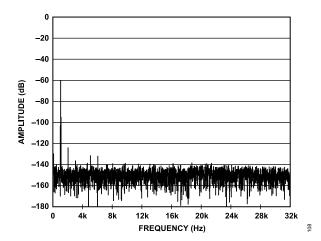

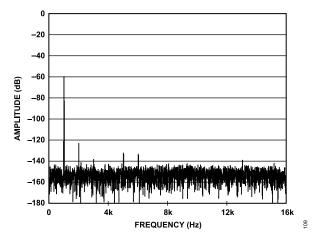

## TYPICAL PERFORMANCE CHARACTERISTICS

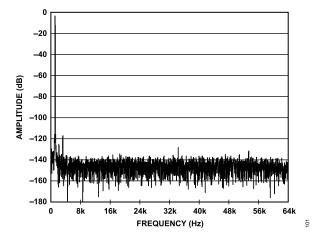

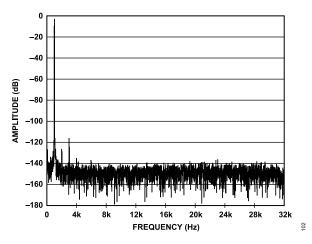

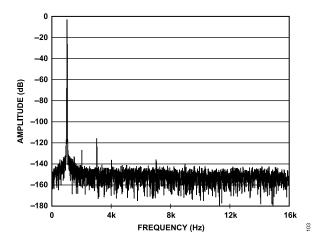

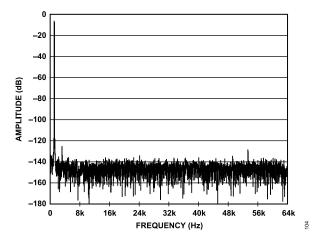

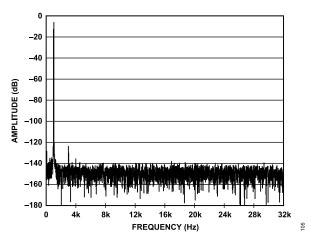

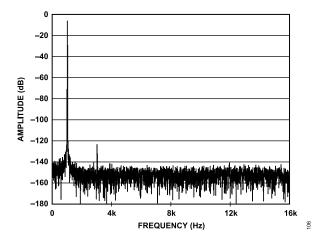

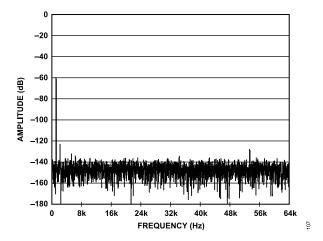

$AV_{DD}$  =  $DV_{DD}$  = 2.5 V ± 5%,  $V_{DRIVE}$  = 1.8 V to 3.6 V,  $V_{REF+}$  = 5 V, MCLK = 1.024 MHz, common-mode input =  $V_{REF+}/2$ .  $T_A$  = 25°C, unless otherwise noted. All FFTs were generated using 8192 samples using a four-term Blackman-Harris window.

Figure 7. AD7766 FFT, 1 kHz, -0.5 dB Input Tone

Figure 8. AD7766-1 FFT, 1 kHz, -0.5 dB Input Tone

Figure 9. AD7766-2 FFT, 1 kHz, -0.5 dB Input Tone

Figure 10. AD7766 FFT, 1 kHz, -6 dB Input Tone

Figure 11. AD7766-1 FFT, 1 kHz, -6 dB Input Tone

Figure 12. AD7766-2 FFT, 1 kHz, -6 dB Input Tone

analog.com Rev. D | 10 of 23

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 13. AD7766 FFT, 1 kHz, -60 dB Input Tone

Figure 14. AD7766-1 FFT, 1 kHz, −60 dB Input Tone

Figure 15. AD7766-2 FFT, 1 kHz, -60 dB Input Tone

Figure 16. AD7766 IMD FFT, 50 kHz Center Frequency

Figure 17. AD7766-1 IMD FFT, 25 kHz Center Frequency

Figure 18. AD7766-2 IMD FFT, 12 kHz Center Frequency

analog.com Rev. D | 11 of 23

## TYPICAL PERFORMANCE CHARACTERISTICS

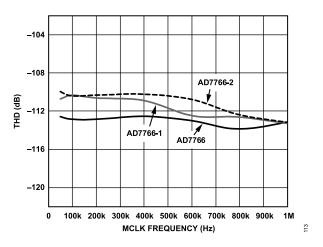

Figure 19. AD7766/AD7766-1/AD7766-2 THD vs. MCLK Frequency

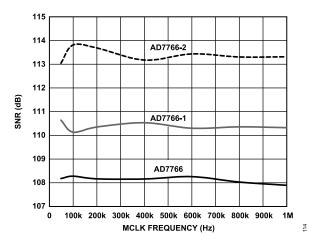

Figure 20. AD7766/AD7766-1/AD7766-2 SNR vs. MCLK Frequency

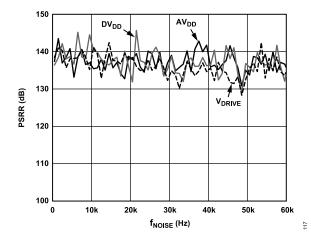

Figure 21. AD7766 Power Supply Sensitivity vs. Supply Ripple Frequency  $(f_{NOISE})$  with Decoupling Capacitors

Figure 22. AD7766 CMRR vs. Common-Mode Ripple Frequency (f<sub>NOISE</sub>)

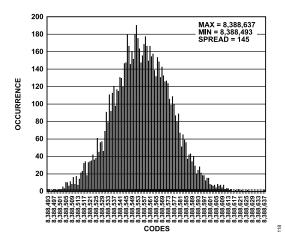

Figure 23. AD7766 24-Bit Histogram

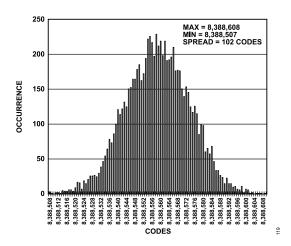

Figure 24. AD7766-1 24-Bit Histogram

analog.com Rev. D | 12 of 23

# TYPICAL PERFORMANCE CHARACTERISTICS

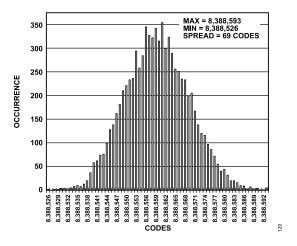

Figure 25. AD7766-2 24-Bit Histogram

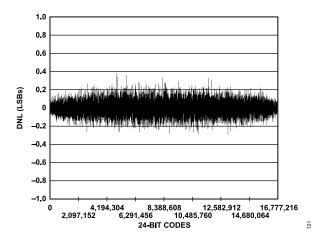

Figure 26. AD7766/AD7766-1/AD7766-2 24-Bit DNL

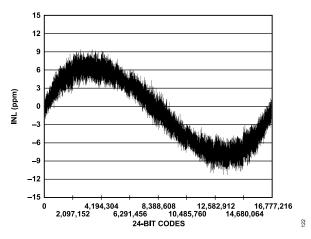

Figure 27. AD7766/AD7766-1/AD7766-2 24-Bit INL

analog.com Rev. D | 13 of 23

## **TERMINOLOGY**

# Signal-to-Noise Ratio (SNR)

SNR is the ratio of the actual input signal's rms value to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

# **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of harmonics to the fundamental. For the AD7766, it is defined as

$$THD (dB) = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_I}$$

(1)

where:

$V_1$  is the rms amplitude of the fundamental.

$V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second to the sixth harmonics.

# Nonharmonic Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio of the rms signal amplitude to the rms value of the peak spurious spectral component, excluding harmonics.

## **Dynamic Range**

Dynamic range is the ratio of the rms value of the full scale to the rms noise measured with the inputs shorted together. The value for the dynamic range is expressed in decibels.

## Intermodulation Distortion (IMD)

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities creates distortion products at sum and difference frequencies of mfa  $\pm$  nfb, where m, n = 0, 1, 2, 3, and so on. Intermodulation distortion terms are those for which neither m nor n is equal to 0. For example, the second-order terms include (fa + fb) and (fa - fb), and the third-order terms include (2fa + fb), (2fa - fb), (fa + 2fb), and (fa - 2fb).

The AD7766 is tested using the CCIF standard, where two input frequencies near the top end of the input bandwidth are used.

In this case, the second-order terms are usually distanced in frequency from the original sine waves, and the third-order terms are usually at a frequency close to the input frequencies. As a result, the second- and third-order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification, where it is the ratio of the rms sum of the individual

distortion products to the rms amplitude of the sum of the fundamentals expressed in decibels.

# Integral Nonlinearity (INL)

INL is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function.

## **Differential Nonlinearity (DNL)**

DNL is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### Zero Error

Zero error is the difference between the ideal midscale input voltage (when both inputs are shorted together) and the actual voltage producing the midscale output code.

## **Zero Error Drift**

Zero error drift is the change in the actual zero error value due to a temperature change of 1°C. It is expressed as a percentage of full scale at room temperature.

## **Gain Error**

The first transition (from  $100 \dots 000$  to  $100 \dots 001$ ) should occur ½ LSB above the nominal negative full scale for an analog voltage. The last transition (from  $011 \dots 110$  to  $011 \dots 111$ ) should occur  $1\frac{1}{2}$  LSB below the nominal full scale for an analog voltage. The gain error is the deviation of the difference between the actual level of the last transition and the actual level of the first transition, from the difference between the ideal levels.

## **Gain Error Drift**

Gain error drift is the change in the actual gain error value due to a temperature change of 1°C. It is expressed as a percentage of full scale at room temperature.

# Common-Mode Rejection Ratio (CMRR)

CMRR is defined as the ratio of the power in the ADC output at full-scale frequency f to the power of a 100 mV sine wave applied to the common-mode voltage of the  $V_{\text{IN+}}$  and  $V_{\text{IN-}}$  inputs at frequency f<sub>S</sub>.

$$CMRR (dB) = 10 \log(Pf/Pf_S)$$

(2)

where Pf is the power at the frequency f in the ADC output, and  $Pf_S$  is the power at the frequency  $f_S$  in the ADC output.

#### THEORY OF OPERATION

The AD7766/AD7766-1/AD7766-2 operate using a fully differential analog input applied to a successive approximation (SAR) core. The output of the oversampled SAR is filtered using a linear-phase digital FIR filter. The fully filtered data is output in a serial format, with the MSB being clocked out first.

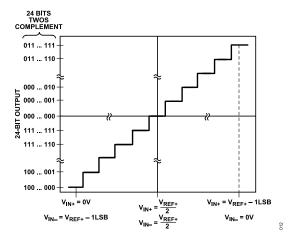

# AD7766/AD7766-1/AD7766-2 TRANSFER FUNCTION

The conversion results of the AD7766/AD7766-1/AD7766-2 are output in a twos complement, 24-bit serial format. The fully differential inputs  $V_{\text{IN+}}$  and  $V_{\text{IN-}}$  are scaled by the AD7766/AD7766-1/ AD7766-2 relative to the reference voltage input ( $V_{\text{REF+}}$ ) as shown in Figure 28.

Figure 28. AD7766/AD7766-1/AD7766-2 Transfer Function

# **CONVERTER OPERATION**

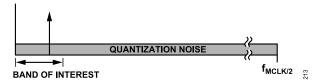

Internally, the input waveform applied to the SAR core is converted and an equivalent digital word is output to the digital filter at a rate equal to MCLK. By employing oversampling, the quantization noise of the converter is spread across a wide bandwidth from 0 to  $f_{MCLK}$ . This means that the noise energy contained in the signal band of interest is reduced (see Figure 29).

Figure 29. Quantization Noise

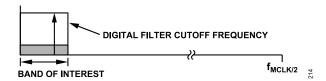

Figure 30. Digital Filter Cutoff Frequency

The digital filtering that follows the converter output acts to remove the out-of-band quantization noise (see Figure 30). This also has the effect of reducing the data rate from  $f_{MCLK}$  at the input of the filter to  $f_{MCLK}/8$ ,  $f_{MCLK}/16$ , or  $f_{MCLK}/32$  at the digital output, depending on which model of the device is being used.

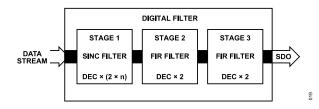

The digital filter consists of three separate filter blocks. Figure 31 shows the three constituent blocks of the filter. The order of decimation of the first filter block is set as 2, 4, or 8. The remaining sections each operate with a decimation of 2.

Figure 31. FIR Filter Stages (n = 1 for AD7766, n = 2 for AD7766-1, n = 4 for AD7766-2)

Table 6 shows the three available models of the AD7766, listing the change in output data rate relative to the order of decimation rate implemented. This brings into focus the trade-off that exists between extra filtering and reduction in bandwidth, whereby using a filter option with a larger decimation rate increases the noise performance while decreasing the usable input bandwidth.

Table 6. AD7766 Models

| Model    | Decimation Rate | Output Data Rate (ODR) |

|----------|-----------------|------------------------|

| AD7766   | 8               | 128 kHz                |

| AD7766-1 | 16              | 64 kHz                 |

| AD7766-2 | 32              | 32 kHz                 |

Note that the output data rates shown in Table 6 are realized when using the maximum MCLK input frequency of 1.024 MHz. The output data rate scales linearly with the MCLK frequency, as does the digital power dissipated in the device.

The settling time of the filter implemented on the AD7766, AD7766-1, and AD7766-2 is related to the length of the filter employed. The response of the filter in the time domain sets the filter settling time. Table 7 shows the filter settling times of the AD7766/AD7766-1/AD7766-2.

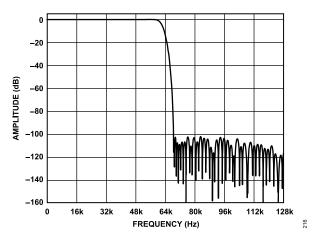

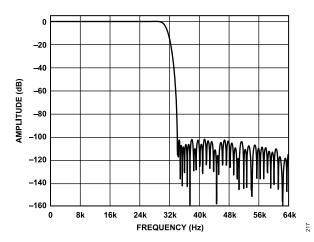

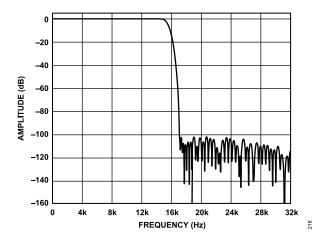

The frequency responses of the digital filters on the AD7766, AD7766-1, and AD7766-2 are shown in Figure 32, Figure 33, and Figure 34, respectively. At the Nyquist frequency (output data rate/2), the digital filter provides 6 dB of attenuation. In each case, the filter provides stop-band attenuation of 100 dB and pass-band ripple of ±0.005 dB.

analog.com Rev. D | 15 of 23

#### THEORY OF OPERATION

Figure 32. AD7766 Digital Filter Frequency Response

Figure 33. AD7766-1 Digital Filter Frequency Response

Figure 34. AD7766-2 Digital Filter Frequency Response

#### **ANALOG INPUT STRUCTURE**

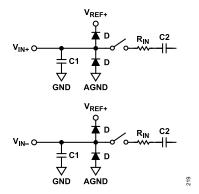

The AD7766/AD7766-1/AD7766-2 are configured as a differential input structure. A true differential signal is sampled between the analog inputs  $V_{\text{IN+}}$  and  $V_{\text{IN-}}$ , Pin 4 and Pin 5, respectively. Using differential inputs provides rejection of signals that are common to both the  $V_{\text{IN+}}$  and  $V_{\text{IN-}}$  pins.

Figure 35 shows the equivalent analog input circuit of the AD7766/AD7766-1/AD7766-2. The two diodes on each of the differential inputs provide ESD protection for the analog inputs.

Figure 35. Equivalent Analog Input Structure

Take care to ensure that the analog input signal does not exceed the reference supply voltage (V<sub>REF+</sub>) by more than 0.3 V, as specified in the Absolute Maximum Ratings section. If the input voltage exceeds this limit, the diodes become forward biased and start to conduct current. The diodes can handle 130 mA maximum.

The impedance of the analog inputs can be modeled as a parallel combination of C1 and the network formed by the series connection of  $R_{IN},$  C1, and C2. The value of C1 is dominated by the pin capacitance.  $R_{IN}$  is typically 1.4  $k\Omega,$  the lumped component of serial resistors and the  $R_{ON}$  of the switches. C2 is typically 22 pF, and its value is dominated by the sampling capacitor.

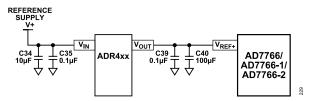

## SUPPLY AND REFERENCE VOLTAGES

The AD7766/AD7766-1/AD7766-2 operate from a 2.5 V supply applied to the DV<sub>DD</sub> and AV<sub>DD</sub> pins. The interface is specified to operate between 1.7 V and 3.6 V. The AD7766/AD7766-1/ AD7766-2 operate from a reference input in the range of 2.2 V to 2 × AV<sub>DD</sub> applied to the V<sub>REF+</sub> pin. The nominal reference supply voltage is 5 V, but a 2.5 V supply can also be used. When using a 5 V reference, the recommended reference devices are the ADR445, ADR435, or ADR425; when using 2.5 V, the ADR441, ADR431, or ADR421 are recommended. The voltage applied to the reference input (V<sub>REF+</sub>) operates both as a reference supply and as a power supply to the AD7766/AD7766-1/AD7766-2 devices. Therefore, when using a 5 V reference input, the full-scale differential input range of the AD7766/AD7766-1/AD7766-2 section for details on the maximum input voltage.

analog.com Rev. D | 16 of 23

## AD7766/AD7766-1/AD77662-2 INTERFACE

The AD7766/AD7766-1/AD7766-2 provide the user with a flexible serial interface, enabling the user to implement the most desirable interfacing scheme for their application. Each AD7766/AD7766-1/ AD7766-2 interface comprises seven different signals. Five of these signals are inputs: MCLK, CS, SYNC/PD, SCLK, and SDI. The other two signals are outputs: DRDY and SDO.

## **INITIAL POWER-UP**

On initial power-up, apply a continuous MCLK signal. It is recommended that the user reset the AD7766/AD7766-1/AD7766-2 to clear the filters and ensure correct operation. The reset is completed as shown in Figure 5, with all events occurring relative to the rising edge of MCLK. A negative pulse on the SYNC/PD input initiates the reset, and the DRDY output switches to logic high and remains high until valid data is available. Following the power-up of the AD7766/AD7766-1/AD7766-2 by transitioning the SYNC/PD pin to logic high, a settling time is required before valid data is output by the device. This settling time, tSETTLING, is a function of the MCLK frequency and the decimation rate. Table 7 lists the settling time of each AD7766 model and should be referenced when reviewing Figure 5.

Table 7. Filter Settling Time After SYNC/PD

| Model    | Decimation Rate | t <sub>SETTLING</sub> 11                      |

|----------|-----------------|-----------------------------------------------|

| AD7766   | 8               | (590 × t <sub>MCLK</sub> ) + t <sub>21</sub>  |

| AD7766-1 | 16              | (1180 × t <sub>MCLK</sub> ) + t <sub>21</sub> |

| AD7766-2 | 32              | (2357 × t <sub>MCLK</sub> ) + t <sub>21</sub> |

<sup>1</sup> t<sub>SETTLING</sub> is measured from the first MCLK rising edge after the rising edge of SYNC/PD to the falling edge of DRDY.

## **READING DATA**

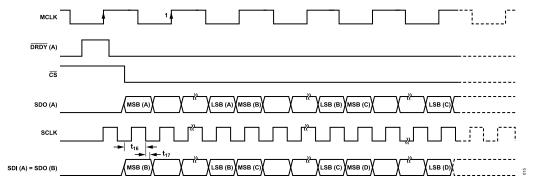

The AD7766/AD7766-1/AD7766-2 output data conversion results in an MSB-first, twos complement, 24-bit format on the serial data output (SDO) pin. MCLK is the main clock, which controls all the AD7766/AD7766-1/AD7766-2 conversions. The SCLK is the serial clock input for the device. All data transfers take place with respect to the SCLK signal.

The DRDY line is used as a status signal to indicate when the data is available to be read from the AD7766/AD7766-1/AD7766-2. The falling edge of DRDY indicates that a new data-word is available in the output register of the device. DRDY stays low during the period that output data is permitted to be read from the SDO pin. The DRDY signal returns to logic high to indicate when not to read from the device. Ensure that a data read is not attempted during this period while the output register is being updated.

The AD7766/AD7766-1/AD7766-2 offer the option of using a chip select input signal  $(\overline{CS})$  in a data read cycle. The  $\overline{CS}$  signal

is a gate for the SDO pin and allows many AD7766/AD7766-1/ AD7766-2 devices to share the same serial bus. It acts as an instruction signal to each of these devices indicating permission to use the bus. When  $\overline{\text{CS}}$  is logic high, the SDO line of the AD7766/ AD7766-1/AD7766-2 is tristated.

There are two distinct patterns that can be initiated to read data from the AD7766/AD7766-1/AD7766-2 devices: a pattern for when the  $\overline{CS}$  falling edge occurs after the  $\overline{DRDY}$  falling edge and a pattern for when the  $\overline{CS}$  falling edge occurs before the  $\overline{DRDY}$  falling edge (when  $\overline{CS}$  is set to logic low).

When the  $\overline{\text{CS}}$  falling edge occurs after the  $\overline{\text{DRDY}}$  falling edge, the MSB of the conversion result is available on the SDO line on the  $\overline{\text{CS}}$  falling edge. The remaining bits of the conversion result (MSB – 1, MSB – 2, and so on) are clocked onto the SDO line by the falling edges of SCLK that follow the  $\overline{\text{CS}}$  falling edge. Figure 3 details this interfacing scheme.

When  $\overline{\text{CS}}$  is tied low, the AD7766/AD7766-1/AD7766-2 serial interfaces can operate in 3-wire mode as shown in Figure 4. In this case, the MSB of the conversion result is available on the SDO line on the falling edge of  $\overline{\text{DRDY}}$ . The remaining bits of the data conversion result (MSB – 1, MSB – 2, and so on) are clocked onto the SDO line by the subsequent SCLK falling edges.

# POWER-DOWN, RESET, AND SYNCHRONIZATION

The SYNC/PD pin allows the user to synchronize multiple AD7766/AD7766-1/AD7766-2 devices. This pin also allows the user to reset and power down the AD7766/AD7766-1/AD7766-2 devices. These features are implemented relative to the rising edges of MCLK and are shown in Figure 5, marked as A, B, C, and D.

To power down, reset, or synchronize a device, the \$\overline{SYNC/PD}\$ pin should be taken low. On the first rising edge of MCLK, the AD7766/AD7766-1/AD7766-2 are powered down. The \$\overline{DRDY}\$ pin transitions to logic high, indicating that the data in the output register is no longer valid. The status of the \$\overline{SYNC/PD}\$ pin is checked on each subsequent rising edge of MCLK. On the first rising edge of MCLK after the \$\overline{SYNC/PD}\$ pin is taken high, the AD7766/AD7766-1/AD7766-2 are taken out of power-down. On the next rising edge, the filter of the AD7766/AD7766-1/AD7766-2 is reset. On the following rising edge, the first new sample is taken.

A settling time,  $t_{SETTLING}$ , from the filter reset must elapse before valid data is output by the device (see Table 7). The DRDY output goes logic low after  $t_{SETTLING}$  to indicate when valid data is available on SDO for readback.

analog.com Rev. D | 17 of 23

## **DAISY CHAINING**

Daisy chaining devices allows numerous devices to use the same digital interface lines by cascading the outputs of multiple ADCs on a single data line. This feature is especially useful for reducing component count and wiring connections, for example, in isolated multiconverter applications or for systems with a limited interfacing capacity. Data readback is analogous to clocking a shift register where data is clocked on the falling edge of SCLK.

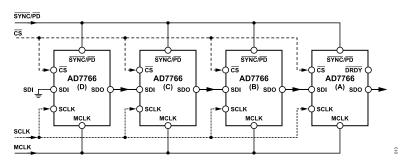

The block diagram in Figure 36 shows how devices must be connected to achieve daisy-chain functionality. The scheme shown operates by passing the output data of the SDO pin of an AD7766 device to the SDI input of the next AD7766 device in the chain. The data then continues through the chain until it is clocked onto the SDO pin of the first device in the chain.

## **READING DATA IN DAISY-CHAIN MODE**

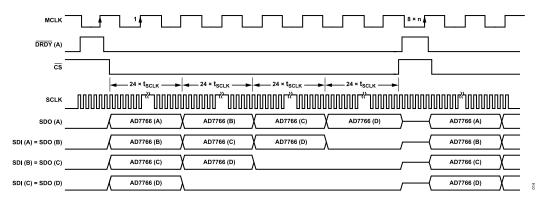

An example of a daisy chain of four AD7766 devices is shown in Figure 36 and Figure 37. In the case illustrated in Figure 36, the output of the AD7766 labeled A is the output of the full daisy chain. The last device in the chain (the AD7766 labeled D) has its serial data input (SDI) pin connected to ground. All the devices in the chain must use common MCLK, SCLK,  $\overline{CS}$ , and  $\overline{SYNC/PD}$  signals.

To enable the daisy-chain conversion process, apply a common SYNC/PD pulse to all devices, synchronizing all the devices in the chain (see the Power-Down, Reset, and Synchronization section).

After applying a \$\overline{SYNC/PD}\$ pulse to all the devices, there is a delay (as listed in Table 7) before valid conversion data appears at the output of the chain of devices. As shown in Figure 37, the first conversion result is output from the AD7766 device labeled A. This 24-bit conversion result is followed by the conversion results from the devices labeled B, C, and D, with all conversion results output in an MSB-first sequence. The stream of conversion results is clocked through each device in the chain and is eventually clocked onto the SDO pin of the AD7766 device labeled A. The conversion results of all the devices in the chain must be clocked onto the SDO pin of the final device in the chain while its \$\overline{DRDY}\$ signal is active low. This is illustrated in the examples shown (Figure 37 and Figure 38), where the conversion results from the devices labeled A, B, C, and D are clocked onto SDO (A) during the time between the falling edge of \$\overline{DRDY}\$ (A).

#### CHOOSING THE SCLK FREQUENCY

As shown in Figure 37, the number of SCLK falling edges that occurs during the period when  $\overline{DRDY}$  (A) is active low must match the number of devices in the chain multiplied by 24 (the number of bits that must be clocked through onto SDO (A) for each device).

The period of SCLK ( $t_{SCLK}$ ) required for a known daisy-chain length using a known common MCLK frequency must, therefore, be established in advance. Note that the maximum SCLK frequency is governed by  $t_8$  and is specified in Table 3 for different  $V_{DRIVE}$  voltages.

In the case where  $\overline{\text{CS}}$  is tied logic low,

$$t_{SCLK} \le \left\lceil \frac{t_{READ}}{24 \times K} \right\rceil \tag{3}$$

where:

K is the number of AD7766/AD7766-1/AD7766-2 devices in the chain

$t_{SCLK}$  is the period of the SCLK.

$t_{READ}$  equals  $t_{DRDY}$  -  $t_5$ .

In the case where  $\overline{\text{CS}}$  is used in the daisy-chain interface,

$$t_{SCLK} \le \left[ \frac{\left( t_{READ} \right) - \left( t_6 + t_7 + t_{13} \right)}{24 \times K} \right] \tag{4}$$

where:

K is the number of AD7766/AD7766-1/AD7766-2 devices in the

$t_{SCLK}$  is the period of the SCLK.

$t_{READ}$  equals  $t_{DRDY} - t_5$ .

Note that the maximum value of SCLK is governed by  $t_8$  and is specified in Table 3 for different  $V_{DRIVE}$  voltages.

analog.com Rev. D | 18 of 23

## **DAISY CHAINING**

# DAISY-CHAIN MODE CONFIGURATION AND TIMING DIAGRAMS

Figure 36. Daisy-Chain Configuration with Four AD7766 Devices

Figure 37. Daisy-Chain Timing Diagram (n = 1 for AD7766, n = 2 for AD7766-1, n = 4 for AD7766-2) When Driving the AD7766

Figure 38. Daisy-Chain SDI Setup and Hold Timing

analog.com Rev. D | 19 of 23

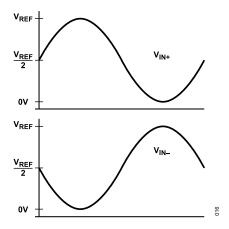

## **DRIVING THE AD7766/AD7766-1/AD7766-2**

The AD7766/AD7766-1/AD7766-2 must be driven with fully differential inputs. The common-mode voltage of the differential inputs to the AD7766/AD7766-1/AD7766-2 devices, and therefore the limits on the differential inputs, is set by the reference voltage ( $V_{REF+}$ ) applied to the device. The common-mode voltage of the AD7766/AD7766-1/AD7766-2 is  $V_{REF+}$ /2. When the AD7766/AD7766-1/AD7766-2  $V_{REF+}$  pin has a 5 V supply (using ADR445, ADR435, or ADR425), the common mode is at 2.5 V, meaning that the maximum inputs that can be applied on the AD7766/AD7766-1/AD7766-2 differential inputs are a 5 V p-p input around 2.5 V.

Figure 39. Maximum Differential Inputs to the AD7766

An analog voltage of 2.5 V supplies the AD7766/AD7766-1/ AD7766-2 AV $_{\rm DD}$  pin. However, the AD7766/AD7766-1/AD7766-2 allow the user to apply a reference voltage of up to 5 V. This provides the user with an increased full-scale range, offering the user the option of using the AD7766/AD7766-1/AD7766-2 with a greater LSB voltage. Figure 39 shows the maximum inputs to the AD7766.

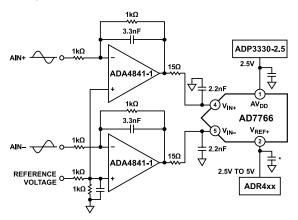

## **DIFFERENTIAL SIGNAL SOURCE**

An example of recommended driving circuitry that can be used in conjunction with the AD7766 is shown in Figure 40. Figure 40 shows how the ADA4841-1 device can be used to drive an input to the AD7766 from a differential source. Each of the differential paths is driven by an ADA4841-1 device.

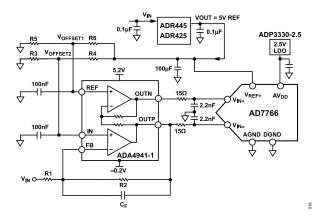

## SINGLE-ENDED SIGNAL SOURCE

For applications using a single-ended analog signal, either bipolar or unipolar, the ADA4941-1 single-ended-to-differential driver creates a fully differential input to the AD7766. The schematic is shown in Figure 41.

R1 and R2 set the attenuation ratio between the input range and the ADC range ( $V_{REF+}$ ). R1, R2, and  $C_F$  are chosen depending on the desired input resistance, signal bandwidth, antialiasing, and noise contribution. The ratio of R2 to R1 should be equal to the ratio of REF to the peak-to-peak input voltage. For example, for the  $\pm 10$  V range with a 4 k $\Omega$  impedance, R2 = 1 k $\Omega$  and R1 = 4 k $\Omega$ .

R3 and R4 set the common mode on the  $V_{IN-}$  input, and R5 and R6 set the common mode on the  $V_{IN+}$  input of the ADC. The common mode, which is equal to the voltage present at  $V_{OFFSET1}$ , should be close to  $V_{REF+}/2$ . The voltage present should roughly be set to the ratio of  $V_{OFFSET1}$  to 1 + R2/R1.

\*SEE  $V_{REF+}$  INPUT SIGNAL SECTION FOR DETAILS.

Figure 40. Driving the AD7766 from a Fully Differential Source

710

Figure 41. Driving the AD7766 from a Single-Ended Source

Table 8. Resistor Values Required When Using the Differential-to-Single-Ended Circuit with ADA4941 (See Figure 41)

| V <sub>IN</sub> (V) | V <sub>OFFSET1</sub> (V) | V <sub>OFFSET2</sub> (V) | OUT+ (V)     | OUT- (V)   | R1 (kΩ) | R2 (kΩ) | R4 (kΩ) | $R3 = R5 = R6 (k\Omega)$ |

|---------------------|--------------------------|--------------------------|--------------|------------|---------|---------|---------|--------------------------|

| +20, -20            | 2.5                      | 2.203                    | -0.01, +4.96 | 5.01, 0.04 | 8.06    | 1       | 12.7    | 10                       |

| +10, -10            | 2.5                      | 2.000                    | 0.01, 4.99   | 4.99, 0.01 | 4.02    | 1       | 15      | 10                       |

| +5, -5              | 2.5                      | 1.667                    | 0.00, 5.00   | 5.00, 0.00 | 2       | 1       | 20      | 10                       |

analog.com Rev. D | 20 of 23

## **DRIVING THE AD7766/AD7766-1/AD7766-2**

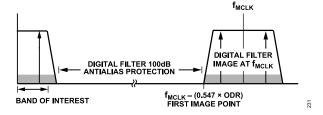

## **ANTIALIASING**

The AD7766/AD7766-1/AD7766-2 sample the analog input at a maximum rate of 1.024 MHz. The on-board digital filter provides up to 100 dB attenuation for any possible aliasing frequency in the range from the beginning of the filter stop band (0.547 × ODR) to where the image of the digital filter pass band occurs. This occurs at  $f_{MCLK}$  minus the filter stop band ( $f_{MCLK}$  – 0.547 × ODR), as shown in Figure 42.

Figure 42. AD7766/AD7766-1/AD7766 Spectrum

Table 9 shows the attenuation achieved by various orders of front-end antialias filters prior to the signal entering the AD7766/AD7766-1/AD7766-2 at the image of the digital filter stop band, which is 1.024 MHz – 0.547 × ODR.

Table 9. Antialias Filter Order

| Model    | Filter Order | Attenuation at 1.024 MHz – 0.547 × ODR |

|----------|--------------|----------------------------------------|

| AD7766   | First        | 27 dB                                  |

|          | Second       | 50 dB                                  |

|          | Third        | 70 dB                                  |

| AD7766-1 | First        | 33 dB                                  |

|          | Second       | 62 dB                                  |

|          | Third        | 89 dB                                  |

| AD7766-2 | First        | 38 dB                                  |

|          | Second       | 74 dB                                  |

|          | Third        | 110 dB                                 |

The AD7764 and AD7765  $\Sigma$ - $\Delta$  devices are available to customers that require extra antialias protection. These devices sample the signal internally at a rate of 20 MHz to achieve up to a maximum of 156 kHz or 312 kHz output data rate. This means that the first alias point of these devices when run at the maximum speeds is 19.921 MHz and 19.843 MHz, respectively.

# **POWER DISSIPATION**