### The EMS Company of the Year, pg. 32

### PRINTED CIRCUIT pcdandf.com December 2020 DESIGN & FAB CIRCUITSASSEMBIJY.com DECEMBER 2020

-----

## Are LTS Solders All Wet?

4th Gen SnBi Alloys Are Put to the Test

PCEA: Filling a Void

**Microsectioning** for High-Volume Production

Apertures for 01005s

# Because Your Home Is Now Your Office, Partner With A Company You Can Trust

APCT Provides DFM Expertise & Quick-Turn Capability for NPI; Complete Offshore Management for Production

### **DOMESTIC SOLUTIONS**

- Standard to Advanced HDI Technology

- Flex & Rigid Flex Technology

- Complete DFM Support

- Cycle Times Faster Than Industry Standards

- Defense & Aerospace Certifications

### **OFFSHORE SOLUTIONS**

- One Point of Contact

- Seamless Recipe Transfer

- VMI & Kanban Programs

- U.S. Bonded Warehouse for Tariff Relief

- Risk Mitigation

### Contact APCT Today 408.727.6442 | APCT.com

#### Board Solutions Printed Circuit

APCT.com

APCT Santa Clara HQ 🗄 APCT Anaheim 🗄 APCT Orange County 🗄 APCT Wallingford 🗄 APCT Global 408.727.6442

714.921.0860

714.993.0270

203.269.3311

203.284.1215

TLB, a global leader in the 4th industrial revolution.

## **TRUST 2030**

Good Company in 20 Years, Great Company in 30 Years.

is specialized in manufacturing PCB for semiconductors. By joining World Class 300 in 2018, we have become a company specializing in materials and components leading the fourth industrial revolution. Based on technology and quality, we will establish ourselves as a material parts company that leads not only Korea PCB but also world PCB.

### DRAM Module / SSD Module

IOT / Build-up Board

Semiconductor TEST B'd & 5G Network System

### TLB CO., LTD.

15602) 305, Sinwon-ro, Danwon-gu, Ansan-si, Gyeonggi-do, Republic of Korea Tel.82-31-8040-2096 Fax. 82-31-492-6623 Domestic Tel. 82-31-8040-2071, E-Mail. cmh@tlbpcb.com Offshore Tel. 82-31-8040-2060, E-Mail. will\_shin@tlbpcb.com

## PROTOTYPES IN 4 DAYS FROM TAIWAN

### **No Tariffs!** Best Quality and Price!

### Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

### Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015

### FIRST PERSON

### 6 CAVEAT LECTOR

An emerging powerhouse in China. Mike Buetow

### MONEY MATTERS

#### 16 ROI

Flirting with disaster. Peter Bigelow

### 17 FOCUS ON BUSINESS

Why you should consider a certification program. Susan Mucha

### TECH TALK

### 18 DESIGNER'S NOTEBOOK

Quieting the noise. John Burkhert

### 20 MATERIAL GAINS

Making advanced technologies affordable. Alun Morgan

### 21 MATERIAL MATTERS

Scratch that etch. Bill Hargin

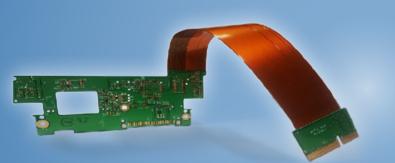

### 23 THE FLEXPERTS

Short and stiff. Mark Finstad

### 40 GETTING LEAN

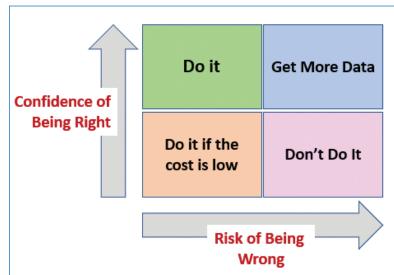

Questions to ask before taking action. John Borneman

### 42 SCREEN PRINTING

01005 apertures. Clive Ashmore

### 42 DEFECT OF THE MONTH

When through-hole connectors move. Bob Willis

### **48 TECHNICAL ABSTRACTS**

### **DEPARTMENTS**

8 AROUND THE WORLD

- 15 MARKET WATCH

- 44 OFF THE SHELF

- 47 MARKETPLACE

#### DECEMBER 2020 • VOL. 37 • NO. 12

### PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

### **FEATURES**

### 24 PCEA

### A New Industry Community Explodes Online During a Global Pandemic

Now a year old, the collaborative educational group is making strides educating PCB engineers. by CHELSEY DRYSDALE

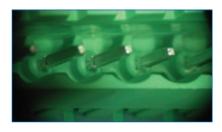

### 27 PCB INSPECTION

### Accurate Microsectioning for High-Volume Production

When it comes to testing in this production setting, doing only a final inspection is insufficient. Processes and tools for accurate lab analysis and defect detection of the highest reliability boards: IPC Class 3/A. by TIM WEBER, PH.D.

### 32 EMS COMPANY OF THE YEAR

### Courage in the Face of Covid

2020 will be remembered as the year of Covid-19. The response was the industry's finest hour. by MIKE BUETOW

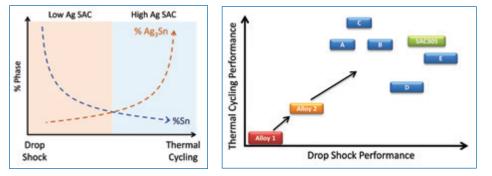

### 34 SOLDER MATERIALS

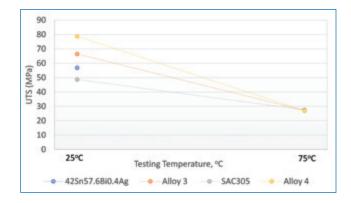

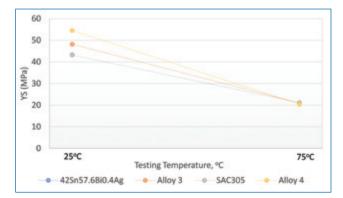

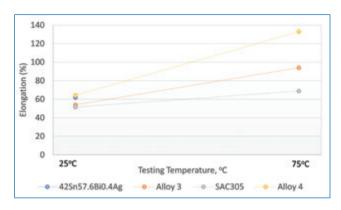

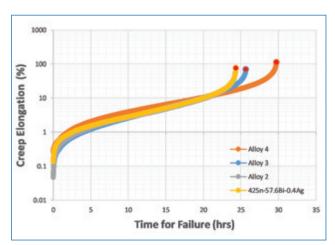

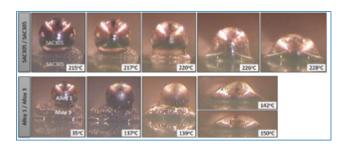

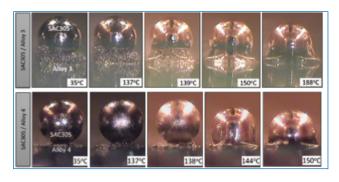

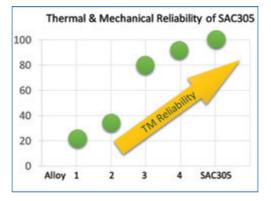

### High-Reliability, Fourth-Generation Low-Temperature Solder Alloys

cover story

The latest version of the eutectic 42Sn58Bi alloy is compared with previous SnBi solders and SAC 305 under a battery of tests, including melting behavior, solder joint formation, tensile tests at room temperature and at 75°C, and high-temperature creep. by MORGANA RIBAS, PH.D., ANIL KUMAR, PRATHAP AUGUSTINE, PRITHA CHOUDHURY, PH.D., and SIULI SARKAR, PH.D.

### IN THE DIGITAL EDITION

### The Digital Route

Meet our leadership. by KELLY DACK

### **Retrospective**

A look back at friends and colleagues who left us in 2020.

### ON PCB CHAT (pcbchat.com)

The SMTA with MARTIN ANSELM, PH.D.

### **Electronics Data Transfer**

with the IPC-2581 CONSORTIUM

EMI Simulation Tools with BRAD GRIFFIN

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

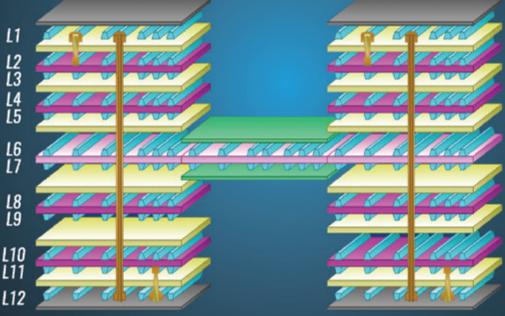

## Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

### When you're in a rush call RUSH PCB

Affordable Pricing • Satisfaction Guarantee • Fast Response • Free Quote • Fast Shipping HDI Boards • Stacked Micro Vias • 2 mil line & Space • Flex & Rigid Flex

### Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL

www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

# UPGRADE YOUR KNOWLEDGE

Learn about THERMAL DESIGN CONSIDERATIONS in our latest e-book and view our growing library of resources created by the PCB design experts at EMA Design Automation.

Download the FREE e-book at: go.ema-eda.com/LearnThermal

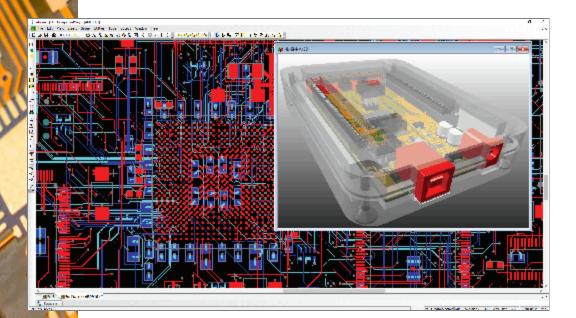

### COMPREHENSIVE PCB DOCUMENTATION

Use 3D Models for Superior PCB Assembly Illustrations

Manage Layer Stackup Design and Materials

### BluePrint-PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings to drive fabrication.

of imported CAD data as a 3D PCB

Lowers documentation cost and time

Increases documentation detail & accuracy

Shortens PCB design cycles

Reduces documentation time by 60-80%

### downstreamtech.com • (508) 970-0670

©2020 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

### PRINTED CIRCL **DESIGN** & FA pcdandf.com

circuitsassembly.com

### **EDITORIAL**

EDITOR IN CHIEF Mike Buetow 617-327-4702 | mbuetow@upmediagroup.com

SENIOR EDITOR Chelsey Drysdale 949-295-3109 | cdrysdale@upmediagroup.com

DESIGN TECHNICAL EDITOR Pete Waddell

EDITORIAL OFFICE P.O. Box 470, Canton, GA 30169

#### PCD&F CONTRIBUTING EDITORS

Akber Roy, Peter Bigelow, John Burkhert, Mark Finstad, Bill Hargin, Nick Koop, Greg Papandrew

CIRCUITS ASSEMBLY CONTRIBUTING EDITORS AND ADVISORS Clive Ashmore, David Bernard, Robert Boguski, John D. Borneman, Joseph Fama, Susan Mucha, Chrys Shea, Jan Vardaman, Ranko Vujosevic

### PRODUCTION

ART DIRECTOR AND PRODUCTION blueprint4MARKETING, Inc. | production@upmediagroup.com

### SALES

SALES DIRECTOR Frances Stewart 678-817-1286 | fstewart@upmediagroup.com

SENIOR SALES ASSOCIATE Brooke Anglin 404-316-9018 | banglin@upmediagroup.com EXHIBIT SALES

Frances Stewart 678-817-1286 | fstewart@upmediagroup.com PRINT/FLECTRONIC REPRINTS

cdrysdale@upmediagroup.com

### SUBSCRIPTIONS

For changes, additions or cancellations: subscriptions@upmediagroup.com

### **UP MEDIA GROUP, INC.**

PRESIDENT Pete Waddell

VICE PRESIDENT. SALES AND MARKETING Frances Stewart

VICE PRESIDENT. EDITORIAL AND PRODUCTION Mike Buetov

DIRECTOR OF GROUP SHOWS

Alyson Corey | acorey@upmediagroup.com

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. For others, annual Subscription Rates in U.S. funds are: \$80 (U.S. and Canada), \$145 (all other countries). Single copy price is \$8.50. All subscription and single copy orders or inquiries should be directed to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169, email subscriptions@upmediagroup.com. Photocopies and issues on Microfilm/Microfiche (16mm, 33mm or 105mm) are available from University Microfilms International, 300 N. Zeeb Rd., Ann Arbor, MI 48106, Telephone 313-761-4600.

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by UP Media Group Inc., PO Box 470 Canton, GA 30169. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

Periodicals postage paid at Canton/Ball Ground, GA, and additional mailing offices. © 2020, UP Media Group, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS Assembly is forbidden without written permission.

Postmaster: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169.

The **ORIGINAL** Conference and Exhibition for Printed Circuit Board Design, Fabrication and Assembly on the **EAST COAST**.

### Conference: May 10 - 12 Exhibition: Tuesday, May 11

Best Western Royal Plaza Hotel & Trade Center Marlborough, MA

### CAVEAT LECTOR

MIKE BUETOW FDITOR-**IN-CHIEF**

### A New Fox in the EMS Henhouse?

ON HAI, BETTER known as Foxconn, has been the largest EMS/ODM company in the world since 2005, when it catapulted Flextronics to gain the top spot. To be sure, Foxconn's revenues then and now are enhanced by ample non-electronics manufacturing segments, but the depth and breadth of the company is by any measure staggering. In calendar 2019, it reached roughly \$150 billion, a mark that is all the more impressive when you consider it doesn't include sales from some of its largest subsidiaries, such as Innolux, Sharp, and its connector and cable units. Its quarterly revenue alone would make it the largest EMS/ ODM in the world. And its annual output not only eclipses all its customers' electronics sales, sans Apple, but also the next four largest competitors combined.

In pursuit of the almighty dollar, Foxconn is the almightiest. Nothing seems out of its reach. Its founder and erstwhile chairman ran for president of Taiwan. It also dabbled in American politics, putting a massive (if mostly empty) facility smack dab in the soy and corn fields of the district of the then-US House Speaker.

Never one to rest on its success, Foxconn is pushing further upstream into the semiconductor market. Having already snared Albit, three years ago it took a shot at the Toshiba memory business. And as we go to press, Foxconn is making a play for Silterra, the Malaysian maker of ICs, MEMs and sensors.

Hon Hai is on high. In mythical terms, toppling Foxconn would be like defeating Voldemort and Sauron. And then for good measure, maybe kicking the butt of that creepy emperor from Star Wars. Any company would be foolish to take that on, right?

And yet ... from China (where else?) comes an upstart that apparently doesn't believe the EMS/ODM pecking order is set per lapis (set in stone).

Luxshare had just been born when Foxconn ascended to the top of the EMS pyramid. It was founded in 2004, and its Xiexun Electronic manufacturing unit came along late the following year.

Like Foxconn, which got its first big break when Terry Gou convinced Michael Dell to start sourcing its plastic parts, Luxshare came about as a provider of cable assemblies and connectors. Its public offering on the Shanghai Exchange in 2010 produced nary a ripple. Yet a decade later, its annual run rate based on the past four completed quarters is nearly \$13 billion.

That's nothing to sneeze at, but why would Foxconn worry about an imitator it could gobble up in a strategic acquisition?

Two reasons. One, Luxshare has impressed the people it needs to impress. In January 2012, when Apple released its first public list of suppliers, a single

Luxshare facility was on it. Moving forward to 2007, however, Luxshare snagged a deal to build Apple's AirPods in Kunshan. Production of the wireless headphones quickly grew to account for nearly 80% of the plant's total output. As of last year, it had eight plants supplying Apple.

Luxshare's share of Apple's manufacturing is reportedly 5%, which equates to about 58% of its total revenue. That's going to rise, too. As we reported in July, Luxshare has signed a deal worth nearly \$475 million to acquire a pair of Wistron entities in China. Those plants make iPhones, giving Luxshare an added boost into the Apple supply chain.

Two, China Inc. can't be pleased that its biggest private-sector employer has been investing more readily of late in its native Taiwan, India and Vietnam. Moreover, after throwing his hat in the presidential ring, Gou publicly challenged the Communist government in China to recognize Taiwan as a sovereign country. That, coupled with Beijing's Made in China 2025 strategic plan, could be more than enough to push the weight of the world's second-largest economy behind Luxshare.

Foxconn reportedly is concerned, enough so that, per Reuters, it convened a task force to study the upstart competitor, a move launched by none other than Gou himself. Among the questions: Is China's government supporting Luxshare?

Luxshare's growth has been fueled by acquiring suppliers to Apple. Is Foxconn about to be outfoxed? We are about to find out.

mbuetow@upmediagroup.com

@mikebuetow

P.S. As we come to the end of this most trying year, we thank our readers and customers for your ongoing support, and wish you all a healthy, prosperous 2021.

## The Gears of The PCB Machine **Run Smoother With APCT**

DFM Expertise & Quick-Turn Capability for NPI; Complete Offshore Management for Production

### DOMESTIC SOLUTIONS

- Standard to Advanced HDI Technology

- Flex & Rigid Flex Technology

- Complete DFM Support

- Cycle Times Faster Than Industry Standards

- Defense & Aerospace Certifications

### OFFSHORE SOLUTIONS

- One Point of Contact

- Seamless Recipe Transfer

- VMI & Kanban Programs

- U.S. Bonded Warehouse for Tariff Relief

- Risk Mitigation

### Contact APCT Today 408.727.6442 | APCT.com

Printed Circuit Board Solutions

APCT.com

APCT Santa Clara HQ 408.727.6442

**APCT Anaheim** 714.921.0860

APCT Orange County 714.993.0270

APCT Wallingford 203.269.3311

**APCT Global** 203.284.1215

### **PCDF** People

Dyconex promoted Dr. Jonas Kottman to vice president operations. He joined the fabricator last year as manager opera-

The FED trade group awarded the PCB Design Award to Thomas Blasko (CiBoard Electronic), Georg Scheuermann (TQ-Systems) and Michael Matthes (Wittenstein Cyber Motor).

GoPro named John Burkhert Jr. senior PCB layout engineer. He has more than 30 years' experience in PCB design with Velodyne, Google, Qualcomm and others.

Jacobs Technology named Russ Pringle printed circuit board designer.

L3Harris Technologies named Cameron Stouder ECAD tools and library team lead.

Lone Star Circuits promoted Lance Riley to chief operating officer. He has been with Lone Star since 2017, and previously held engineering and sales executive roles with TTM and

Unicircuit.

### **PCDF Briefs**

Apple is expected to accelerate the adoption of LCP (liquid crystal polymer)-based flexible PCBs for the antenna modules to be used by its future iPhone lineup supporting 5G mmWave technology, according to industry sources.

Cicor expanded production capacity at its Wangs, Switzerland, fabrication site.

Exception PCB purchased a Ucamco Ledia direct imager.

Gerber Labs, an Orange County-based engineering startup, is rolling out a platform that makes custom PCBs accessible to electrical engineering students, hobbyists and small businesses.

Hitachi Chemical, a longtime leader in the development of electronic materials, changed its name to Showa Denko Materials, reflecting the latter's acquisition of the venerable Japanese firm.

**ILFA** has acquired circuit board distributer Skytech Europe for an undisclosed sum.

Insulectro rolled out an online shopping center for conductive inks and pastes plus advanced substrates and films.

Koh Young joined the IPC-DPMX (IPC-2581) Consortium.

### California Startup Says It Has Answer to High-Density, Ultra-Thin Designs

SAN FRANCISCO - "Innovation starts at the bottom," a San Francisco startup says, underpinning its belief printed circuit boards will drive the next big leap in innovation.

Thintronics, the new firm founded last year by chemist Dr. Stefan Pastine, wants to help companies make better products through "reconceptualizing PCB design."

The materials company has ideas for lower layer count designs for devices that must be small or lightweight or both, such as mobile, IoT, wearables and autonomous systems for self-driving cars and LiDAR or drones.

Its hypothesis is companies capable of using the PCB to drive end-product innovation are few and far between, but superior materials will help design engineers shed design rule constraints, while manufacturers benefit from shorter processing cycle times.

Its solution? A novel thin, low dielectric constant, skew-free substrate. In this case, how thin is "thin?" The company defines it as a 1.0-mil thick dielectric for standard products and 0.5 mils for "ultra" thin.

According to Thintronics, the novel material can enable product designers to cut board thickness and layer counts in half without a loss in interconnect density, or reduce PCB thickness by 35% with no layer count penalty, while doubling interconnect density.

The company's claims are eye-opening: a 75% reduction in lamination cycle times and a 60% reduction in post-processing times, the latter because the Thintronics material cuts desmear times and requires no plasma. The dielectric constant range is 3.0-3.1, and the impedance tolerance is 5%. Moreover, Thintronics touts the "unlimited" prepreg shelf life. The dielectric spacing is 1 mil or 0.5 mils, and the material is CAF-resistant.

"Thintronics was created not by tweaking existing PCB materials, but by inventing new materials, starting from the molecular level. Our bottom-up molecular design approach creates products that, at their molecular core, are vastly different than any material in the world, much less the dielectrics used in the PCB market today," the firm explains on its website.

Pastine comes to the PCB industry by way of Connora, a designer of thermoset plastics and composites that have the added feature of low-energy recyclability. Connora, which Pastine cofounded in 2011, was acquired by Aditya Birla Chemicals in 2019, freeing up Pastine to embark on his current pursuit.

As of November, longtime materials executive Tarun Amla has joined as president and chief operating officer. Amla was previously CTO at ITEQ and has held top technology jobs at Shengyi and Isola as well.

"We share the same view that it is sad that the USA has let its grip on dielectric technology slip away," Pastine said in a LinkedIn post announcing Amla's arrival. "We both expect to reverse the trend vis-à-vis the coupling of advanced simulation with Thintronics' bottom-up, molecular-level design approach to inventing new dielectric materials." (MB)

### Electronic Design Tool 'Morphs' Interactive Objects

We've come a long way since the first 3-D-printed item came to us by way of an eye wash cup, to now being able to rapidly fabricate things like car parts, musical instruments, and even biological tissues and organoids.

While much of these objects can be freely designed and quickly made, the addition of electronics to embed things like sensors, chips, and tags usually requires that you design both separately, making it difficult to create items where the added functions are easily integrated with the form.

Now, a 3-D design environment from MIT's Computer Science and Artificial

# PCB WEST 2021 Conference & Exhibition

### Conference: August 31 - September 3 Exhibition: Wednesday, September 1

### SANTA CLARA CONVENTION CENTER, CA

pcbwest.com

**Meltex** is building a new fab plant in Japan and increasing production capacity in Thailand, according to reports.

The **Redfern Companies** will acquire **Automated Chemical Solutions**, a provider of specialty chemicals for PCBs.

Soochow University researchers have developed a new approach to printed electronics whereby ultra-low-power electronic devices could recharge from ambient light or radio frequency noise. The approach paves the way for low-cost printed electronics that could be seamlessly embedded in everyday objects and environments.

Smartphone OEMs are extending fully integrated modem-RF system designs to support 5G and LTE implementations over their flagship devices, a new teardown analysis from **System Plus Consulting** says.

**Unimicron Technology's** PCB fabrication plant in Taoyuan, Taipei, sustained a fire that sent at least 10 persons to the hospital.

A section of the US Senate's latest NDAA bill requires US companies to stop using PCBs made in China, Iran, North Korea and Russia by fiscal 2033.

### **CA** People

Circuit Works named **Luis Gallegos** manufacturing engineer manager.

Creative Electron named **Courtney Kalb** client specialist.

Electrolube appointed Carolyn McAllister European sales manager. She has a degree in chemistry from the University of Nottingham, and spent the past six years with the com-

pany's research and development team.

Nortech Systems named **Christopher D**. **Jones** chief financial officer and senior vice president of finance.

STI Electronics announced **Emery "Gra**ham" Goff, a student at Calhoun Community College, as recipient of the 2020/2021 Jim D. Raby Scholarship.

Z-Axis promoted **David Figler** to purchasing manager. He joined the purchasing team in 2019, and has more than 20 years' experience in electronics purchasing and commodity

management with Caldwell Manufacturing Company, Alstom, ITT Gould Pumps and Pfaudler.

Zollner promoted **Erick Fabian** to supply chain designer.

Intelligence Laboratory (CSAIL) lets users iterate an object's shape and electronic function in one cohesive space, to add existing sensors to early-stage prototypes.

The team tested the system, called MorphSensor, by modeling an N95 mask with a humidity sensor, a temperature-sensing ring, and glasses that monitor light absorption to protect eye health.

MorphSensor automatically converts electronic designs into 3-D models, and then lets users iterate on the geometry and manipulate active sensing parts. This might look like a 2-D image of a pair of AirPods and a sensor template, where a person could edit the design until the sensor is embedded, printed, and taped onto the item.

To test the effectiveness of MorphSensor, the researchers created an evaluation based on standard industrial assembly and testing procedures. The data showed that MorphSensor could match the off-the-shelf sensor modules with small error margins for both the analog and digital sensors.

"MorphSensor fits into my long-term vision of something called 'rapid function prototyping,' with the objective to create interactive objects where the functions are directly integrated with the form and fabricated in one go, even for non-expert users," says CSAIL PhD student Junyi Zhu, lead author on a new paper about the project. "This offers the promise that, when prototyping, the object form could follow its designated function, and the function could adapt to its physical form."

MorphSensor in action. Imagine being able to have your own design lab where, instead of needing to buy new items, you could cost-effectively update your own items using a single system for both design and hardware.

For example, let's say you want to update your face mask to monitor surrounding air quality. Using MorphSensor, users would first design or import the 3D face mask model and sensor modules from either MorphSensor's database or online

open-sourced files. The system would then generate a 3D model with individual electronic components (with airwires connected between them) and color-coding to highlight the active sensing components.

Designers can then drag and drop the electronic components directly onto the face mask, and rotate them based on design needs. As a final step, users draw physical wires onto the design where they want them to appear, using the system's guidance to connect the circuit.

Once satisfied with the design, the "morphed sensor" can be rapidly fabricated using an inkjet printer and conductive tape, so it

An MIT team used MorphSensor to design multiple applications, including a pair of glasses that monitor light absorption to protect eye health.

can be adhered to the object. Users can also outsource the design to a professional fabrication house.

To test their system, the team iterated on EarPods for sleep tracking, which only took 45 minutes to design and fabricate. They also updated a "weather-aware" ring to provide weather advice, by integrating a temperature sensor with the ring geometry. In addition, they manipulated an N95 mask to monitor its substrate contamination, enabling it to alert its user when the mask needs to be replaced.

In its current form, MorphSensor helps designers maintain connectivity of the circuit at all times, by highlighting which components contribute to the actual sensing. However, the team notes it would be beneficial to expand this set of support tools

## The Circuits Assembly Directory of EMS Companies

Build your EMS database

3,000+ facilities worldwide

Sortable in Excel

Unrestricted use

Includes contact info, no. of lines, markets served and more!

circuitsassembly.com/dems

### **CA Briefs**

**ABAJ Group** is setting up a TV and AC manufacturing facility near Mehsana, India.

AIM Solder opened a 12,000 sq. ft. ISO 9001-certified solder manufacturing facility in Malaysia.

Aimtron purchased an Austin American Technology X30 stencil cleaner, its second.

Apple has reportedly suspended new business with Pegatron after discovering labor violations at a student workers' program.

In the two months since **Huawei** lost access to American technology, Japanese makers of electronic parts have enjoyed a fresh wave of orders from other smartphone manufacturers seeking to claim market share now up for grabs.

**CalcuQuote** has partnered with **Rochester Electronics** to build a new integration that offers up-to-date information through the CalcuQuote platform.

**Cogiscan** named **AES** to handle sales and service throughout Vietnam.

**Compal Electronics** has been increasingly requested by its clients to diversify manufacturing bases beyond China, particularly for smart devices, according to a company executive.

**Compal Electronics** and **Cisco** have partnered to work in the 5G AloT market and provide integrated network solutions.

**Computrol** installed a **Thermaltronics** TMT-R9800S solder robot.

**Creative Electron** has been awarded a US patent for Al-powered programming of x-ray inspection systems.

**East/West Manufacturing** will invest more than \$5 million toward a new electronics manufacturing facility in Round Rock, TX, with plans to be open by next August.

**Elisa Oyj** made a strategic investment to hold a majority stake in **CalcuQuote**.

FoundPac Group is considering spinning off its laser stencil unit, Dynamic Stencil, and is looking at IPO possibilities.

**Foxconn** dismissed media reports suggesting a souring relationship between the ODM and **Apple** as "nonsense" and vowed legal action. It reportedly formed a task force to fend off competition from **Luxshare**, which is targeting Apple as a key customer.

**Foxconn** chairman Liu Young-way said the company hopes to take 10% of global market share for electric vehicles between 2025-27, and that it has been in talks with multiple carmakers for future cooperation. even further, where future versions could potentially merge electrical logic of multiple sensor modules together to eliminate redundant components and circuits and save space (or preserve the object form).

Zhu wrote the paper alongside MIT graduate student Yunyi Zhu; undergraduates Jiaming Cui, Leon Cheng, Jackson Snowden, and Mark Chounlakone; postdoc Michael Wessely; and Professor Stefanie Mueller.

This material is based upon work supported by the National Science Foundation. (By Rachel Gordon. This article was first published in MIT News and is republished here with permission of Rachel Gordon and MIT.)

### Victory Giant Technology Plans Second 'Smart' PCB Plant

**SHANGHAI** – Victory Giant Technology will begin work on a new smart manufacturing factory here in the first quarter 2021, the printed circuit fabricator's second such facility.

The new plant is expected to be operational by the second quarter 2022.

The plant is a larger version of VGT's high-volume Industry 4.0 factory, which opened last year. The site relies on AGVs and other automation, plus VGT developed intelligent ERP software and real-time product metrology to reduce labor and shorten production cycle time. (MB)

## Ticer to Buy Materion LAC Assets, Head Off Supply Break

**CHANDLER, AZ** – Ticer Technologies announced an agreement to acquire certain manufacturing assets from Materion's Large Area Coatings division, effective Jan. 1.

The deal will help Ticer avoid a potential supply disruption, the company said.

The companies did not disclose financial terms.

Ticer, which makes thin film embedded resistor foils, will acquire LAC's vacuum deposition/sputtering production equipment, which will remain at the firm's facility in Windsor, CT, as well as certain staff. Processes, equipment and raw materials will remain the same during the transition process, the companies said.

"This is a significant improvement in capacity and supply leadership long sought by Ticer," said David Burgess, president, Ticer. "We believe our global customers will benefit from the flexibility and supply chain control afforded by this change."

Ticer had previously announced a potential supply chain disruption due to the planned divestiture of Materion's LAC division. The acquisition will obviate that potential disruption and make product requalification unnecessary. (MB)

### BAE Breaks Ground on Massive Electronics Factory

**CEDAR RAPIDS, IA** – BAE Systems is investing more than \$100 million to build a stateof-the-art manufacturing and R&D facility here. The center includes a 278,000 sq. ft. factory and research and development center located on a 32-acre site in Cedar Rapids.

Besides the large factory, the site will include several hundred offices, workstations, and flexible workspaces, and classified and unclassified labs. The building was designed for growth, with the ability to add 50,000 sq. ft. of additional space in the future.

The facility will support the company's newly acquired Navigation & Sensor Systems business, which makes mission-critical military GPS products. The new building will bring the company's local design and production employees from multiple locations into a single center of excellence with modern manufacturing, engineering, and office space. Wenge Yang Vice President, Marketing Entegris

### YOU MAKE CRITICAL DECISIONS.

### WE GIVE YOU CONFIDENCE.

### Access reliable SEMI data to uncover new business opportunities.

Learn how SEMI IS MORE by exploring how our Market Data products with leading forecast-accuracy can help you make critical business decisions with confidence, visit **semi.org/semiismore**.

### SEMI IS MORE

Foxconn said its commitment to Wisconsin has not wavered, and it will continue to work with the local government to create new jobs and attract new investment to the state.

**Incap Electronics Estonia** opened a new SMT production line in its factory in Kuressaare.

**Indium** and **RENEX** have formed a strategic partnership for the service of PCB and engineered solder materials in Poland.

**Intellitronix** installed a **Europlacer** iineo+ pick-and-place machine.

**Kyzen** named **Solder Connection** to sell and support its cleaning products in Ireland.

LeddarTech announced a collaborative project agreement with Flex for the development of a LiDAR evaluation kit and related service.

**NASA** has selected **Nokia** to build the first cellular network on the moon.

Niche Electronics and QCMS have selected MIRTEC's MV-6 OMNI 3D AOI.

After being defunct for six years, a former **Nokia** factory in Sriperumbudur, India, came to life as electronics manufacturer **Salcomp** launched commercial operations from the plant.

**Nordson Dage** named **Murray Percival** representative of its Assure Series of x-ray component counters in the Midwest US.

**OnePlus** will allocate up to Rs 100 crores (\$14 million) in new phone and TV manufacturing sites and other expansion in India.

**Ryder Industries** is increasing its electronics manufacturing services capacity by investing in two new facilities in Taiwan.

**Square E** is shutting its EMS plant outside Louisville, closing the book on an operation that lasted more than 40 years.

Syrma Technology merged with SGS Tekniks in a cash and stock deal of Indian EMS companies.

University of Washington engineers have created simple plastic devices without batteries or semiconductors that can wirelessly interact with smartphones and computers.

A Wistron subsidiary announced it will spend \$28.7 million to acquire a plant from Western Digital in Malaysia. The facility will improve operational efficiency, optimize production, and enhance the company's ability to deliver high-quality military GPS products to the warfighter. Construction began in October and is expected to finish in 2022.

"Our world-class military GPS business is built on the rich talent pool in Greater Cedar Rapids," said John Watkins, vice president and general manager of Precision Strike & Sensing Solutions, BAE Systems. "This investment will provide our hightech engineering and manufacturing experts with a world-class workspace and the tools to enhance operational excellence." (MB)

### New Study Lays Groundwork for US Semi Fab Resurgence

**WASHINGTON** – A new report finds the US government has a strategic opportunity to reverse the decades-long trajectory of declining chip manufacturing in America, strengthen national security, make domestic supply chains more resilient, and make the country one of the most attractive places in the world to produce semiconductors.

The report, issued in September by the Semiconductor Industry Association and the Boston Consulting Group, says the US share of the global semiconductor fabrication industry has dropped to 12%, from 37% in 1990. Moreover, just 6% of new capacity is earmarked for the US, the authors say. In contrast, China will add nearly 40% of new capacity, making it the largest semiconductor manufacturer in the world.

The US is slowed by the high cost of fabs, which is about 30% higher over a 10-year period than key sites in Southeast Asia, and 37% to 50% higher than China. Much of the difference – up to 70% – is due to government subsidies and incentives that gravitate manufacturers to the Pacific Rim.

Nonetheless, the US could grab back up to twice its current share through a series of targeted government incentives, the authors assert. Such a strategy would ensure supply for critical end-markets such as aerospace and defense and increase employment in the sector by 70,000, while providing a boost to political issues such as trade balances. The report says the right combination of incentives could generate 19 new fabs, each staffed with 3,000 to 6,000 workers.

Ironically, the study shows the US holds dominant positions in EDA software, core IP and manufacturing equipment. Its share of the materials and manufacturing sectors, however, is roughly 12% each, and it lacks the leading-edge capabilities of Taiwan (TMSC) and South Korea (Samsung). As fabless models have taken hold, the US now lags every major chip-producing market, including Japan and Europe. (Intel's plans to sell its manufacturing plants, announced after the report was released, will only accelerate this trend.)

The authors assert government investment of \$20 billion to \$50 billion would lead to the addition of 14 to 19 new fabs in the US, at the peak making it the top site for new plants outside China. Such a move would boost the US share of the world market to 14% by 2030, versus 10% if there were no changes to the status quo. (MB)

#### EDITED by CHELSEY DRYSDALE

| COMPUTERS BOOT UP                                                                                                                                                 |      |               |      |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|-------|

| Trends in the US electronics<br>equipment market (shipments only)                                                                                                 | JUL. | % CHA<br>Aug. |      | YTD%  |

| Computers and electronics products                                                                                                                                | 4.1  | 0.5           | 1.2  | 2.9   |

| Computers                                                                                                                                                         | -2.8 | -0.7          | 3.3  | -10.1 |

| Storage devices                                                                                                                                                   | 2.9  | -1.3          | -7.4 | 34.5  |

| Other peripheral equipment                                                                                                                                        | 23.7 | 3.0           | -9.2 | 8.6   |

| Nondefense communications equipment                                                                                                                               | 9.2  | 1.7           | 2.8  | 9.4   |

| Defense communications equipment                                                                                                                                  | -3.8 | 6.2           | -5.1 | 4.0   |

| A/V equipment                                                                                                                                                     | 10.7 | -3.0          | 2.8  | -9.3  |

| Components <sup>1</sup>                                                                                                                                           | 4.5  | 0.7           | -0.7 | 9.5   |

| Nondefense search and navigation equipment                                                                                                                        | 1.2  | -0.8          | -1.1 | -5.9  |

| Defense search and navigation equipment                                                                                                                           | 1.7  | -3.2          | 2.6  | 2.5   |

| Medical, measurement and control                                                                                                                                  | 1.2  | 2.8           | 0.5  | -1.9  |

| <sup>(</sup> Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted.<br>Source: U.S. Department of Commerce Census Bureau, Nov. 3, 2020 |      |               |      |       |

| US MANUFACTURING INDICES                              |      |      |      |      |      |  |  |  |

|-------------------------------------------------------|------|------|------|------|------|--|--|--|

|                                                       | JUN. | JUL. | AUG. | SEP. | OCT. |  |  |  |

| PMI                                                   | 52.6 | 54.2 | 56.0 | 55.4 | 59.3 |  |  |  |

| New orders                                            | 56.4 | 61.5 | 67.6 | 60.2 | 67.9 |  |  |  |

| Production                                            | 57.3 | 62.1 | 63.3 | 61.0 | 63.0 |  |  |  |

| Inventories                                           | 50.5 | 47.0 | 44.4 | 47.1 | 51.9 |  |  |  |

| Customer inventories                                  | 44.6 | 41.6 | 38.1 | 37.9 | 36.7 |  |  |  |

| Backlogs                                              | 45.3 | 51.8 | 54.6 | 55.2 | 55.7 |  |  |  |

| Source: Institute for Supply Management, Nov. 1, 2020 |      |      |      |      |      |  |  |  |

| KEY COMPONENTS                                                                                                                                                             |       |       |       |                            |                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------------------------|--------------------|--|

|                                                                                                                                                                            | MAY   | JUN.  | JUL.  | AUG.                       | SEP.               |  |

| Semiconductor equipment billings <sup>1</sup>                                                                                                                              | 13.5% | 14.4% | 26.7% | 32.5% <sup>r</sup>         | 40.3% <sup>p</sup> |  |

| Semiconductors <sup>2</sup>                                                                                                                                                | 4.82% | 4.9%  | 4.23% | <b>4.9</b> 4% <sup>r</sup> | 5.79% <sup>p</sup> |  |

| PCBs <sup>3</sup> (North America)                                                                                                                                          | 1.10  | 1.12  | 1.00  | 0.94                       | 0.93               |  |

| Computers/electronic products <sup>4</sup>                                                                                                                                 | 5.44  | 5.44  | 5.28  | 5.22 <sup>r</sup>          | 5.18p <sup>p</sup> |  |

| Sources: <sup>1</sup> SEMI, <sup>2</sup> SIA (3-month moving average growth), <sup>3</sup> IPC, <sup>4</sup> Census Bureau, <sup>p</sup> preliminary, <sup>r</sup> revised |       |       |       |                            |                    |  |

### Hot Takes

- Taiwan's PCB industry output in 2021 is expected to grow 2-3% to NT\$690 billion (US\$24 billion) because of 5G. (TPCA)

- Worldwide silicon wafer area shipments rose 6.9% yearover-year but were down 0.5% sequentially to 3,135 million sq. in. in the third quarter. (SEMI)

- Global tablet shipments rose 24.9% year-over-year to 47.6 million units in the third quarter. (IDC)

- Worldwide smartphone market shipments declined 1.3% year-over-year in the third quarter. (IDC)

- Global notebook shipments are forecast to rise at a CAGR of 0.9% from 2020 to 2025. (Digitimes Research)

- Singapore's factory output expanded 24.2% year-on-year in September on growth in semiconductor production. (Economic Development Board)

■ Tin use contracted 5.4% in 2019 to 359,200 tonnes and is expected to decline a further 5.9% in 2020 because of the Covid-19 pandemic. (ITA)

- The AR headset market will grow to over \$20 billion by 2030. (IDTechEx)

- Global shipments of PCs (desktops, notebooks, and workstations) rose 14.6% year-over-year to 81.3 million units in the third quarter. (IDC)

- PC memory chip and device supplies are falling short of demand, with the tight supply unlikely to ease until the first quarter 2021. (DigiTimes)

- Companies are rushing to use AI, but few see a payoff, with only 11% reaping a "sizable" return on their investments. (Boston College)

### Preparing Your Company for Disaster

Businesses can't plan for everything, but with the right prep they can adapt.

DECEMBER IS FINALLY here. Mercy knows it seems to have taken forever to bring this most unusual year to a close. I keep pondering the question customers inevitably ask during a supplier audit: What contingencies are in place for "unforeseen and unthinkable" disasters and events? If anyone had asked me a couple years ago to come up with a plan to deal with a global pandemic I would have thought them to be crazy for asking. And yet, that was 2020!

The one takeaway from this crazy year is you can never plan for everything. Paradoxically, good planning makes it easier to deal with the unimaginable.

Business planning takes numerous forms. Most people think first of the financial budget planning, usually led by finance and account staffs. Visions of building a budget, whether bottom-up or top-down, as a tool to measure specific activities against comes to mind. This type of planning revolves around predicting core operating activities that are repeatable, predictable and highly measureable. While important, if not essential, for the operations folk to run the "business as usual," that budget is only one aspect of planning.

Capital planning is the kissing cousin to financial budgeting. The one major difference is that planning for the acquisition of capital assets, facilities upgrades, or working capital needs more of a "what if?" in the equation. Multiple scenarios must be taken into consideration to hedge both the best- and worst-case scenarios. Such planning incorporates potential risks and focuses on what "could" occur, rather than what is "expected" to take place.

Contingency planning is a horse of a different color. While the event, situation, occurrence(s) and magnitude of the contingency being planned for may differ, the common trait is the events are major distractions, all unprecedented and usually quite unimaginable. One cannot do this type of planning alone, and this type of planning may seem a waste of time, as the contingency most likely will never occur.

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

For many, navigating and surviving the unimaginable (and most likely unplanned for) global pandemic was, in part, accomplished because the organization performed *some* kind of contingency planning and was able to leverage pieces of those plans to adapt to the situation at hand. Plans for any extreme disaster or crisis share several basic elements.

*Flexibility* is critical for everyone, especially the leadership team. An unprecedented event requires all involved to be flexible, adaptable and ready to shift gears on-the-fly to manage the crisis. Flexibility of one's mind, let alone an entire organization, doesn't

just happen. Leadership needs to plan for how it will adapt and enable a department, division or company to move in different directions if needed.

*Cross-trained staff* is one of the best ways to enable flexibility. Even those in very specialized roles or the most mundane jobs need to move around the organization periodically so they are exposed to other aspects of the process and see tasks they may be able to handle if and when necessary. A cross-trained staff does not happen organically. It takes planning and advanced training to have employees who can move in and out of different situations and tasks smoothly and effectively.

*Rapid deployment* is critical when dealing with a crisis. Leadership needs to quickly deploy people, ideas, contingency plans, and resources to deal with a given situation. Times like these have no set script. Management needs to utilize the best-available information from wherever it is offered to move decisively and rapidly. Waiting for perfect information, or analysis paralysis, is a surefire way to lose precious time, often the most precious resource.

*Communication* is the most important element, one that makes the difference between a successful attack plan and workers flailing unproductively. Communication is two-way. It is essential that all involved understand the strategy, deployment plan, risk, and basis of information used to make decisions. There is nothing wrong communicating that everyone is working in an unprecedented situation. Equally, it is imperative to listen and take what is reported by those in the line of action forward to the appropriate person(s), so *all* information is taken into consideration. A solid communication environment does not just happen: It is planned for and understood by all.

*Patience* is needed by all and, most important, must be exercised and demonstrated by everyone in the leadership team. While everyone reacts differently, plan on how those in charge will mutually support and demonstrate as much patience as possible while dealing with the challenge so employees don't panic.

Finally, have adequate financial reserves available to tap, if needed. All in charge should know if and when those resources are deployed, so they can be focused on the most critical areas of need.

No organization can plan for and be prepared for every possible event. Moreover, trying to plan for every permutation and combination is not the best utilization of resources. A management team and corporate culture that has the critical elements needed to prepare and respond may make the critical difference when an unimaginable event strikes.

## Opportunity Knocks at the Doors of Continuous Learners

Why you should consider a certification program.

WHEN I LOOK back on my career and consider the key ingredient to my success, I'd say whenever opportunity knocked, I had the right skill set to walk through the door. I was fortunate that my first electronics manufacturing services (EMS) employer had both a tuition refund program that paid for my master's degree in management and an internal management training program. That started me on a path of continuous learning that included multiple certification programs and other training programs. And, as advancement opportunities came up, I had the right qualifications and a results-focused track record.

Company-sponsored educational resources are more limited today. That said, technology has made it possible and convenient to engage in focused continuous learning opportunities. IPC's Certified Electronics Program Manager (CEPM) training and certification program is a good example. What once required multiple trips to training locations and a solid week of classroom time can now be done via computer either in live sessions or through reviews of class recordings. The program was redesigned to an online format in 2017 and now is a six-week program with two twohour classes per week, providing overviews of program management, sales, cost accounting, materials management, contracts, production planning, quality and leadership. Students are assigned to teams that complete a case study each week related to the concepts presented. A variety of online exercises reinforce key concepts. The goal is to ensure participants are provided a common framework of knowledge and the opportunity to interact with peers to discuss best practices. Information on the program and upcoming dates is available here: https://www.ipc.org/contentpage.aspx?pageid=cepm.

If you have a degree, why consider a certification program? The reality is many educational disciplines have only a peripheral relationship to the job functions performed. Employees learn on the job, and the result may be gaps in knowledge. A certification program lays out a formal framework of knowledge related to a specific discipline. It helps those who have learned on the job fill knowledge gaps. Another benefit of certification programs is students are usually working in their fields. The knowledge shared in class discussions tends to be hands-on and relevant to each student's current job. A byproduct is often better focus on skills improvement areas or stronger focus on incorporating best practices at work.

Most EMS salespeople and program managers don't have a degree that specifically relates to those functions. Most have a technical/engineering or business background. In some cases, this may be the first manufacturing-related job an individual has held. The result is sales and program managers are often strong on either the technical or business side of the equation, but not both. IPC's CEPM program is designed to help participants develop balance in business and technical knowledge. There is strong emphasis on setting customer expectations, building a business case, understanding contracts and cost accounting. There is equal emphasis on materials management considerations, production planning and the production process. A leadership section focuses on team motivation and management skills.

CEPM's team aspect is also beneficial. The EMS environment can be stress-filled, which workers may believe is specific to their company. As teams work together on case studies, they typically find the challenges they encounter in their jobs are universal. They also learn there is often more than one "right" way to do things, enhancing the options available to resolve challenges or do their jobs better. Since the program is open to OEM and EMS participants, team activities and class discussion often build a better understanding on both sides about challenges inherent in the outsourcing process.

The focus on building a business case also has benefits. Often the reason a customer says no is because the reason for the request is not adequately explained. Inexperience in the industry or gaps in relevant knowledge are often the root cause of failure to build a business case. The CEPM training focuses on examples of typical business cases used to justify requests related to price changes, DfM recommendation implementation, inactive/obsolete inventory resolution and other common program issues. Combined with a better understanding of common cost drivers and how EMS processes interrelate, this makes it easier to discuss the business case for a change in customer behavior.

The CEPM program is not IPC's only online offering in the EMS management realm. This year they've rolled out a negotiation class, and other classes will follow. First quarter dates for CEPM and negotiation class should be added to the IPC website soon.

Regardless of the training opportunity, consider starting 2021 with a commitment to increase your skills base. Opportunity knocks regularly at the doors of continuous learners.  $\Box$  SUSAN MUCHA is president of Powell-Mucha Consulting Inc. (powellmuchaconsulting. com), a consulting firm providing strategic planning, training and market positioning support to EMS companies, and author of Find It. Book It. Grow It. A Robust Process for Account Acquisition in Electronics Manufacturing Services: smucha@powellmuchaconsulting. com.

### Taming Electromagnetic Interference on a PCB

What's all this noise? Look beyond the wires and connectors to think inside the box.

YOU CAN'T ALWAYS hear it, feel it or see it, but every active electronic device radiates some kind of energy as it operates. For the most part, that's the point. We want to hear the music; we want to feel the air conditioning or see the light. Those are the good things.

Meanwhile, we don't want side effects: static on the radio, compressor noise from the AC or that annoying 60Hz hum from the light fixture bleeding over to my new bass amp. It's these things we try our best to design out of the products we build.

We can adjust the tuner on the radio, and we can install the central AC unit away from the windows. I ordered a noise suppressor and plugged it into a socket where there's no dimmer switches or high current motors plugged in. Then the amplifier and pedal board power cords were routed into the special apparatus, and I no longer get a wave of white noise when this MacBook Pro searches for a WiFi signal.

Even if the emissions cannot be perceived with our five senses, they can be detrimental to the performance of the circuit or spill out onto other nearby electronics. We use metal for the device housings for multiple reasons. Beyond its heat-shedding property, we want to keep the noise inside the box while preventing other noise from getting in. Those are the two central tenets of coexistence.

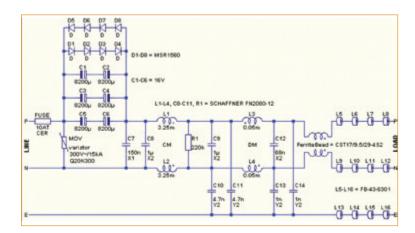

If you want to chain a bunch of gain-stages together, it helps to start with clean power and a common ground path. The fix for noise issues is almost always additive. The new schematic you get just before the prototype goes for FCC certification usually has a new ferrite bead, maybe a diode here and there and some retuned bypass capacitor values.

Generally speaking, a few factors cause signal degradation. One of the main factors is long traces. The farther a signal travels, the more likely it will end up near a bad neighbor. In this case, "bad" can mean noisy or susceptible to picking up noise. I'm tempted to open up that big, white plastic wall-wart for this laptop to see if it has any shielding.

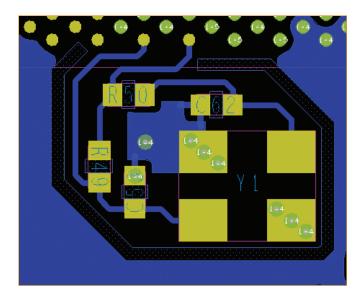

Getting the dirt out of the wall juice is the first line of defense. At the PCB level, the second line of defense is to shield the most vulnerable victim traces from exposure to the outside world. EMI shielding is carried out around the noise makers, as well as the sensitive signals (FIGURE 2). One of the best ways to reduce coupling between those two types of elements is simply adding space.

Placement and orientation of components and printed antennas go a long way toward mitigating noise issues. However, the luxury of a generous PCB is a rarity. No matter the amount of electronics, printed circuit boards cost money, so less is more. Doing more with less is our existential challenge. A lot of designs have an external oscillator, so let's take a look at that.

The crystal (FIGURE 3) is placed close to the IC, but we could achieve shorter traces by rotating the circuit 90° clockwise. Note the route keep-out that creates a moat that separates the outer layer ground plane from the pins of the crystal. Putting a ground via on the edge of the shape defeats the purpose. Ideally,

FIGURE 1. My Blackboard with a new surge protector that also filters EMI and RFI.

FIGURE 2. These components are the typical building blocks of a noise suppressor circuit. (Source: Audio Karma)

JOHN BURKHERT JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for highspeed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly

## Understanding High-Speed onstral graphics & equations; references on via impedance

FREE new e-book!

pcdandf.com/pcdesign/constraints

This fabulous treatise allows PCB designers and engineers to understand all the important constraints and determine their values.

SECOND

details on edge rates;

written by Charles Pfeil

Charles Pfeil has spent over 50 years in the PCB industry as a designer, owner of a service bureau, and in engineering management and product definition roles at Racal-Redac, ASI, Cadence, PADS, VeriBest, Mentor Graphics, and Altium. He was the original product architect of Expedition PCB.

there are one or more XO return pins for a direct ground path back to the SOC.

A mechanical outline for a PCB typically comes from a

mechanical engineer with little to no electrical training. They might give us one part of the board where tall components are allowed. Wouldn't you know it, the tall components include the crystal. All that thing does is sit there making noise, so something has to be done with the long link back to the mothership.

Internal routing is more effective than running an aggressor on the outer layers. That notion is predicated on the fact there will be an unbroken ground plane both above and below the trace. Taking it a step further, a dedicated shape on the signal layer that encloses the trace is a good policy.

In **FIGURE 4**, the ground net is highlighted in green. The cyan and magenta represent layers 3 and 5. The via labels indicate the span of the microvias. We want to tie the relevant ground planes together, but not necessarily any other ground layers. If we were to flood ground on the routing layers, the full plane would not engulf these guard-bands. You might have noticed several signal vias without an adjacent ground via. The

FIGURE 3. A crystal and its passive parts.

**FIGURE 4.** Guard bands around noisy traces. The surrounding low-speed signals benefit from the isolation.

signals on both layers see the ground plane on layer 4, so the ground via is a feel-good measure.

Note: I used a 2-4 microvia stack for layer three and a 4-6 microvia stack to shield the layer five routes. Finally, going beyond a single return via for the transition from layer three to layer five, there is a cluster of 2-6 vias around the 3-5 signal vias. The idea is to form a coaxial Faraday cage in the z-axis. In cases where there isn't this amount of space, do your best to isolate the noisy party.

We hear a lot about length-matching, phase tuning and taking care of the impedance of high-speed connections. We know vias are a discontinuity to avoid if possible. Routing over a split or void in the reference plane is a no-no. All these impedance and timing rules are also necessary to keep EMI to a minimum. nets.

Staking down the edges of the ground planes, including the voids, makes for a PCB that runs quieter and provides a substantial path for thermal dissipation. Once you've digested all the basic rules around EMI, you'll see PCBs in a different way. We can immediately spot it when an artist tries to draw imaginary circuits for a logo.

The average person sees the circles and lines and does not know the difference. A trained designer spots the flaws in a heartbeat. That goes beyond the artistic rendering and down into the nuances of memory routing or even chaining a bunch of guitar effects together to create a sound I hear inside my head. I'm looking beyond the wires and connectors to think inside the box. That's how a PCB designer sees the world.

planes transforms the PCB into a bunch of free capacitors. These signal integrity and power integrity rules are there for the circuit performance reasons listed above but also to quell emission of spurious radiation. Solid design practices help bust EMI and RFI problems.

We are also drilled to keep inductive loops small when we

place and route bypass caps. We are told to use multiple vias

for power and ground planes. Alternating power and ground

Reducing crosstalk reduces power consumption. Making noise takes energy, so suppressing the noise saves power. I mentioned noise suppression is usually an additive process. Each of those resistive, capacitive and inductive elements has its own parasitic effects. It's like adding cream and sugar to make the coffee less bitter. At a certain point, we lose the flavor of the coffee and need a stronger brew.

An elegant layout that accounts for potential energy transfer does not require as much cream and sugar on top of the essential circuits. The ground net plays a huge role. It's the most interesting net on the board. Vias are the one element that prevents the ground net from taking on a charge from the other

### The 5G Rollout Should be Flying High – Literally

Affordable and accessible technologies are the key to global progress.

MY SMARTPHONE DOES everything so well I hardly use my tablet or laptop at all. It contains all the apps I need to use every day, is always with me and always connected, and the clarity of the screen makes it a pleasure to handle the majority of computing tasks on this device. I am convinced improvements in display technologies have helped the smartphone become the go-to device for a vast number of daily activities.

To support the best possible experiences in video, photography and gaming, new display technologies continue to emerge to provide seamless, immersive viewing. OLED displays are dominating the smartphone and flat-panel television markets, bringing attributes such as conformability and optical performance, including high contrast ratio with the ability to render true black, which conventional LCDs cannot manage.

But we humans are insatiable by nature. If the color is good, the viewing angle could be a little wider. If the angle is okay, the contrast could be higher. Now, another change is in progress with the arrival of mini-LED backlit LCDs. Containing many thousands of individual mini-LED emitters less than 0.2mm in size, the backlight has many dimmable zones and permits deep black levels, high contrast ratio and high luminance.

The prevalence of bright, high-resolution and colorful displays almost everywhere we look is another example of the way our technologies are constantly adapted to deliver better experiences and improve the quality of life for large numbers of people.

Technologies are usually expensive when launched, and often aimed at a relatively small and select market. They almost always evolve to become affordable and accessible for the masses. A combination of mature technologies and processes have been combined with new techniques to enable affordable mini-LED displays. We can expect further development of mini-LED displays to reduce the number of components and simplify control, improving both viewing performance and affordability. And we expect high-performing substrate materials with suitable dielectric and mechanical properties, as well as special optical microstructures, to be available for high-volume mini-LED production.

ALUN MORGAN is technology ambassador at Ventec International Group (ventec-group. com); alun.morgan@ ventec-europe.com.

The optical microstructures also make these materials ideal substrates in horticultural lighting for applications such as indoor farming, also called vertical farming. As populations around the world continue to urbanize, growing fresh produce inside buildings such as multi-level warehouses can enhance efficiency in the food supply chain while saving costs and environmental burdens associated with food transportation. Spectrally tuned to the red and blue wavelengths that maximize photosynthesis for faster growing, horticultural LED lighting earns vertical farms the nickname "pinkhouses." Some indoor farmers believe the growth is as much as 20% faster with tuned LED lighting. Generating only photosynthetically useful photons also minimizes energy consumption. Other advanced technologies such as automation of crop care and harvesting are also being employed, helping indoor farming become cost-effective, profitable, and environmentally beneficial.

Our industry continues to come up with great ideas to improve our lives. I am intrigued by the Loon project, initially launched by Google, which promises to greatly democratize access to high-speed Internet by providing flexible 4G and 5G access. Loon - so called because the idea seemed crazy at first - puts 4G base stations in the sky, mounted on-board large balloons at stratospheric altitudes to avoid weather and commercial aviation. They have been successfully connected to commercial mobile networks, and agreements have been established to start services in various locations in South America and Africa. It's an ideal solution for places beset with logistical and technical challenges and could help prevent large numbers of people becoming left behind as the digital and information revolutions gather pace in the developed world.

It's not the only "flying infrastructure" concept out there. A fleet of drones has recently been proposed to provide 5G coverage for the UK. Apparently 60 units is enough to cover the entire country, each providing hundreds of steerable beams from a 3 m. antenna, at less than the cost to install conventional infrastructure. Their hydrogen-fueled motors eliminate emissions worries associated with keeping the drones airborne, and each drone will fly for several days at a time. Like the Loon balloons, they are designed to operate at stratospheric altitudes to avoid interfering with commercial aircraft.

I've mentioned in previous columns that 5G rollout to rural areas could take some time using conventional base stations. Using drones or balloons to provide access from the sky may offer a faster solution.

Another advantage of flying base stations like these is they can be set up quickly in disaster zones, provided the necessary supporting infrastructure is in place. The base stations can bypass access and power supply problems close to the affected area, enabling

continued on pg. 31

### **Etch Effects Explained**

The impedance implications of the trapezoidal trace.

UNTIL RECENTLY I thought those who believed in rectangular traces were about as common as those who believe in square waves and a flat earth. Recently, though, I came to realize it's not as clear as I thought, not only for newbies but in general. Over the past 25 years, I've acquired a good number of books on PCB design and signal integrity, and you wouldn't know from reading most of the industry literature that traces were anything but rectangular. Interesting, right?

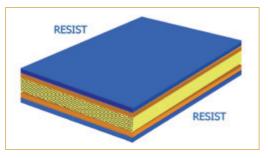

If you've read previous "Material Matters" columns, you may recognize the following cross-section from our Z-solver software. Among other things, it shows that the base of a trace, facing the core dielectric, is wider than the side of the trace that faces the prepreg. As such, the trace trapezoids face both up and down in a multilayer stackup. There's no relationship to the layer number or whether the trace is on the top or bottom half of the board. For this reason, some including me – but not everyone – avoid using terms like "top" or "bottom" with regard to trapezoidal traces.

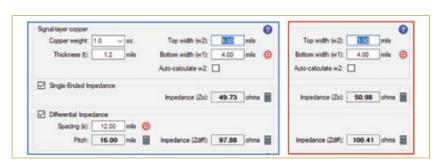

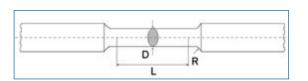

In the dimensions shown in **FIGURE 1**, the w1 value at the base of the trapezoid is the value hardware teams and fabricators exchange when talking about trace

widths and spacing(s). It's important to know that actual fabricated boards won't have quite that much copper. As traces are etched from top to bottom, the etching chemical ("etchant") remains in contact with the prepreg side of the trace longer than the core side. This makes the prepreg side of the trace narrower than the core side and gives the trace a trapezoidal cross-section. In this column we'll discuss the reasons for this fabrication phenomenon and the implications for impedance.

Innerlayer etching. Etching innerlayers involves cleaning the copper on both sides of the laminate, applying a photoresist, exposing the photoresist to create the innerlayer pattern, developing the resist, etching away the unwanted copper, and removing the etch resist. This process is automated in most shops, and the chemistry is automatically monitored. As a result, the accuracy and repeatability is quite good. Using this process, it is possible to etch innerlayer traces to an accuracy of  $\pm 0.5$  mils. This accuracy control helps keep impedance within the tolerances required for transmission lines.

After cores are cleaned, **FIGURE 2** shows a blue light-sensitive film or photoimageable "resist" that is applied by heat and pressure to the metal surfaces of the core. The film is sensitive to ultraviolet light. If you ever tour a fab shop, the room where photoresist is handled uses "yellow light" to prevent inadvertent exposure of the resist. The filters remove the wavelength of light that would affect the resist coating.

The Gerber, IPC-2581 or ODB++ data for the part are used to plot film that depicts the traces and pads of the board design. The phototools or artwork include the copper features. This film is used to place an image on the resist.

Innerlayer film is a "negative" image of the copper features, meaning the copper patterns left behind

> after processing the core correspond to the transparent areas on the film. Core panels are exposed to high-intensity UV light that serves to harden or "polymerize" the film resist, creating an image of the circuit pattern, similar to a slidenegative and a photograph.

The exposed core is then processed through a chemical "developer" that removes the resist from areas that were not hardened by the UV light. Next, the copper is chemically etched from the core in all areas not covered by the remaining blue dry-film resist. After etching, the developed dry-film resist is chemically removed from the panel, leaving just the copper features exposed on the panel.

It's even more nuanced than we've alluded to so

BILL HARGIN has more than 20 years' experience in PCB design software and materials. He is director of everything at Z-zero (z-zero.com); billh@z-zero.com.

PLANE Prepreg Dielectric2 (Dk2, Df2) h2 Resin (Dk7, Dfr) h1 Core Dielectric1 (Dk1, Df1) PLANE

FIGURE 1. The trapezoidal shape of innerlayer traces, shown in a stripline cross-section, where w2 is narrower than w1. (Image from Z-zero's Z-solver software)

**FIGURE 2.** Blue resist film is placed on both sides of an innerlayer core prior to imaging, UV exposure, and subsequent etching.

# Are you getting to the bottom of your via?

Prevent connection failures in thick PCB substrates with plasma treatment

New **VIA<sup>™</sup> Series 2.5** cleans deep, narrow vias where other processes can't go

Contact us now to learn more +1-925-827-1240 / info@nordsonmarch.com

nordsonmarch.com

VIA<sup>™</sup> Series 2.5 Plasma System

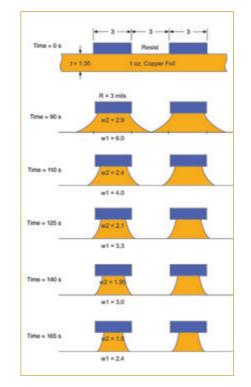

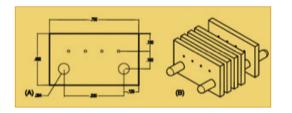

far. As **FIGURE 3** shows, the actual sides of a trace are curved, and an etching "undercut" is below the blue resist. Remember w1 is the dimension hardware teams and fabricators use to describe trace widths. R is the width of the resist the fabricator uses. And the ledge under the resist is the undercut, *u*. Ideally, R, w2 and w1 are equal. The closer a fabricator can get to this, the better, and good fabricators work hard to achieve this.

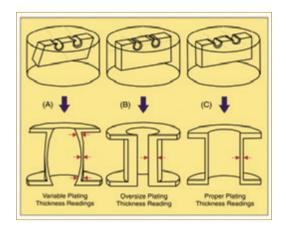

The gap between resist areas is removed evenly at first and then in a progressively cup-shaped fashion until the center area between traces is broken through to the exposed core dielectric, which opens progressively as the etchant goes to work in and under the resist as the side wall is gradually removed through increased exposure. The amount of time the copper is exposed to the etchant determines the final shape of the copper features, as illustrated in **FIGURE 4**.

A resist width (R) equal to the base of the trapezoid (w1) is ideal etching. In Figure 4, this corresponds to the 140 sec. etching scenario. Note too that if R is less than w1, as in the cases up to 125 sec., the copper features or traces are underetched. In the case where the copper is exposed to the etchant for 165 sec., the copper is overetched. The times here are for this specific example, where cupric chloride was used as an etchant, targeting 3.0-mil line and space patterns, using 1.0-mil resist on 1-oz (1.35-mil) copper foil.

Etch factor. From the parameters in Figure 3, there are two descriptive measures of the etching process: undercutting and etch factor. Undercutting is well-defined. It's the average overhang of resist after top width reduction. Hardware teams don't really need to worry about the width of the resist, but the "undercut" term and concept are useful. Obviously, the goal is to minimize the *u* parameter.

$$Undercut(u) = \frac{R - w2}{2}$$

"Etch factor" is quite a bit murkier. Some define it as being proportional

to copper thickness, t, and inversely related to the difference between w1 and w2, the width difference in the trapezoid. But depending on whom you talk to, these relationships may be inverted or use different parameters.

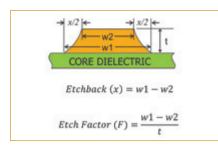

I find the relationship shown in FIGURE 5 intuitive. It

x ("etchback") is the difference between w1 and w2, and "etch factor" is defined as the degree of etchback per thickness.

Fabricator data. Average suppliers typically maintain roughly 0.25 mils of etchback for 0.5-oz. copper and 0.5 mils of etchback for 1-oz. copper, respectively. Advanced PCB manufac-

would be nice if we could agree on a definition like this, where

turers can bring these numbers to 0.17 mils for 0.5-oz. copper and 0.45 mils for 1-oz. copper.

I could be talked into changing the practice, but to avoid getting the complications of conflicting definitions, I've worked in percentages, specifically the ratio between w2 and w1 (with the goal to get as close as possible to 1.0).

Using this approach, advanced PCB manufacturers might achieve w2/w1 of 0.972, for example, for 0.5-oz. copper. Similarly, research shows advanced manufacturers can achieve w2/w1 of 0.925. The limitation with this approach is that it presumes a specific value for w1: in this case, 6 mils.