# PRINTED CIRCUIT pcdandf.com Circuitsassembly.com January 2026

CIRCUITS ASSEMBLY

# BATTLE OF THE CONTINUES

Why Every Stencil Needs a Nanocoating

Designing the PCB Stackup Solving Heat at the PCB Level Exactly What is Ultra HDI? The Electronics Industry's East Coast Conference and Exhibition

Conference: April 28 - May 1 Exhibition: Wednesday, April 29

**DCU Convention Center, Worcester, MA**

F P<sub>o</sub>G A colocated with HOR|ZONS BEYOND GATE ARRAYS

Brought to you by

pcbeast.com

The Electronics Industry's East Coast Conference and Exhibition

# Exhibition: Wednesday, April 29 Conference: April 28 – May 1

DCU Convention Center Worcester, MA

#### WHO'S EXHIBITING (to date)

**Accurate Circuit Engineering**

**Adiuvo Engineering**

All Flex Solutions, Inc.

**AMD**

**American Computer**

Development, Inc. (ACDi)

**ASC Sunstone Circuits**

**BittWare**

Blue Pearl Solutions, Inc.

Breadboard

Cofactr

DirectPCB

**Efinix**

Electronic Interconnect

Eleprint S.R.L.

**EMA Design Automation**

EMX US Inc.

**ESPEC North America Inc**

Fineline Global

Flexible Circuit Technologies

Freedom CAD Services, Inc.

Glory Faith Electronics Co., Ltd.

**GS Swiss PCB**

InstaDeep

JBC Tools USA Inc.

JS Circuit

**K2** Engineering Services

**Lattice Semiconductor**

Microchip Technology Inc.

Millenium Circuits Limited

**NCAB** Group

Newgrange Design

OKI Circuit Technology Co., Ltd.

PalPilot International Corp.

PCB Technologies USA, Inc.

**PCBWay**

Photonics Systems USA Inc.

Polar Instruments, Inc.

Polyonics Inc.

**Precision Circuit Technologies**

Printed Circuit Engineering Assoc. (PCEA)

Quantic Ohmega-Ticer

RBB

Samtec

**Screaming Circuits**

Sierra Circuits

**Suntech Circuits**

Trylene Inc.

T-Tech, Inc.

XJTAG

Zenode

### **SIEMENS**

Start where you need. Scale when you're ready. The Xpedition family grows with you.

**Xpedition** Xpeditio<u>n</u> **Enterprise Standard PADS Pro Essentials ACCESSIBILITY** SCALABILITY PERFORMANCE

# Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

#### Measuring Made Easy®

www.fischer-technology.com | info@fischer-technology.com | 860.683.0781

#### FIRST PERSON

#### THE ROUTE

When the grid fails.

Mike Buetow

#### MONEY MATTERS

#### ROI

The AI hype has uncomfortable echoes.

**Peter Bigelow**

#### **FOCUS ON BUSINESS**

In the hiring game, we all misfire sometimes.

Jake Kulp

#### **TECH TALK**

#### **DESIGNER'S NOTEBOOK**

The design review.

John Burkhert, Jr.

#### **BOARD TALK**

Solving heat at the PCB level. **Jeffrey Beauchamp**

#### **DATA TRANSFER**

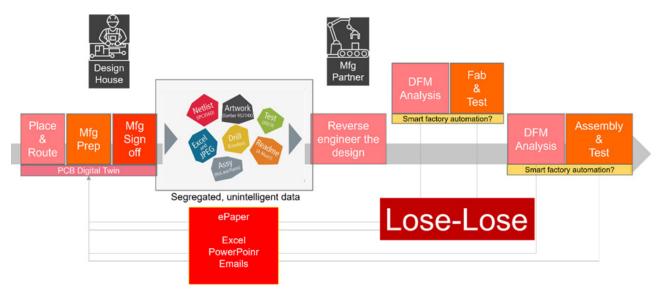

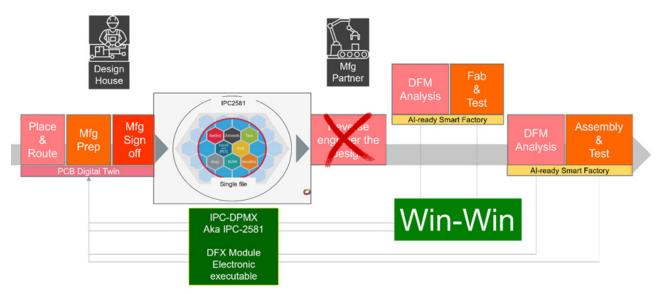

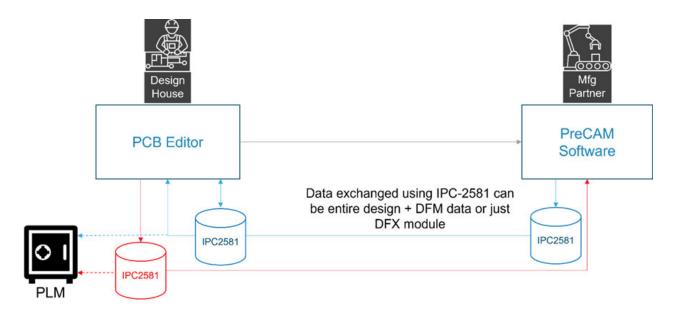

Streamlining DfM feedback. Hemant Shah

#### **MATERIAL GAINS**

What will happen when AI slows? Alun Morgan

#### **GETTING LEAN**

From QC to QA.

Alvaro Grado

**TECHNICAL ABSTRACTS**

#### **DEPARTMENTS**

**AROUND THE WORLD**

**PCEA CURRENT EVENTS**

**MARKET WATCH**

**OFF THE SHELF**

# PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

#### **FEATURES**

#### **UHDI FOUNDATIONS**

#### Ultra HDI: What is It and How is It Different than HDI?

It's not "smaller HDI" but rather a different approach to manufacturing the copper structures themselves, which matters for designs with very fine-pitch BGAs, dense routing channels or demanding RF and high-speed nets. by ANAYA VARDYA

#### **STACKUP ESSENTIALS**

#### The Critical Nature of PCB Stackup, and How to Build an Efficient One

Proper circuit design can be undone by a poorly planned stackup. The construction of a board and the impact of taking a considered approach.

by AKBER ROY

#### **MARKETPLACE MECHANICS**

#### The Marketplace for Misfit Chips

A new platform offers a conduit between companies with excess inventory and the buyers who need them.

by RYANN HOWARD

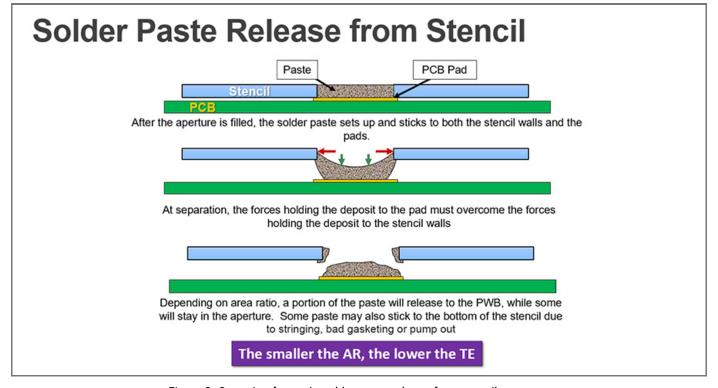

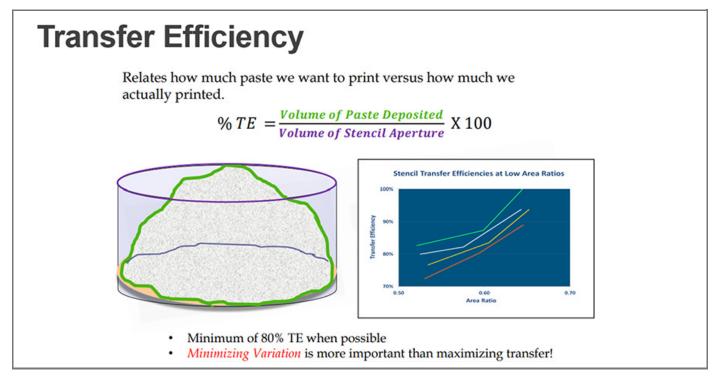

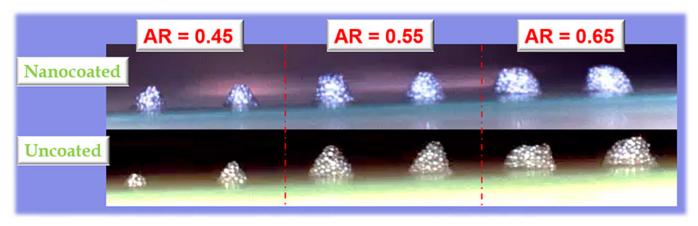

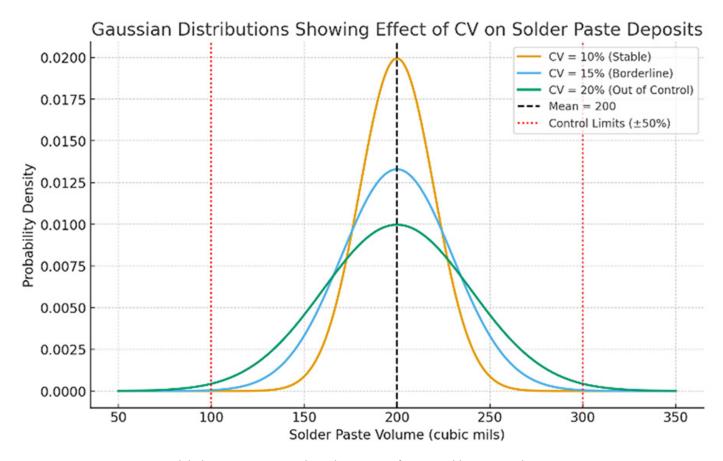

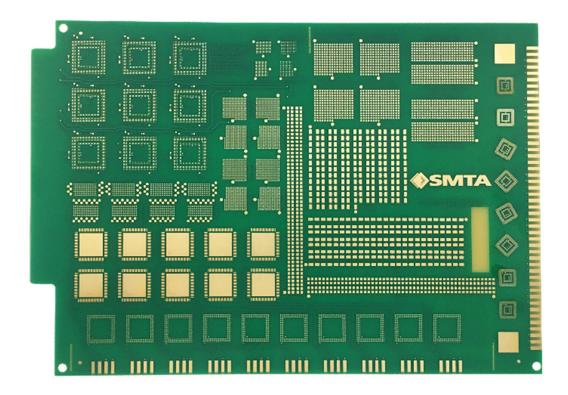

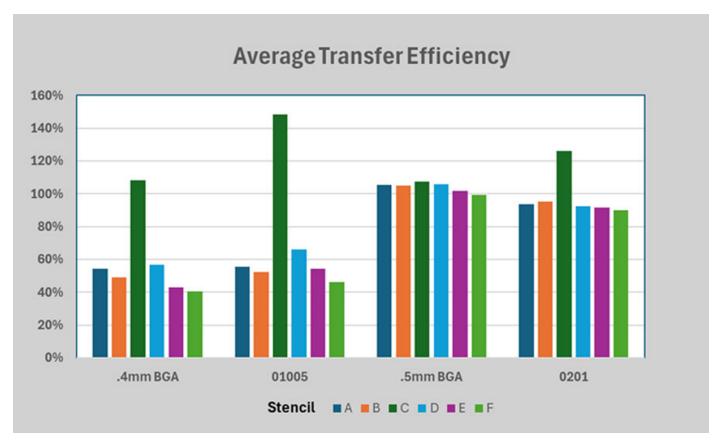

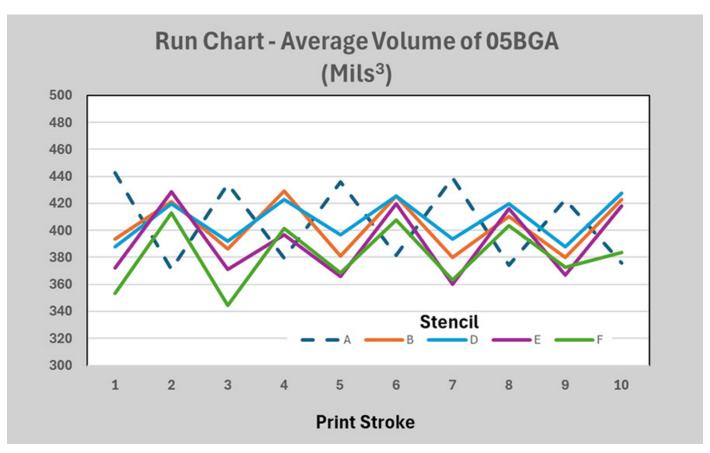

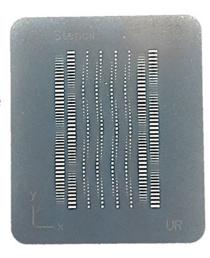

#### STENCIL PERFORMANCE (COVER STORY)

#### A Comparison of Stencil Capabilities

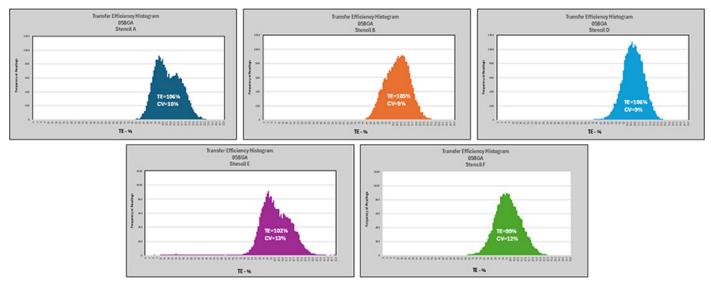

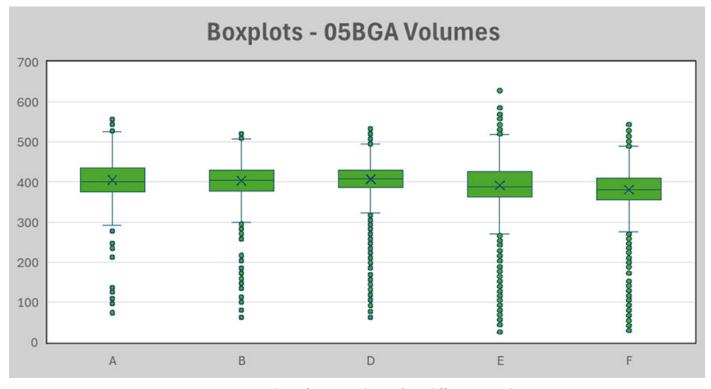

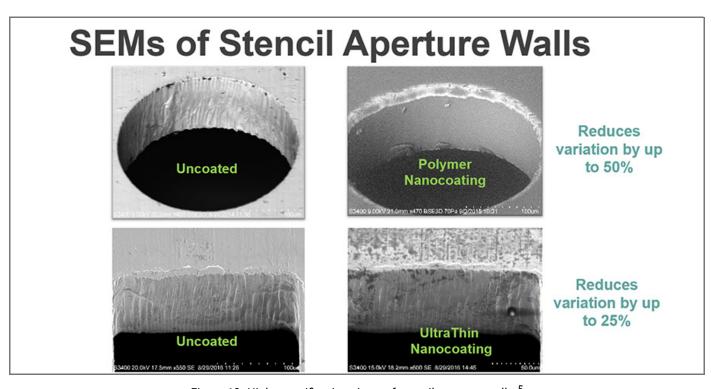

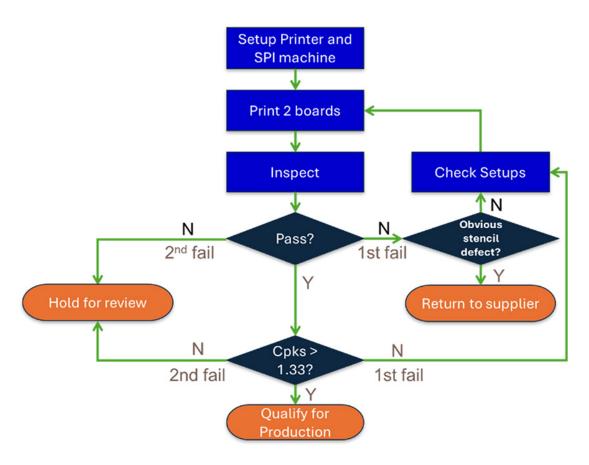

How do modern stencil materials and coatings influence transfer efficiency and volume repeatability as SMT features continue to shrink? by CHRYS SHEA

#### ON PCB CHAT (PCBCHAT.COM)

#### **WORKING WITH CONTRACT MANUFACTURERS**

with RAYMOND NOVARA

#### A RELIABILITY MATTERS PODCAST YEAR-END REFLECTION

with MIKE KONRAD

#### HOW TO WORK EFFECTIVELY WITH YOUR CM

with DANIEL STANPHILL and SEAN KINCAID

# Built for change.

The world is constantly changing. Now faster than ever. From rapid tech shifts to climate pressure. From geopolitical uncertainty to new production methods. Today, stability comes from agility. That means having a supply chain that can adapt to your needs - fast. And PCB production is no exception.

**NCAB** is built for change. For over 30 years, we have been producing PCBs and taking full responsibility — without owning any factories. Instead, we constantly source, qualify and develop the most optimal ones across three continents. And we only use them where they excel.

**In other words:** You will always have more than one option for your PCB production. So when things change, you can too. Fast.

Reliable PCBs. Resilient supply chain.

PCEA PO BOX 807 AMESBURY, MA 01913

# PRINTED CIRCUIT DESIGN & FAB pcdandf.com circuitsassembly.com

#### **PCEA BOARD OF DIRECTORS**

Stephen Chavez, CHAIRMAN Susy Webb, VICE CHAIRMAN Justin Fleming, SECRETARY Anaya Vardya, TREASURER

#### **MEMBERS**

Jim Barnes

Michael Buetow

Tomas Chester

Douglas Dixon

Juan Frias

Richard Hartley

Matthew Leary

Charlene McCauley

Eriko Yamato

#### **PCEA.NET**

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

| PCD&F/Circuits Assembly    | digital.pcea.net             |

|----------------------------|------------------------------|

| WEBSITES                   |                              |

| PCD&F                      | pcdandf.com                  |

| Circuits Assembly          | circuitsassembly.com         |

| NEWSLETTER                 |                              |

| PCB Update                 | pcbupdate.com                |

| PODCASTS                   |                              |

| PCB Chat                   | pcbchat.com                  |

| EVENTS                     |                              |

| PCB West                   | pcbwest.com                  |

| PCB East                   | pcbeast.com                  |

| PCB Detroit                | pcea.net/pcb-detroit         |

| EDUCATION                  |                              |

| PCB2Day                    | pcb2day.com                  |

| PCEA Training              | pceatraining.net             |

| Printed Circuit University | printedcircuituniversity.com |

| AWARDS PROGRAMS            |                              |

| Service Excellence Awards  | circuitsassembly.com         |

| NPI Awards                 | pcea.net/npi-award           |

PCB Prote

#### MANAGEMENT

PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net VICE PRESIDENT, SALES & MARKETING Frances Stewart 770-361-7826 | frances@pcea.net

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

MANAGING EDITOR

Ryann Howard 912-803-9780 | ryann@pcea.net

#### **COLUMNISTS AND ADVISORS**

Jeffrey Beauchamp, Peter Bigelow, Robert Boguski, John Burkhert, Jr., Stephen Chavez, Mark Finstad, Geoffrey Hazelett, Nick Koop, Jake Kulp, Alun Morgan, Susan Mucha, Greg Papandrew, Chrys Shea, Jan Vardaman, Gene Weiner

#### **PRODUCTION**

ART DIRECTOR & PRODUCTION

blueprint4MARKETING, Inc. | production@pcea.net Nathan Hoeller | nathan@pcea.net

#### SALES

VICE PRESIDENT, SALES & MARKETING

Frances Stewart 770-361-7826 | frances@pcea.net

SENIOR SALES EXECUTIVE

Will Bruwer 404-313-1539 | will@pcea.net

#### REPRINTS

sales@pcea.net

#### **EVENTS/TRADE SHOWS**

**EXHIBIT SALES**

Frances Stewart 770-361-7826 | frances@pcea.net

TECHNICAL CONFERENCE

Mike Buetow 617-327-4702 | mike@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuits assembly. com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2026, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/ CIRCUITS ASSEMBLY is forbidden without written permission.

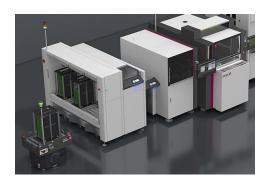

# Small. Powerful. Efficient.

Reduce selective soldering floor space usage by up to 60% with SELECT Synchro and scale your production floor's potential.

# What will you do with all that floor space?

## When the Robots Stop: From San Francisco, a Cautionary Tale

MANY YEARS AGO, in *The Dark Knight*, Batman's nemesis the Joker famously observed that nobody panics when things go "according to plan – even if the plan is horrifying." It's when the unexpected happens that chaos erupts.

San Francisco got a taste of that chaos in late December when a power outage brought the city's fleet of Waymo autonomous vehicles to a standstill. For hours, the self-driving cars sat motionless at darkened intersections, hazard lights blinking, blocking traffic and stranding frustrated drivers. Social media lit up with videos of the gridlock. Tow trucks worked overtime. And the ride-hailing service that had been touting its superior safety record was forced offline.

Let's be clear: Waymo's safety statistics are impressive. According to the company, its autonomous vehicles have 90% fewer serious injury crashes, 82% fewer airbag deployments and 81% fewer injury-causing incidents compared to human drivers over the same distance. Dr. Jonathan Slotkin, a Pennsylvania neurosurgeon and trauma specialist who analyzed Waymo's data, suggests that if just 30% of cars were fully automated, we might prevent 40% of crashes. That's a compelling case for autonomous vehicles.

Except when the power goes out.

The malfunctions are especially puzzling because these vehicles are specifically designed to handle lost connectivity and dead traffic signals. Poor weather on occasion knocks out traffic lights in San Francisco without causing problems. The cars run on onboard batteries and are engineered to operate in areas where wireless signals drop.

Yet they did. Or at least, they relied on something that failed when the grid went dark.

Waymo explained that while its vehicles treat nonfunctional signals as four-way stops, "the sheer scale of the outage led to instances where vehicles remained stationary longer than usual to confirm the state of the affected intersections." Translation: the system got overwhelmed and froze.

The irony is, remote facilitation may be more critical to safe operation than we know. Some autonomous vehicle companies employ remote technicians who help these cars navigate situations they can't solve independently. To wit, Tesla's Robotaxis, which have onboard remote assistance monitored by humans, reportedly operated without problems during the same outage. That's worth noting.

In the electronics industry, we understand redundancy, fault tolerance and graceful degradation. We design systems

expecting failures. But public infrastructure – and that's what these vehicles have become – requires the highest standard. When you're transporting people, blocking intersections and potentially impeding emergency services, "system bugs and failures" aren't acceptable.

No injuries or accidents resulted from the Waymo outages, which is fortunate. But the company has previously issued recalls after software malfunctions caused vehicles to collide with a pickup truck and a telephone pole in Phoenix. The pattern suggests that edge cases and unexpected scenarios remain significant challenges.

If you are thinking it's unusual for electronics and public health to intersect so dramatically, you are not alone. The fundamental question remains: Are these systems truly ready for widespread deployment?

Dr. Slotkin's assessment is that it's in the public's best interests to make the transition to autonomous vehicles, because even with the potential for mistakes the robots are less error-prone than humans.

But December's power outage revealed something important: when systems fail – which eventually they all do – autonomous vehicles can create new problems even as they solve old ones. The technology may be 90% safer in normal conditions, but what happens in abnormal conditions matters too. It's up to all of us to decide just how much.

By the next afternoon, San Francisco streets returned to normal, aside from the conspicuous absence of Waymos. When service resumed, users were still greeted with: "Our service is currently paused. We're sorry for the inconvenience – please check back again soon."

The inconvenience passed. The questions remain.

The Joker was right about one thing: it's the unexpected that causes panic. If autonomous vehicles are going to share our streets, they need to be ready to handle the chaos. And so must we.

mike@pcea.net @mikebuetow

P.S. Registration for PCB East opens later this month. Be sure to check out the full slate of offerings this year: technical conferences for design and fabrication, plus three dedicated assembly tracks, including an all-day hand soldering workshop! Plus, the PCB Management Forum and the FPGA Horizons conference. All of this wraps around the one-day exhibition on April 29, featuring more than 80 companies, including AMD, Microchip, Samtec and the leading PCB EDA software vendors. Hope to see you there.

MIKE BUETOW is president of PCEA (pcea.net); mike@pcea.net.

### LEADER TAPE EXTENDERS

Boost Efficiency with TapeSplice® Leader Tape Extenders

500 pieces per box

TapeSplice® Leader Tape Extenders provide a strong, gap-free connection between feeder and carrier tape for smooth, reliable, and continuous production.

Strong, Reliable Bond:

Prevents tape jams and misfeeds

Time-Saving:

Reduces feeder setup interruptions

**Color Options:**

Easy line organization

## Quilter Al Tool Lays Out Complete Computer Design in Less than Week, Company Says

LOS ANGELES – Quilter in December announced the creation of a printed circuit board design for a computer using artificial intelligence tools in under a week.

The startup company, founded in 2019 by former SpaceX engineer Sergiy Nesterenko, said a single engineer completed the layout taking a schematic to manufacturing-ready files in less than a week, a process that traditionally takes an entire engineering team months and requires multiple rounds of redesign. This initiative, called Project Speedrun, represents a major milestone for the hardware industry, demonstrating an ability to compress quarter-long hardware R&D cycles into rapid weekly experiments.

Project Speedrun based its computer design around the widely used NXP i.MX 8M Mini processor, the same embedded computing hardware commonly used in automotive infotainment, safety and machine-vision systems. The system was fully functional upon first boot, capable of handling the demands of video calls, video games and more – a rare outcome in printed circuit board design, where projects typically build in as many as 3-5 respins when scoping.

Professional PCB designers quoted 428 hours of manual labor to create the same two-board system that Project Speedrun would produce; 238 hours for the baseboard and 190 hours for the system-on-module (SOM). With Quilter, 98% of the placement, routing and physics validation was completed autonomously in 27 hours. A single engineer required 12 hours to clean up the baseboard and 26.5 hours to clean up the SOM, which represents an 11x acceleration overall and a peak of 20x improvement on the baseboard.

Quilter works by using physics-driven reinforcement learning to explore manufacturable board layouts. Instead of placing hundreds of components and routing thousands of traces manually, engineers simply submit a schematic and let the AI generate multiple physics-tested designs to choose from.

"We see this as the compiler moment for hardware," said Nesterenko. "What used to take a team months now happens in days, which means you reach market months, if not a year, ahead of competitors. That's how hardware will be built from now on."

Tony Fadell, an investor in Quilter, founder of Nest and a codeveloper of the iPod and iPhone, commented, "Everyone in hardware knows that the best PCBs are still designed by humans, track by track, over weeks of painstaking work. Quilter blows that bottleneck apart. It's a complete paradigm shift. When you iterate faster, you can out-innovate your competitors."

Quilter integrates with Altium, Cadence and Siemens Xpedition, and runs natively on private cloud and GovCloud.

#### Guangzhou Guanghe Technology Files for Hong Kong IPO

HONG KONG, CHINA – Guangzhou Guanghe Technology has submitted its prospectus to the Hong Kong Stock Exchange, seeking a main-board listing with CITIC Securities and HSBC acting as joint sponsors.

According to its prospectus and third-party data from Frost & Sullivan, Guanghe ranked third globally and first among China-headquartered manufacturers by cumulative revenue from computing server PCBs between 2022 and 2024. Server-related products now account for more than 70% of total revenue, reflecting strong demand tied to AI workloads, data center expansion and high-performance computing.

The company operates major manufacturing bases in Guangdong and Hubei provinces and supplies both OEM customers and electronics manufacturing services providers through a direct sales model.

# US-China Economic & Security Review Commission Highlights Need for AmericanMade PCBs

WASHINGTON – The US-China Economic and Security Review Commission has released its 2025 Report to Congress, warning that decades of offshoring PCB manufacturing have sharply eroded domestic capacity. According to the report, US PCB production in output value has fallen from roughly 30% of global supply in 2000 to just 4% today.

The Commission emphasized that semiconductors used in national defense, critical infrastructure and commercial systems all rely on PCBs as their foundational platform. It flagged US dependence on foreign suppliers, particularly China, which now accounts for approximately 60% of global PCB production, as a strategic vulnerability.

While current US defense needs are still supported by domestic manufacturers, the report noted that defense demand alone is insufficient to sustain a modern PCB industrial base. As a result, the United States lacks the capacity to scale production rapidly in response to national or economic security needs.

"We agree with the Commission's finding that Congress should create or expand industrial policy tools, including grants, loans, loan guarantees, advanced manufacturing tax credits and a dedicated industrial finance entity, to rebuild domestic capacity, modernize equipment, and support the US workforce," said David Schild, executive director of the Printed Circuit Board Association of America.

Schild added that the association is backing H.R. 3597, the Protecting Circuit Boards and Substrates (PCBS) Act, which aligns closely with the Commission's recommendations. "We encourage members of Congress to co-sponsor this important legislation, which would help revitalize the US PCB industry and reduce risks to national and economic security," he said.

## Looming Substrate and Materials Shortages for Advanced Packaging, TechSearch Warns

AUSTIN, TX – Rapid growth in AI servers and data center hardware will push substrate demand beyond available capacity by 2028, forcing manufacturers to expand production within the next three years, according to a recent report from TechSearch International.

Advanced Packaging Update highlights rising pressure on substrate materials – especially glass fiber used in core constructions – and evaluates potential alternatives as supply tightens.

The analysis also compares projected high-bandwidth memory (HBM) demand against planned capacity, noting widening gaps as AI accelerators scale. A dedicated section examines hybrid bonding adoption, equipment requirements, and competing fine-pitch interconnect approaches now entering development.

#### Foxconn to Invest \$170M to Build Electronics Manufacturing Plant in Louisville

LOUSIVILLE, KY – Foxconn in December confirmed plans to establish a US production hub in Louisville, announcing a \$170 million investment that will bring 180 new jobs to the region. The project is being supported by Kentucky Economic Development Finance Authority incentives for the company.

The company expects production to begin in the third quarter of next year.

Foxconn plans a new \$170 million electronics manufacturing plant in Louisville.

the facility will produce a well-known consumer product for a well-known brand, though further details were not disclosed. During the announcement, a global operations map labeled the Louisville site as "Kentucky Assembly – TV/Display," hinting at potential product categories.

Local officials said the project signals renewed momentum for US-based electronics manufacturing.

Foxconn has a long history of announcing major investment programs in the US, only to back away, however. Over the past decade, new plants in Wisconsin, Pennsylvania and other states have been announced, only to fail to materialize as planned – or at all.

## Incap Buys Lacon in \$54M Deal, Expands Defense and Design Services

HELSINKI – Incap has signed an agreement to acquire 100% of Germany's Lacon Group in a transaction valued at \$54.2 million, marking an expansion of the Finnish EMS provider's presence in Europe and growing its position in fast-growing defense and industrial markets.

Lacon Group operates EMS and ODM facilities in Germany and Romania totaling roughly 21,300m<sup>2</sup>. Its offering includes PCB assembly, cable harnessing, box build, system integration and design and testing services, which are capabilities that expand Incap's scope beyond manufacturing and into full product-development support. For the first 10 months of 2025, Lacon reported unaudited revenue of \$61.8 million.

The purchase price will be paid in cash and funded through Incap's own reserves and a bank loan of about \$32.5 million. An additional earn-out of up to \$5.4 million may be paid in 2027 based on Lacon's 2026 financial performance. Closing is expected in the first quarter of 2026 pending foreign-investment approvals in Germany and Romania.

Incap expects the acquisition to increase revenue in 2026 and have a slightly positive effect on operating profit after accounting for integration and purchase-price allocation costs. The deal also gives Incap a larger foothold in the DACH region and adds more than 600 employees, bringing the combined organization to over 3,000 employees across Europe, Asia and North America.

#### Micro-Precision Technologies Acquires Stellar Manufacturing

SALEM, NH – Micro-Precision Technologies has acquired Stellar Manufacturing, adding PCB assembly capabilities to its US microelectronics platform. The deal, which closed in early October, builds on MPT's partnership with Great River Capital Partners and supports its expansion across defense, aerospace, medical and commercial markets.

Stellar's Salem, NH, operation will continue serving customers. MPT said the acquisition combines Stellar's PCBA expertise with its own hybrid, multichip module and thick-film technologies.

#### PCD&F

**AGY** will invest \$12 million to expand specialty glass fiber production at its Aiken County, SC, facility, adding 80 jobs and increasing capacity for materials used in semiconductor packaging and high-performance printed circuit boards. Operations are expected to begin in early 2026.

Calumet Electronics installed a Schmid Infinity H+ developer.

**Celus** announced electronic component supplier **AGS Devices** has officially gone "live" with the Celus Design Platform, an Al-assisted electronics design platform.

**Doosan Electro-Materials** is reportedly positioned to become the sole CCL supplier for **Nvidia's** upcoming Rubin AI platform.

**Ecarx** has partnered with **Victory Giant Technology** to scale production of high-performance automotive computing platforms.

**KKR** has reportedly become the main contender for the acquisition of assets of **Taiyo Holdings**, with the intent to privatize the Japanese chemical company.

**Mobius Materials** has closed a \$3 million seed round to expand its authenticated semiconductor spot market.

**Syrma SGS** has started building a PCB facility in Andhra Pradesh, India, to expand domestic production capacity.

**Wipro Electronics** plans to begin operations at its new, \$60 million PCB facility in Doddaballapura, Bengaluru North within the next nine months. **◄**

#### CA

AIM Solder appointed RMG Vietnam authorized distributor in Southeast Asia.

Amber Enterprises India has completed the acquisition of a majority stake in Pune-based Shogini Technoarts.

Coherix opened a new vision center in Sinsheim, Germany.

**Critical Manufacturing** partnered with **Canonical** to expand cloud-native MES deployment options across cloud, hybrid and on-premises manufacturing environments.

**Foxconn** and **Luxshare** plan to expand Vietnam's game console manufacturing capacity by several million units per year as both firms seek permits for large production increases across Northern Vietnam.

**Foxconn** is set to invest NT\$15.9 billion (\$510 million) to develop a new headquarters complex in Kaohsiung, Taiwan. Construction is scheduled to begin in 2027 and completion targeted for 2033.

Giga Computing is partnering with Syrma SGS for a production hub in Tamil Nadu, India.

**Golden Technology** broke ground on its second mobile phone manufacturing facility in Kurdistan.

**GPV** and **East/West Manufacturing** have entered into a strategic partnership whereby the two EMS companies will support each other's production to serve customers in regions affected by trade and domestic manufacturing compliance issues.

**Kitron** secured an \$18.5 million contract to produce advanced electronic components for combat vehicle systems, with deliveries beginning in late 2026, and signed an \$8.3 million agreement with a new customer to produce electronics for autonomous systems across air, land and sea domains for the defense industry.

**Kitron** in December received approval from Swedish competition authorities and the Swedish authority **ISP** to proceed with the acquisition of **Deltanordic**, a deal that was announced on Nov. 19.

Merck Electronics is entering qualification on its \$581 million Kaohsiung materials plant.

NanoFlowX named Bentec representative in Europe and India.

**Nidec Advance Technology** and **Gantu Technology** are codeveloping Al-driven inspection and test solutions for PCBs and advanced semiconductor packaging.

**Safari Circuits** has acquired **Lacroix Electronics**' Grand Rapids, MI, manufacturing plant, preserving 116 PCB assembly jobs.

**Samson** has begun electronics manufacturing at its new Offenbach facility, completing the transition from Frankfurt.

**Scanfil** in December finalized its previously announced acquisition of US-based electronics manufacturer **Adco Circuits**.

Solutions Manufacturing installed a Universal Fuzion pick-and-place machine.

**SynQor**, which designs and manufactures power electronics, will relocate its 250 employees in Massachusetts to Salem, NH.

**Tata Electronics** and **Intel** signed an agreement to explore chip manufacturing, packaging, and AI PC development in India.

**Wistron's** board approved a new, \$135 million investment plan to expand AI server and networking production at its campus in Hsinchu, Vietnam.

### You dream, we deliver.

Design, Engine and Produce, at pcbpro.online

pcbpro.online

# WTT TECHNOLOGIES

**WTT** ELECTRONICS CO., LTD.

REGISTERED CAPITAL

**75**Million USD

HEADCOUNT

1000+ Employee

#### **TECHNICAL FEATURES**

Max. Layer Count: 46

Max. Panel Size: 620\*710mm (24.4\*28")

Max. Board Thickness: 6mm

HDI: 3+N+3, Anylayer

**Back Drilling**

Max. Through Hole Aspect Ratio: 32:1

Max. Laser Via Aspect Ratio: 1:1

Min. Line Width / Spacing: 30/40 µm

POFV / VIPPO

Depth Control Drilling & Milling

High Speed Materials

Heavy Copper up to 8 oz

www.wttpcb.com

#### **PCDF**

Gerrit Steen

Dan Beeker

**Denis Boulanger**

Nancy Smith

Kelly Dack

Jay Gorajia

Steve Robinson

Paul Cooke

AdvancedPCB named Lisa Holmes director of global marketing.

AT&S appointed **Gerrit Steen** chief financial officer.

Blue Origin named Chris Sadler senior PCB designer.

**Dan Beeker** has retired from NXP and has assumed the role of president and CTO at System Solution Specialists.

Draper named **Denis Boulanger** principal engineer DFM PCB/CCA.

Equinox Power Innovations hired Nancy Smith as senior printed circuit board designer.

Kelly Dack joined Pioneer Circuits as senior applications engineer.

Siemens Digital Industries Software promoted **Jay Gorajia** to vice president – professional services and customer support – Lifecycle Management Solutions.

**Steve Robinson**, former president and CEO of APCT, Data Circuit and executive VP at Merix, passed away in December.

Summit Interconnect named Paul Cooke director of engineering.

#### CA

Billy Aldridge

Keith Howell

Tim Filteau

Sascha Brüning

**Andrew Regrut**

Helios Technologies promoted **Billy Aldridge** to president, electronics segment.

Keith Howell, technical director at Nihon Superior USA, passed away in December.

Naprotek appointed Tim Filteau chief executive officer.

Neways named Sascha Brüning vice president defense.

Kimball Electronics promoted **Andrew Regrut**, the company's treasurer and investor relations officer, to lead strategic development efforts.

We are committed to advancing technology through shared knowledge and collective excellence.

# Thank You! PCEA CORPORATE MEMBERS

Collaborate across the electronics industry,

Educate future innovators, and

Inspire a global community of professionals.

# Join Today!

WTT TECHNOLOGIES

### PCB West Booth Space Now Open to Any Exhibitor

PEACHTREE CITY, GA – The exhibition floor for PCB West 2026 is now open to any prospective exhibitor. The exhibit floor is expected to sell out, as it has in 11 of the past 12 years.

PCB West will be held Sept. 29 to Oct. 2, 2026, at the Santa Clara (CA) Convention Center. The event includes a one-day exhibition on Sept. 30.

Booth sales opened in early November to returning exhibitors, and the exhibit floor is currently over 60% sold out.

"PCB West has sold out 11 of the past 12 years, and we fully expect it to do so again," said Frances Stewart, vice president of sales and marketing, PCEA. "Attendance at the show was up 3.5% year-over-year in 2025, and attendees have noted the access to vendors and each other as the primary reasons why they come to PCB West."

Companies interested in exhibiting should contact Stewart at frances@pcea.net for details.

#### PCB East More than 70% Sold Out

PEACHTREE CITY, GA – The exhibition floor space for PCB East 2026 is more than 70% booked and is expected to sell out. The one-day exhibition will be held Apr. 29 at the DCU Center in Worcester, MA, with a four-day conference taking place Apr. 28 – May 1.

"Since its return in 2021, PCB East has sold out each year, and we fully expect it to do so again," said Frances Stewart, vice president of sales and marketing, PCEA. "Attendance at the show was up 15% in 2025, and attendees have noted the access to vendors and each other as the primary reasons why they come to PCB East.

"With the exhibit floor selling out quickly for PCB East, we look forward to another outstanding event for the printed circuit engineering community in 2026."

"Moving PCB East is a major step for the electronics industry's East Coast exhibition and conference," said Mike Buetow, president, PCEA. "The DCU Center is a top-tier venue, and Worcester offers big-city advantages at a more affordable cost to attendees. This change reflects the event's growth and the industry's expanding needs."

Companies interested in exhibiting should contact Frances Stewart at frances@pcea.net for details.

#### Registration for PCB East Conference to Open this Month

PEACHTREE CITY, GA - Registration for the PCB East 2026 conference and exhibition will open this month. PCB East will feature more than 65 hours of design and manufacturing classes, plus another 18 hours of assembly courses during the four days starting in late April.

In addition, this year's event will offer a two-day, two-track conference on FPGA, produced by FPGA Horizons.

The 2026 conference takes place Apr. 28 - May 1 at the DCU Center in suburban Boston.

Among the 33 printed circuit design classes are 20 new to PCB East, including talks on designing high-thermal PCBs, design-time estimation, DfM for UHDI, design for test, and the fundamentals of EMC. Speakers include Rick Hartley, Susy Webb, Stephen Chavez, Tomas Chester and Karen Burnham, among others.

The three-track assembly conference, chaired by Chrys Shea, includes an all-day hands-on soldering class, plus two half-day sessions on circuit assembly. An all-day session on management and supply chain, with a special focus on security, robustness, equipment evaluation and workforce development, rounds out the program.

Leading off the week is a one-day management session, Strategic Leadership in the Age of AI, New Technology Adoption, and Talent Scarcity: Executive Strategies for AI Adoption, Meeting Workforce Challenges, and New PCB Process Selection For Advanced Electronics Packaging, chaired by Gene Weiner and Peter Bigelow and featuring talks on technology implementation, workforce skills training, market conditions and legislative updates will take place on Apr. 28.

More details are forthcoming at pcbeast.com.

#### Spring PCB Design Training Classes Scheduled

PEACHTREE CITY, GA - Registration is open for the next PCEA Training Certified Professional Circuit Designer (CPCD) training and certification classes.

Upcoming sessions are

• Feb. 6, 13, 20, 27, and Mar. 6. Registration closes Jan. 9.

The 40-hour instructor-led course is designed for printed circuit engineers, layout professionals and other individuals currently serving in the design engineering industry or seeking to get into it.

The classes cover the gamut of printed circuit design engineering, from layout, place and route to specifications and materials to manufacturing methods. Schematic capture, signal integrity and EMI/EMC are also part of the comprehensive program.

Each class includes a copy of *Printed Circuit Engineering Professional*, a 400-page handbook on circuit board design, and the optional certification exam recognized by PCEA.

There are no prerequisites to enroll. Classes are held online and led by experienced instructors.

To enroll, visit pceatraining.net/registration.

#### PCEA **CURRENT EVENTS**

#### ASSOCIATION NEWS

**Certification.** The following recently passed the PCEA Certified Printed Circuit Designer exam:

- John Andorf

- Joshua Cruz

- Michael Dauphinai

- Javier Feliciano

- Sean Welch

**Conferences.** PCB Detroit will return to the campus of Wayne State University on Jun. 15-16, 2026. More details will be forthcoming at pcea.net/events.

**Networking.** The PCEA Discord server brings together engineers and designers from around the world on a private channel to discuss technical questions and career opportunities. To join, contact PCEA.

Recent conversations covered the implementation of copper pours, design reviews and low-voltage differential signals.

#### **CHAPTER NEWS**

**Richmond, VA.** Our next in-person meeting is being planned for January, possibly with a presentation on manufacturing tests. Contact Michael Burns for details.

**Portland, OR.** Our next chapter meeting will be held online on Jan. 22. The tentative topic is thermal issues and thermal management. Contact Stephan Schmidt for details.

The Electronics Industry's East Coast Conference and Exhibition

Conference: April 28 - May 1 Exhibition: Wednesday, April 29

**DCU Convention Center, Worcester, MA**

F P<sub>o</sub>G A colocated with HOR|ZONS BEYOND GATE ARRAYS

Brought to you by

pcbeast.com

The Electronics Industry's East Coast Conference and Exhibition

# Exhibition: Wednesday, April 29 Conference: April 28 – May 1

DCU Convention Center Worcester, MA

#### WHO'S EXHIBITING (to date)

**Accurate Circuit Engineering**

**Adiuvo Engineering**

All Flex Solutions, Inc.

**AMD**

**American Computer**

Development, Inc. (ACDi)

**ASC Sunstone Circuits**

**BittWare**

Blue Pearl Solutions, Inc.

Breadboard

Cofactr

DirectPCB

**Efinix**

Electronic Interconnect

Eleprint S.R.L.

**EMA Design Automation**

EMX US Inc.

**ESPEC North America Inc**

Fineline Global

Flexible Circuit Technologies

Freedom CAD Services, Inc.

Glory Faith Electronics Co., Ltd.

**GS Swiss PCB**

InstaDeep

JBC Tools USA Inc.

JS Circuit

**K2** Engineering Services

**Lattice Semiconductor**

Microchip Technology Inc.

Millenium Circuits Limited

**NCAB** Group

Newgrange Design

OKI Circuit Technology Co., Ltd.

PalPilot International Corp.

PCB Technologies USA, Inc.

**PCBWay**

Photonics Systems USA Inc.

Polar Instruments, Inc.

Polyonics Inc.

**Precision Circuit Technologies**

Printed Circuit Engineering Assoc. (PCEA)

Quantic Ohmega-Ticer

RBB

Samtec

**Screaming Circuits**

Sierra Circuits

**Suntech Circuits**

Trylene Inc.

T-Tech, Inc.

XJTAG

Zenode

### Advanced Packaging Market Set to Double by 2034

OTTAWA – The advanced packaging market is poised for explosive growth over the next five years, driven by AI, high-performance computing and the insatiable demand for smaller, faster electronics, a new report asserts.

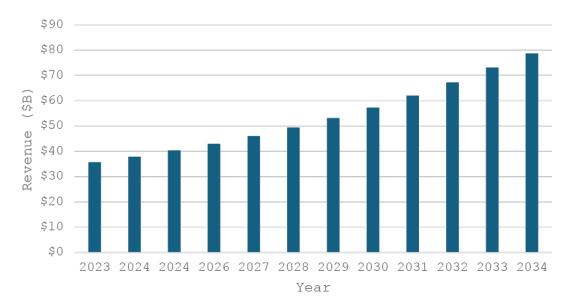

According to new research from Towards Packaging, the global advanced packaging sector will climb to \$78.8 billion by 2034 from \$40.3 billion in 2025 – a compound annual growth rate of 7.6%.

Change in advanced packaging revenue, 2023-34. (Source: Towards Packaging)

And with the growth will come a fundamental shift in how semiconductors are assembled and interconnected, the firm says.

The growth drivers are familiar to anyone tracking the industry: AI accelerators need enormous bandwidth and power efficiency. Data centers are proliferating. Automotive electronics keep getting more complex. And consumer devices? They're demanding performance that can only be delivered through advanced heterogeneous integration.

Fan-out wafer-level packaging is leading the charge, offering superior thermal performance and smaller footprints critical for mobile and wearable applications. But it's the chiplet revolution that's really changing the game. By disaggregating monolithic designs into smaller, specialized dies, manufacturers can mix and match components, boost yields and dramatically reduce costs.

2.5D and 3D packaging technologies continue to mature, with through-silicon vias (TSVs) and interposers enabling the high-bandwidth, low-latency connections that AI and HPC applications require. Meanwhile, system-in-package (SiP) solutions are carving out territory in IoT, wearables and 5G infrastructure by integrating multiple functions into compact modules.

Use of panel-level packaging (PLP), which involves larger panel substrates instead of individual wafers, is rising, which can lower per-unit cost and improve throughput.

North America remains the dominant region, thanks in large part to its strong semiconductor ecosystem, rapid adoption of AI and 5G technologies, and continuous R&D investments.

|                                            | % CHANGE |      |                    |      |  |

|--------------------------------------------|----------|------|--------------------|------|--|

|                                            | JUL.     | AUG. | SEPT. <sup>p</sup> | YTD  |  |

| Computers and electronics products         | 0.2      | -0.2 | -0.1               | 4.9  |  |

| Computers                                  | 1.8      | -1.0 | 1.5                | 14.4 |  |

| Storage devices                            | 6.9      | -0.2 | -5.2               | 9.7  |  |

| Other peripheral equipment                 | 7.3      | -7.6 | -8.4               | 11.5 |  |

| Nondefense communications equipment        | -0.2     | 2.5  | 1.9                | 7.6  |  |

| Defense communications equipment           | -6.9     | -1.9 | -2.4               | -1.0 |  |

| A/V equipment                              | 6.1      | -4.5 | -2.4               | -3.1 |  |

| Components <sup>1</sup>                    | -0.2     | -0.1 | -0.7               | 4.6  |  |

| Nondefense search and navigation equipment | 0.1      | -2.5 | 0.4                | 3.8  |  |

| Defense search and navigation equipment    | -0.7     | -0.6 | 1.1                | 2.3  |  |

| Electromedical, measurement and control    | -0.7     | 0.6  | 0.1                | 4.3  |  |

| Key Components                                                                                                   |        |        |        |        |        |  |  |

|------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--|--|

|                                                                                                                  | JUL.   | AUG.   | SEPT.  | OCT.   | NOV.   |  |  |

| EMS book-to-bill <sup>1,3</sup>                                                                                  | 1.23   | 1.26   | 1.31   | 1.26   |        |  |  |

| Semiconductors <sup>2,3</sup>                                                                                    | 20.6%  | 21.7%  | 15.3%  | 27.2%  |        |  |  |

| PCB book-to-bill <sup>1,3</sup>                                                                                  | 1.00   | 0.98   | 0.92   | 1.00   |        |  |  |

| Component sales sentiment <sup>4</sup>                                                                           | 121.6% | 113.2% | 121.6% | 122.2% | 120.1% |  |  |

| Sources: <sup>1</sup> IPC (N. America), <sup>2</sup> SIA, <sup>3</sup> 3-month moving average, <sup>4</sup> ECIA |        |        |        |        |        |  |  |

#### Hot Takes

Taiwan's sales of rigid printed circuit boards rose 16% year-over-year in November. (TPCA)

The US Pentagon has launched a \$1 billion program to build an industrial base for attack drones. (US government)

Worldwide **foldable smartphone shipments** are forecast to grow 10% year-over-year in 2025 to 20.6 million units. (IDC)

Global **smartphone shipments** are expected to decline 2.1% in 2026 as rising chip costs are likely to impact demand. (Counterpoint)

**Taiwan's PCB industry** is on track to generate \$29 billion in output in 2025, representing 11.1% year-over-year growth. Combined domestic and overseas PCB production was up 11% to \$21.2 billion during the first three quarters. (TPCA)

Global **chipmaking equipment sales** will rise 9% to \$126 billion in 2026, and past \$150 billion for the first time in 2027. (SEMI)

China's November factory PMI contracted for an eighth month, falling to 49.2, underscoring continued weakness in electronics and PCB manufacturing despite a recent US-China tariff truce.

Worldwide **server market revenue** reached a record \$112 billion during the third quarter, a year-over-year increase of 61% in vendor revenue. (IDC)

Vietnam's electronics exports hit nearly \$143 billion year-to-date through November, with computer, components and device shipments surging 48%. (Vietnam Customs)

US retail sales in November and December will grow between 3.7% and 4.2% versus 2024, for total spending between \$1.01 trillion and \$1.02 trillion. (National Retail Federation)

#### Al Demand Echoes the Late-'90s Tech Surge

Memory chip shortages and PCB order spikes signal strength, but history suggests caution amid the hype.

IT APPEARS THAT possibly, as baseball legend Yogi Berra would have said, it's déjà vu all over again.

Reuters reports that the AI (artificial intelligence) frenzy is creating a major shortage of memory chips, used in everything from consumer electronics and industrial equipment to computers and even the most advanced military systems. Concurrently, the Global Electronics Association (IPC) reported that printed circuit board bookings and shipments surged during October. While both announcements suggest that the electronics industry is alive and well, could they also be a forewarning that we are heading toward the same euphoric economic environment that occurred in the late 1990s?

For the electronics industry, the late 1990s was the best of times, until they weren't. PC power was growing by leaps and bounds, creating constant demand for the latest iteration. The internet was in its infancy, creating an insatiable demand for servers and all the infrastructure required to harness emerging technology and enable users to take full advantage of the nascent web. The dot-com frenzy was upon us. Add to that the fear that Y2K, the millennial bug, would render older computers and analog technologies inoperable, which prompted further demand for new, compliant equipment. Demand for all things electronic, and the printed circuit boards and assemblies that the new technology was built on, was skyrocketing, and company revenues and profits were soaring.

Regrettably, the euphoric '90s came to a stunning halt in 2001. Companies with year-long order books had the rude awakening first that demand was flattening, and then decreasing. Inventories spiked. As a white-hot industry cooled, overcommitted companies began to cancel orders. For the electronics industry, especially the circuit board industry, the bottom fell out and many, many businesses foundered. The best of times became the worst of times.

Many will say, that was then, but this time is different. True, we do not have to contend with the uncertainty of a new millennium; we are now a quarter of the way through it. What is similar – if not identical – however, is the economic frenzy an emerging technology is creating, coupled with the resultant demand for electronics. As with the dot-com environment of the late '90s, euphoria over AI now drives the electronics industry. Every business "must" either make or use AI – even if they are not sure how. Consumers are equally enchanted with the likes of ChatGPT or Google AI Overview, which are being played with and deployed for a host of trivial and major activities.

As with many exciting new technologies, a mixture of science, wishful thinking and a lot of hype have swirled together in the story. Since the dot-com era, other "must-have" technologies have been championed. Electric vehicles

are a recent example that has proven exciting and technologically successful, but perhaps disappointing when it comes to worldwide demand. And while EVs are here to stay, many auto companies are scaling back sales projections, production, new product development and, most importantly, are writing off huge investments that will not meet prior forecasts.

The question is, will demand for all things AI come to the same abrupt demise as the dot-com bubble, or just fizzle, as is occurring with EVs? More importantly, will today's electronics companies take what was learned back then and apply those lessons to avoid potential future calamity?

Short term, the future of AI may serve our industry well in creating demand, filling plants and providing the profits to continue investing in our businesses. Clearly, serious money is being invested at all levels of the AI supply chain. And with any new technology, the goal should be to participate at some level and to take advantage of the opportunity at hand. The challenge is not losing objectivity amid all the hype.

When dealing with anything new, a jaundiced eye can be helpful. Upward projections of demand are fine. Unrealistic or euphoric projections should be questioned and challenged, however. When planning capacity utilization or considering expanding capacity, also consider the business response if projections do not materialize. What if the exit ramp is straight down? Possibly most importantly, diversify your customer base, so all your business eggs are not in a single end-market basket.

AI is the next exciting technology. Just be aware that our industry has been there before many times and, in the past, when there has been excessive hype, the end game has not necessarily gone well. As we all navigate the excitement, use lessons from the past to reduce some of the inevitable risk.

PETER BIGELOW has more than 30 years' experience as a PCB executive, most recently as president of FTG Circuits Haverhill; peterbigelow@msn.com. He is vice chair of the PCEA PCB Management Symposium, taking place April 28 at PCB East.

SAVETHE

**CONFERENCE:**

September 29 - October 2 EXHIBITION:

Wednesday, September 30

**Santa Clara Convention Center**

Brought to you by

pcbwest.com

### Lessons From My Worst Sales Hires

You're going to make some mistakes!

HAVING LED DIFFERENT-SIZED sales forces over the years, I've made some massive hiring mistakes. This isn't a "how to avoid all hiring mistakes" piece; everyone will make hiring errors over a long and active career. It is how you respond to those mistakes that can make a big difference in your company.

#### Some of my mistakes:

• A top East Coast sales manager had an impeccable resume and a history of accomplishments. All his references checked out, and he passed my multiple-stage interviews with his peers and me. Every response was spot-on, demonstrating an uncanny knowledge of our business, and he seemed perfect. At my board meeting, as I was preparing an offer, I advised the board of my concerns that he seems "too good" to be true, but we would know in 90 days. Without too much detail, we began to see issues in the 60-day period, and when 90 days were almost up, I was preparing a termination. He resigned on day 89, having accomplished nothing we jointly set out as a plan for him.

- A gentleman on the West Coast had an impeccable history, accomplishments, solid paper and a depth of understanding of the EMS industry. He was also my worst-ever hire. When I finally understood the mistake I had made and began a corrective program, he quit as well. The lies and falsehoods he made about our company capabilities and myself caused damage across the region to our brand, his teammates (backdoor gossip), and my leadership. On an exit interview he told HR he was afraid I would resort to violence once he left. I had to personally own the corrective actions across the territory, repairing the lies, and it became a massive time-suck to get back to ground zero with potential customers, manufacturer reps and some existing customers. (This pattern repeated in his subsequent career moves, or so I heard from hiring managers who were embarrassed that they, too, had hired him.)

- A young woman whose first three months were as strong as any new hire I ever made, bringing new opportunities and working with me on a massive deal I had started before she came aboard. We lost that deal (no fault of hers), and in the following three months every potential deal she brought to us fizzled, almost all before a quote stage. Then, communications stopped. Every call or "I am coming to travel with you" action was driven by me. We agreed on corrective actions, but none of the milestones was hit. Expenses ceased, new opportunities dried up, reports and CRM entries stopped. When I confronted her, she mentioned that she had "some issues" that were never disclosed to me or our HR department, and she couldn't work for us. After termination, it was rumored she may have held a concurrent job with a competitor.

Keep in mind I always lived and worked hundreds or thousands of miles away from my team, so we didn't meet face-to-face in the office every week. We had reporting (CRM) requirements, however, as well as many calls during the week. I also traveled with my team as often as possible, helping move deals forward or assisting with closing deals. Metrics were fudged, details of their activities were fabricated and when I made time to travel with them there seemed to be health or family reasons many of those planned trips had to be postponed. The 30, 60, 90, 180 and 360-day sales goals that were mutually agreed upon onboarding with each new hire, and their subsequent progress reports, mostly turned out to be inaccurate.

For many years, I ran remote sales forces ranging from three to 100 strong. But my propensity to believe my team over what the metrics were indicating led me to suboptimize my role to some degree with these three individuals. Some of these folks also came through professional EMS recruiters, who also could have been able to spot issues before presenting a candidate to me.

#### The takeaways:

- 1. When managing a team over a long period of time, you'll make hiring mistakes.

- 2. Good paper (résumés), prescreening by a recruiter, multiple "touch points" in an interview process with multiple cross-functional senior leaders, excellent knowledge of our business and solid references don't always guarantee a good hire.

- 3. In the highly competitive EMS sales world, with our extremely long sales cycles, it will probably take more than a few months to discover you have made a bad hire.

- 4. Personality tests don't guarantee a good fit.

- 5. Using a professional EMS recruiter is no guarantee. (Note to all my EMS recruiter friends: you are an excellent resource, just not foolproof.)

- 6. Setting 30, 60, 90, 180 and 360-day sales plans/goals during the first week of employment (onboarding), detailing jointly agreed-upon accomplishments/milestones, are a good indicator of future success, but not a 100% guarantee.

- 7. You cannot run a salesforce from a dashboard (CRM) alone. You must be in the field selling with them. That said, tracking progress in a CRM is an indicator to pay attention to.

- 8. A good passive way to view remote sales progress is expenses, which is counterintuitive to a fiscally conservative company. If they aren't spending on lunches, as one example, something's up.

- 9. Speaking with and visiting potential new prospects the new hire is engaging is smart practice, but no guarantee of success.

- 10. A detailed job description is important to avoid any misunderstanding early in an interview process.

I treated recruiting as a 24/7 sort of side job I had to do. I was always on the look-out for talent and performance. I used all these takeaways in the hiring process, and in managing them once they were hired. And while most of my recruiting was successful, I made some huge mistakes. How I responded when it became clear I made an error were some of my most memorable accomplishments.

Want to be a dynamic growth engine sales leader? Get over yourself. We all make mistakes. Failing to admit them, refusing to try to correct them, and finally having to make a hard termination call if you cannot turn the person around, is what can kill your small-to-medium-sized business. I was often asked if terminating an employee was hard. Yes! If it becomes easy to fire someone, it is time to punch out; you've lost your heart.

Use your best demonstrated practices recruiting and making hiring decisions, try not to make a quick hiring decision no matter how good the person seems, stay true to your recruitment process, and while you'll probably be successful most of the time, you will have some catastrophic failures. Identify them as fast as possible, invest time to correct those errors and terminate quickly when you are sure this was a hiring mistake.

JAKE KULP is founder of JHK Technical Solutions, where he assists OEMs and EMS companies with optimizing demand creation offerings and deciding when and where to outsource manufacturing. He previously spent nearly 40 years in executive roles in sales and business development at MC Assembly, Suntron, FlexTek, EMS, and AMP Inc. He can be reached at

jkulp@cox.net.

We are committed to advancing technology through shared knowledge and collective excellence.

# Thank You! PCEA CORPORATE MEMBERS

Collaborate across the electronics industry,

Educate future innovators, and

Inspire a global community of professionals.

# Join Today!

WTT TECHNOLOGIES

## Reviewing the PCB Design Review Process

A structured design review process ensures alignment across teams.

ONE THING IS certain about printed circuit board design: change is inevitable. The vernacular surrounding the art and science of PCB design gives credence to this statement. Upfront, it's a schematic editor that leads to a layout editor. If you get far enough downstream, you're working with a Gerber editor. Across the board, the notion of making changes is distilled into the process.

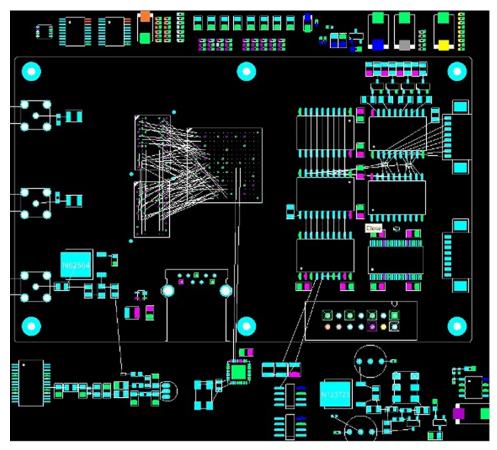

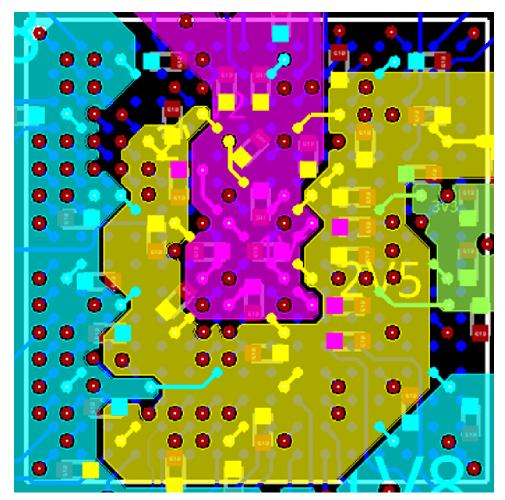

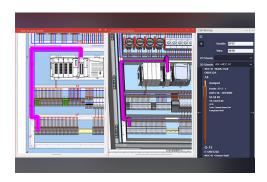

Figure 1. Colorizing power and ground domains helps floorplan the design. The passive components arrayed across the top of the board are mostly bypass capacitors intended for the secondary side. The components below are pre-placed to provide greater visibility into the extent of these subcircuits. (Credit: Author)

Another axiom in effect is: "If it works, don't break it." This sentiment is especially strong where a circuit must be qualified through a regulatory body. If a radio meets the requirements, it's as if it were written in stone rather than copper. Change is for the better unless it adds unreasonable risk or lengthens the schedule.

It's important to maintain that continuity while making improvements as needed. A second pair of eyes is always helpful and, in fact, the more the merrier, up to a point. The mechanical engineering of PCB layout is the foundation of the circuit board, while embedded electronics are the vessel for the software. Testing the circuit lies somewhere between these two camps. Herding all these cats requires finesse from the PCB designer.

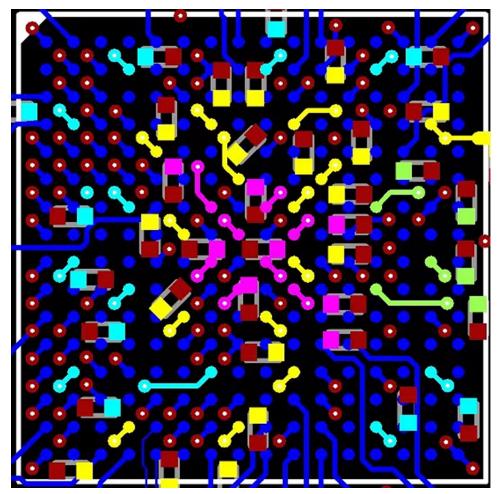

Figure 2. Capacitors on the bottom (red) respond to a 1.2V patch of pins (magenta) in the middle of the processor. Surrounding them is a ring of 2.5V (yellow). Finally, the outer voltage domain is for 1.8V (cyan) with a side of 3.3V (green). Completing this PDN is a top priority. (Credit: Author)

**Getting the lay of the land.** Kicking off a layout usually starts with the mechanical information. Design reuse of the mechanicals is a common theme. The trick is that later upgrades rarely come in the form of a reduction to the bill of materials. We fix electrical problems with more electronics, perhaps a new filter or a shield. Sometimes, it's another mounting hole, and it could be all those things at once.

We compete in the market with new features to enhance the product. Even with the same feature set, we're compelled toward faster, smaller and more efficient designs. You could say that revision 1 is just messing around, while revision 2 is after you find out what was overlooked in the rush to market.

With all of this going on, we can't go it alone. Tight schedules push us into a corner. Backtracking is a waste of that precious time and money. The goal is always to do it right the first time. All this is just to say that we need clear communication on every aspect of ongoing improvements.

Arbitrary and capricious "changes" can backfire. Don't go at it alone. Schedule a design review at each stage of the design cycle. Day one of the schedule is a good time for setting milestones. Once you have an outline and a stackup, you have enough data for a budgetary quote from your vendor(s). "Vendor" should always be plural for the bare board as well as the components.

Figure 3. Fan-out optimized for bypass cap placement and avoiding choke points in the power planes. (Credit: Author)

**Being prepared to kick off placement.** The mechanical outline and stackup should account for all packages involved, as well as the routing and placement keep-out regions. If you don't want routing below a component type, the footprint should include a route keep-out. I built a route keep-out into every inductor since no one wants routing under there. Some sensors require more clearance than a standard part. That extra space should be incorporated into the virtual part.

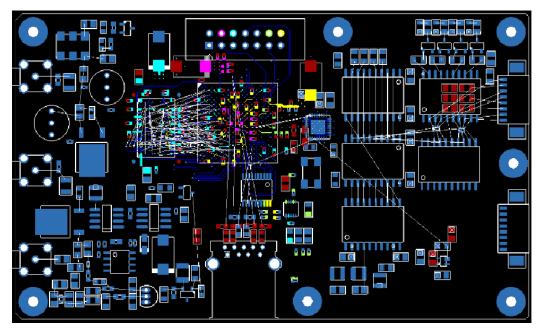

Figure 4. When all was said and done, the board grew horizontally while the technology moved from plated-through-hole to HDI in order to place the DDR memory belly-to-belly. (Credit: Author)

The more absolute rules you can encapsulate, the better. This serves two purposes. It reduces your workload and shows reviewers that you're aware of the constraint and have acted. Keep-ins, keep-outs, headroom limits and other restrictions can be a hassle, but the payoff is a compliant PCBA that fits where it belongs and works as intended.

**The design review.** Design reviews will be boring for someone with no stake in that part of the process, so the attendee list should reflect that. The mechanical engineer is required to verify that the board outline and all non-electrical features were imported correctly. That's square one. There's no point in inviting the test engineer to that review. Loop them in when you're fairly certain that the test points have optimal coverage. By that point, the ME is out of the picture. Their return could be disruptive.

Certain milestones deserve a design review.

- 1. Mechanical outline review, including all components, holes and other features covered by the outline drawing. An outline drawing might not yet be available. At a minimum, we compare the layout to the 3-D model to see if everything makes sense. This should involve you and mechanical engineering. After this review, it makes sense to spool up the fabricator so they can provide trace geometry and any other input related to the proposed stackup.

- 2. Library completion with all components randomly placed outside the board outline. This is you, the EE and maybe copy the project manager. If you're lucky enough to have a dedicated librarian, loop them in.

- 3. Critical placement with RF chains routed and major ICs in their proposed locations. You, the EE and signal integrity, and at least one of your peers, if possible.

- 4. Detailed but rough placement with your best effort at fleshing out the power delivery network (PDN). This is a good time to organize your reference designators for the first time. Doing so will make the final push a little

more bearable. You, the EE and power integrity.

- 5. After fanout of the most complex integrated circuits. You the EE and, again, copy the project manager. The assembly team, whether in-house or contracted, should be included for a placement evaluation. They can advise you on the assembly subpanel and any test coupons, as required. Markup every document shared as **Preliminary!**

- 6. When memory or other high-speed signals have been connected and length-matched as required. Bring back signal integrity and call on test engineering. The EE should be in the loop daily at this point anyway.

- 7. Routing of the miscellaneous unnamed traces. You, the EE, your manager and a friend to balance out the power dynamic. After this, your main objective is punching in gratuitous vias for thermal and signal integrity compliance.

- 8. Full documentation package with all design rule errors squared away. Make a print of every layer and each drawing so there's something to mark up. Invite mechanical engineering, electrical engineering, project management, your manager and the SI/PI team. CC everyone else who contributed to the design effort.

Depending on the design's complexity and nature, some of these may be combined, but it still pays to break the job down into milestones so you can tell whether the project is on track to meet the tape-out date. Waiting until tape-out day to say that the board isn't done could be seen as a failure on your part, particularly if you've been on "radio silence." Keeping on top of the schedule is a part of managing expectations.

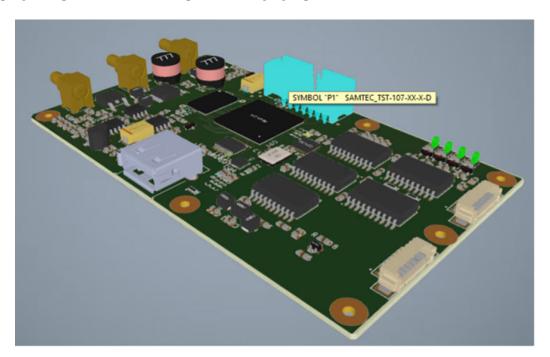

Figure 5. A sanity check after moving the JTAG connector. I will also revisit the inductor between the SMB connectors in the upper corner. (Credit: Author)

The number of touchpoints will vary with each design. Some folks will need a special reminder to make it to the meeting. I remember a signal integrity guy hiding from everyone while using the design review to catch up on his emails. It cuts both ways. Modern times have spread out the workforce, so there are likely to be people phoning it in. Make sure they have a chance to speak and that no one in the room talks over them.

**Schedule design reviews as soon as practical.** Everyone's calendar fills up by the time they get to work that day. Scheduling these reviews at the start of the layout gives you flexibility to include the people you need, when you need them. This can be done while the schematic is in progress, with the schematic-complete milestone penciled in somewhere along the way. Let's be honest here. The schematic will not be done on the day you start the layout.

When things outside of your control happen, it's the only time you can be forgiven for proposing a whole new set of dates for the follow-on milestones. Product managers are under pressure too. They do not want you to pad the schedule for unforeseen circumstances. We act like everything will fall into place at the right moment, but it doesn't happen often.

**Hope for the best while preparing for the inevitable.** While Sun Tzu often gets credit for it, Helmuth von Moltke said, "No plan survives contact with the enemy." To be clear, your coworkers are not the enemy, but they do tend to disrupt the best laid plans. As we work with those around us, we learn who is most likely to surface with a last-minute request.

We manage those people the same way we manage an overwhelming concentration of "rats" coming out of an SoC. Ping them early and often. Ask how confident they are in the input provided at any stage. Some people will hold back on giving new information until they are certain that it is the best way forward. They keep their cards close to the vest until they are compelled to share. At the same time, the vendor can't answer questions that weren't asked.

I remember at Qualcomm when we onboarded an engineer on a work visa. She was from Australia and informed us that she received the very last visa issued for that year. I remarked that she was going to fit right in and added that, "If it wasn't for the last minute, nothing would get done around here." It isn't just Qualcomm. It's human nature. It's incumbent upon us to herd those cats to get the job done by the 11th hour, when it all comes together.

JOHN BURKHERT, JR. is a principle PCB designer in retirement. For the past several years, he has been sharing what he has learned for the sake of helping fresh and ambitious PCB designers. The knowledge is passed along through stories and lessons learned from three decades of design, including the most basic one-layer board up to the high-reliability rigid-flex HDI designs for

aerospace and military applications. His well-earned free time is spent on a bike, or with a mic doing a karaoke jam.

# Why Become a <a href="PCEA Corporate Member?">PCEA Corporate Member?</a>

- ✓ Information, opportunities & marketing channels to highlight your brands, products & services to buyers & users worldwide

- ✓ Inclusion in the PCEA Member Directory, a product & service guide for buyers & users

- ✓ **Free advertising** of your products & services to more than 50,000 design engineers, fabricators & assemblers

- ✓ **Discounts** on trade shows, technical conferences, online learning platforms & webinars

# Join today: pcea.net/pcea-membership

# The AI Boom is Driving Technological Change at Every Level, Reshaping Supply Chains and Business Strategies

Al investment shows no signs of slowing, prompting concern about what happens when it eventually does.

VICTOR HUANG HAS described ChatGPT's arrival as AI's "iPhone moment," when the technology's potential to change the way we live became clear to all. Indeed, the publication of large language models (LLMs) is arguably the most powerful innovation we have seen so far, enabling widespread user engagement spanning personal and professional purposes. Resulting from this, acceptance has snowballed and more and more of us have come to trust and rely on AI assistants. In turn, mainstream use has driven further improvements, as successive updates have delivered more humanlike interactions and additional capabilities.

Within a short space of time, it seems, an AI-based solution has become available for almost everything. In some of the most contentious examples, AI is giving us original novels, including new works in the style of our favorite authors, and virtual film stars. At the same time, the Albanian government has even put an AI – complete with a traditionally dressed avatar – in charge of its national procurement department. On a more day-to-day level, many of us are discovering how much we need the skills AI can bring to our lives, for finding information on the Internet, organizing our digital content, taking better selfies and fulfilling job responsibilities.

On the one hand, edge AI and tiny machine-learning (ML) applications, while on the other, cloud data centers are where we find the heavy lifting for social media, business applications, and intensive analytics. The AI data center server market has become a huge opportunity for equipment vendors as operators upgrade their data centers to meet the explosion in end-user demand. Already worth almost \$300 billion, currently representing 17% of the total server market by value, it's predicted to grow another 20% in 2026.

The effects permeate the entire hardware supply chain, extending to materials needed for chip-packaging substrates and PCBs for high-performance accelerator cards and motherboards. This is advanced, high-end materials technology, including low-CTE quartz glass and ultra-low-profile copper foils needed for high-layer-count boards. The boards are made using advanced techniques such as semiadditive process (SAP) and modified SAP (mSAP) for precise control over circuit dimensions, allowing designers to achieve feature sizes as small as 30µm and traces of 15µm width. Some advanced mSAP and full SAP can achieve even finer features, down to 5-10µm. The opportunities for AI data center equipment present a powerful lure for materials suppliers and fabricators to focus more sharply on high-end products or even realign their businesses away from PCB fabrication and into IC packaging. As AI processors and high-

bandwidth memory drive demand for high-performance substrates, this is a \$20 billion slice of the action in a global semiconductor market poised to reach \$1 trillion in revenues by 2030.

Attracted by the prospect of greater margins, some suppliers are moving higher up the value chain and out of their traditional markets for conventional standard materials. While not all are following this trend, shortages and price increases are likely for these products as the supply chain adjusts and other companies in different geographic areas take over.

As consumer excitement over AI rises to ever-higher levels, however, signs of dissent are appearing. Doubters question whether the current boom is a bubble that's about to burst. While arguments rage on either side of that debate, we must consider at least one spectacular precedent: the telecom industry of the early 2000s. Some of the industry's biggest and most successful hardware suppliers, which built for what they thought was limitless demand, suddenly found themselves holding vast unsold inventories and were forced to revise their forecasts. Multi-billion-dollar write-downs followed, and key players suffered enormous pain in the stock markets. While some are even now just regaining their pre-boom market valuation, others went bust in the debacle, along with many overhyped dotcoms. We are certainly experiencing a hardware boom today, as data centers invest in new AI servers. In the historical telecom example, spending stopped suddenly due to the dotcom bust as operators stopped spending on hardware and reverted to their normal investment cycle of about 5-10 years, which is the typical lifetime of carrier-grade switches.

Today's top computing companies estimate the lifetime of an AI server at 3-6 years. Investment could slow, although the timing is very difficult to predict accurately. After the telecom bust, a major materials supplier asked me to carry out an analysis to learn whether similar issues in the future could be anticipated and avoided. Notionally, of course, it's easy to predict a fall happening sometime because demand cannot continue rising forever. In reality, dynamic high-tech markets that are constantly creating new services and capabilities have many variables as well as many unknowns. With so many interrelated and abstract factors in play, accurately pinpointing the timing and extent of any downturn is practically impossible.

This time, will we learn the lessons history teaches us? Few can resist the excitement of a boom, and shareholders will always expect executives to follow the money. Right now, data centers are still investing in hardware, and the market is expected to continue growing strongly. Sooner or later, however, every bubble bursts and all will be affected in some way. The industry needs to combine dynamism to make the most of the market highs with the resilience to handle the inevitable lows.

ALUN MORGAN is technology ambassador at Ventec International Group (venteclaminates.com); alun.morgan@ventec-europe.com. His column runs monthly.

## Comprehensive PCB Design Training

### **NEXT CLASSES:**

Feb. 6, 13, 20, 27 & Mar. 6 May 15, 22, 29, Jun. 5 & 12

### Metal-Core PCBs and Thermal Management

Catch heat at the board before it turns into a full-time job.

HEAT SNEAKS UP fast in today's electronics. Higher power density, smaller form factors and long-life reliability expectations all collide, requiring better thermal design. The teams that come out on top with this challenge are the ones who solve heat at the PCB level rather than trying to fix it later with a bigger heat sink or more airflow.

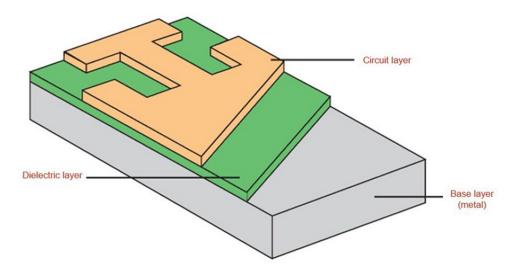

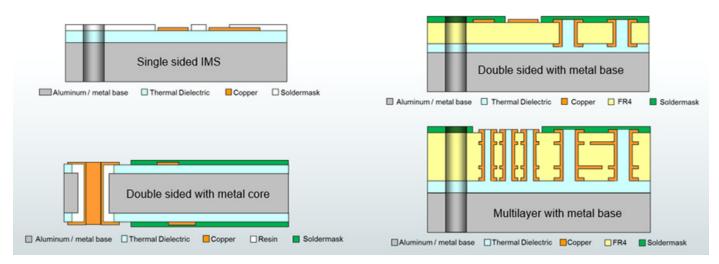

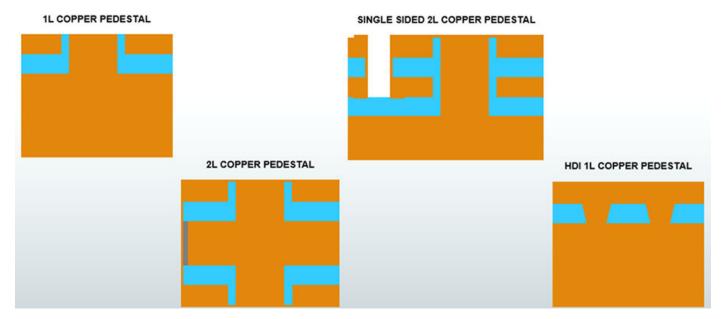

PCB products designed for this level of thermal management generally fall into two categories. The first is metal-base, often called IMS or insulated metal substrate. The second is metal-core. In both variations, the technology turns the familiar idea of a printed circuit board into an active part of the thermal system, rather than expecting FR-4 to carry the load. FR-4 is an excellent structural and electrical material, but it is not a thermal material.

IMS and metal-core types are often referred to interchangeably, and while they share many common traits, there are a few distinct differences worth understanding before choosing one over the other. With MC PCBs, for instance, the heat has a direct path into a metal substrate, such as aluminum or copper. This puts the thermal solution right beneath the components that generate the temperature rise. By permitting the PCB to act as a direct heat distributor, designs become more compact, more predictable, and often lower cost overall. It also buys a lot of reliability margin, especially in LED lighting, power electronics and automotive systems, where junction temperature directly translates to product life.

The fundamental advantage of a metal-base PCB comes down to thermal conductivity. FR-4 stays around 0.3 - 0.5W/m·K, which is enough for structural integrity and electrical insulation, but not for heat. Aluminum substrates typically offer 1 - 4W/m·K, while copper can reach anywhere from 3 to around 14W/m·K, depending on the grade and the dielectrics paired with it (Figure 1).

| Material               | W/mK          | Comment                                                                                                                                                                     | rnermai<br>conductivity | Availability    | Price           |  |

|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-----------------|--|

| Standard FR4           | 0.2-0.6       | Benchmark - Epoxy resin woven glass system                                                                                                                                  | LOW MEDIUM HIGH         | LOW MEDIUM HIGH | LOW MEDIUM HIGH |  |