# PRINTED CIRCUIT DESIGN & FAB

pcdandf.com

circuitsassembly.com

February 2026

CIRCUITS

ASSEMBLY

For AI, Context Reigns Supreme

## Precise Prompts, Perfect Production

- ✓ Drill-to-Trace Clearance

- ✓ UHDI DfM

- ✓ PCB Vibration Analysis

# Flex PCB Assembly & Manufacturing

Get your Custom PCBs exceptionally fast and perfectly tailored to your business needs with our complete dedication to quality and high performance.

[Click to learn more](#)

**PCB TRACE**

20 YEARS OF MANUFACTURING

EXPERIENCE WITH BLIND AND BURIED

VIAS, RIGID FLEX & FLEX PCB

# RUSH PCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH

BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB

ELECTRONIC DESIGN, & QUICK TURN CIRCUIT

BOARDS, ASSEMBLY & FULL TURNKEY

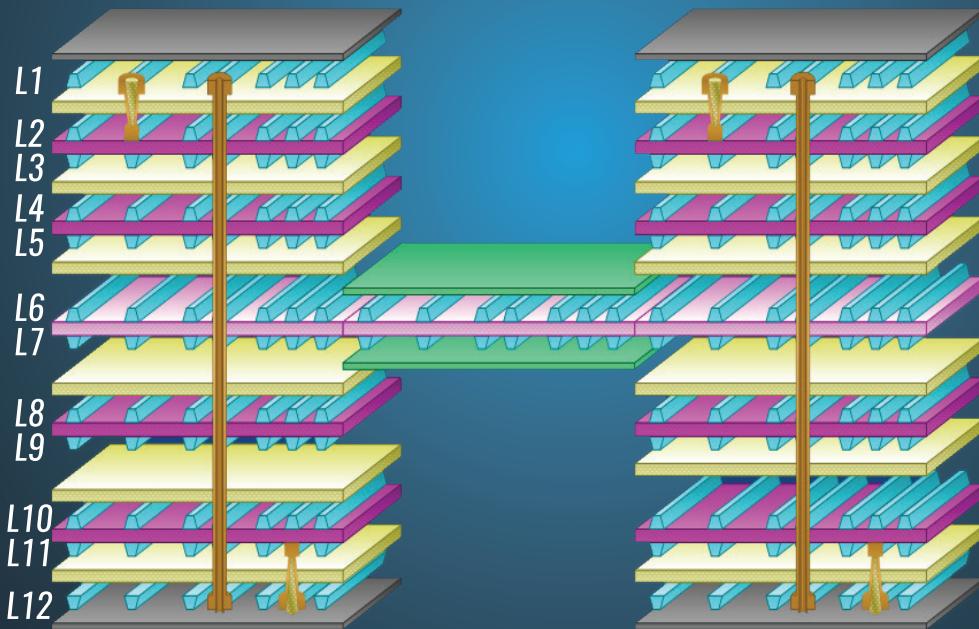

# Multilayer PCB Stackup

**12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex

Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled,

0.002"/0.002" Trace/Space, Controlled Impedance**

Manufactured on August 2016

**When you're in a rush call RUSH PCB**

Affordable Pricing • Satisfaction Guarantee • Fast Response • Free Quote • Fast Shipping

HDI Boards • Stacked Micro Vias • 2 mil line & Space • Flex & Rigid Flex

**Located in the Silicon Valley

PCB up to 12 Layers in 3 days

PCB Assembly Same Day Turn

Full Turnkey Service**

**Certified: ISO9001/ITAR/UL**

[www.rushpcb.com](http://www.rushpcb.com) | [Sales@rushpcb.com](mailto:Sales@rushpcb.com) | 1 408 496 6013

Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

## FIRST PERSON

## THE ROUTE

The hidden cost of AI.

Mike Buetow

## MONEY MATTERS

## ROI

Materials limits loom.

Peter Bigelow

## BOARD BUYING

Buying boards like pros.

Greg Papandrew

## FOCUS ON BUSINESS

Controlling EMS chaos.

Susan Mucha

## TECH TALK

## REBUILDING THE BASE

PCBAA is leading the way on reshoring.

Dan Beaulieu

## DESIGNER'S NOTEBOOK

Quality is earned.

John Burkert, Jr.

## DESIGN BEST PRACTICES

How AI is impacting signal integrity.

Stephen V. Chavez

## MATERIAL GAINS

Packaging power shifts.

Alun Morgan

## THE FLEXPERTS

Bake before reflow.

Mark Finstad

## SEEING IS BELIEVING

Climbing the Anthill.

Robert Boguski

## TECHNICAL ABSTRACTS

## DEPARTMENTS

## AROUND THE WORLD

## PCEA CURRENT EVENTS

## MARKET WATCH

## OFF THE SHELF

## PRINTED CIRCUIT DESIGN &amp; FAB CIRCUITS ASSEMBLY

## FEATURES

## ULTRA HDI FUNDAMENTALS

## Designing for Manufacturability in Ultra HDI: New Rules, New Realities

Ultra HDI reshapes the design-for-manufacturability equation, forcing designers to rethink spacing, stackups, tolerances and yield assumptions as processes change.

by ANAYA VARDYA

## SPACING LIMITS

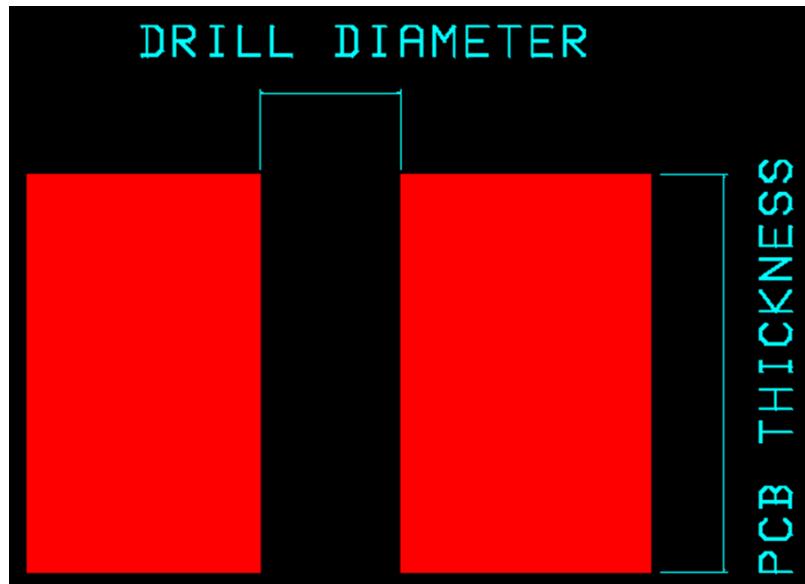

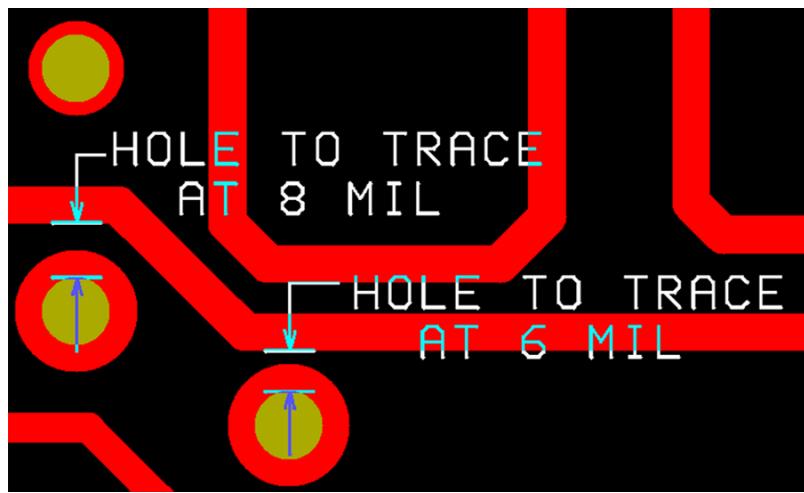

## Consider Manufacturing Complexity When PCB Designs Have Tight Hole-to-Trace Spacing

Tighter spacing can mean using smaller drill sizes, increasing aspect ratio and complicating plating operations.

by AKBER ROY

## PROMPT DISCIPLINE (COVER STORY)

## AI 'Hallucinates.' Why That's Actually Good News.

AI doesn't "know" anything. Without the right context, its answer can sound right but could quietly derail manufacturing decisions.

by SEAN PATTERSON

## ENVIRONMENTAL TESTING

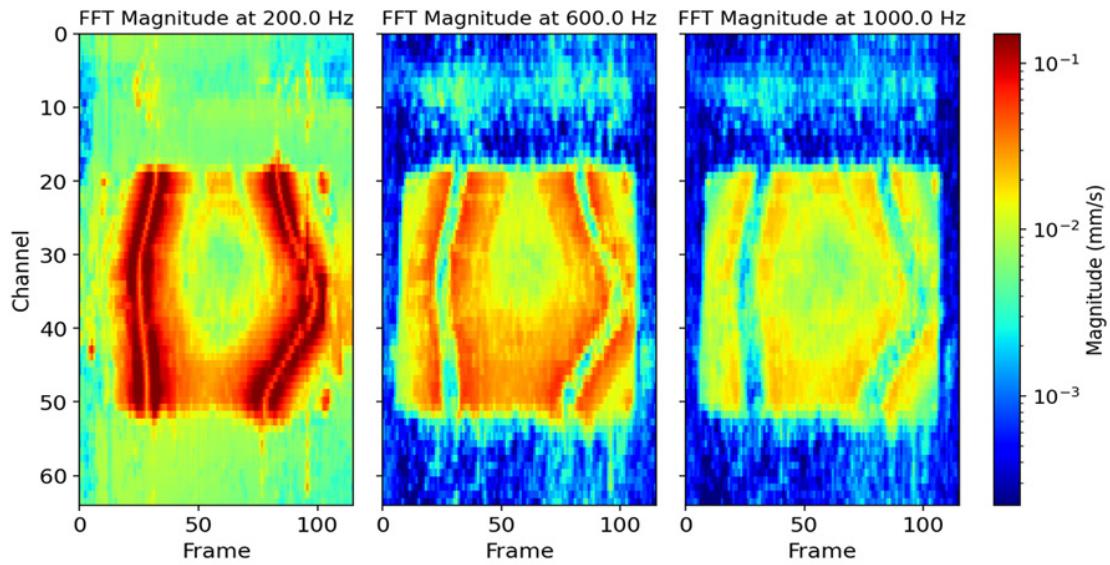

## Vibration Analysis of PCBs for Critical Applications

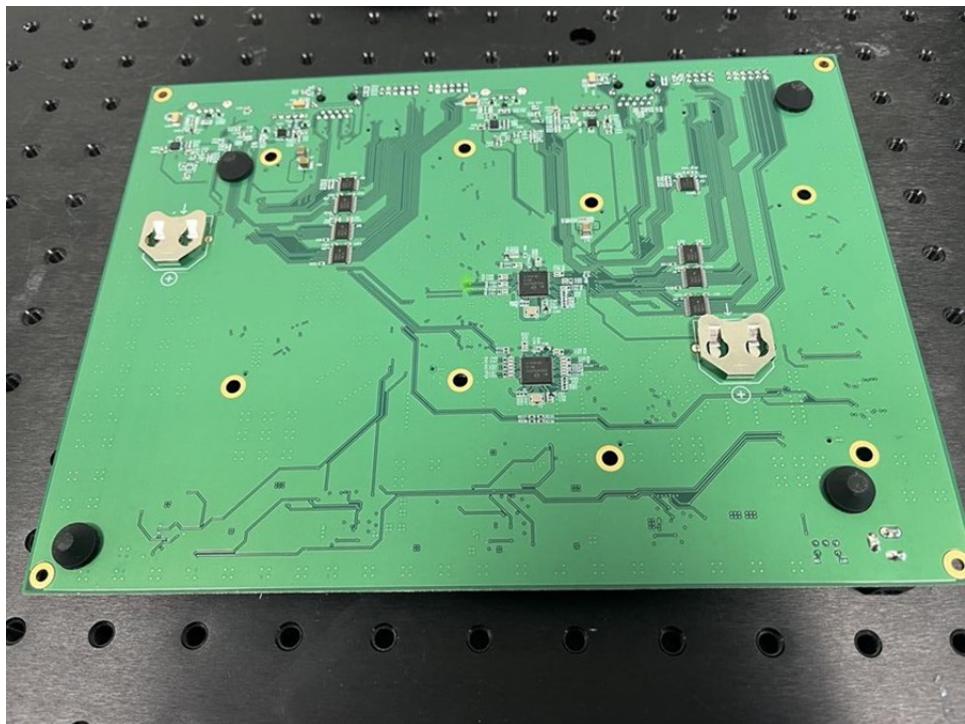

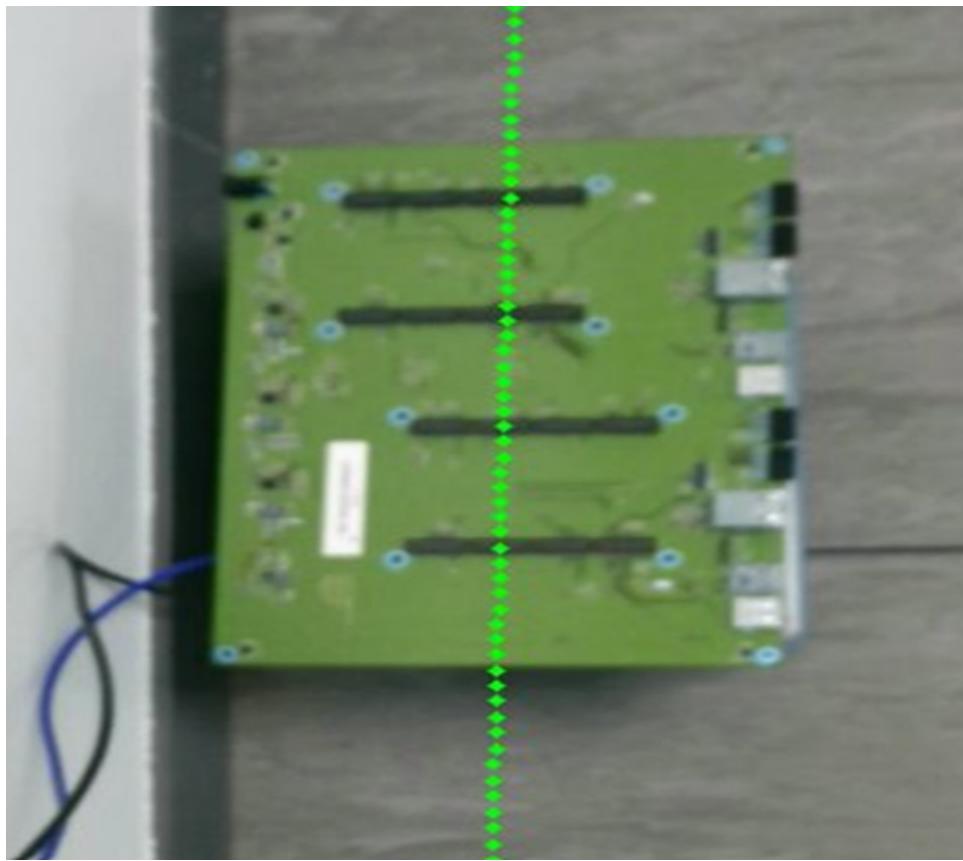

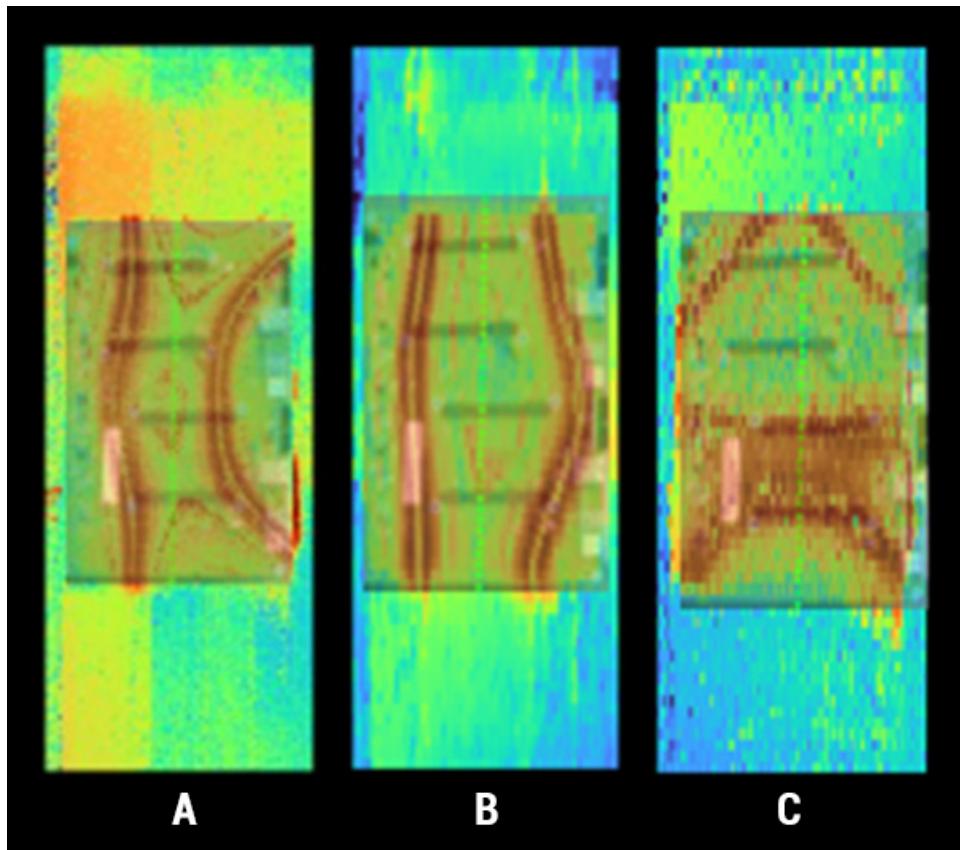

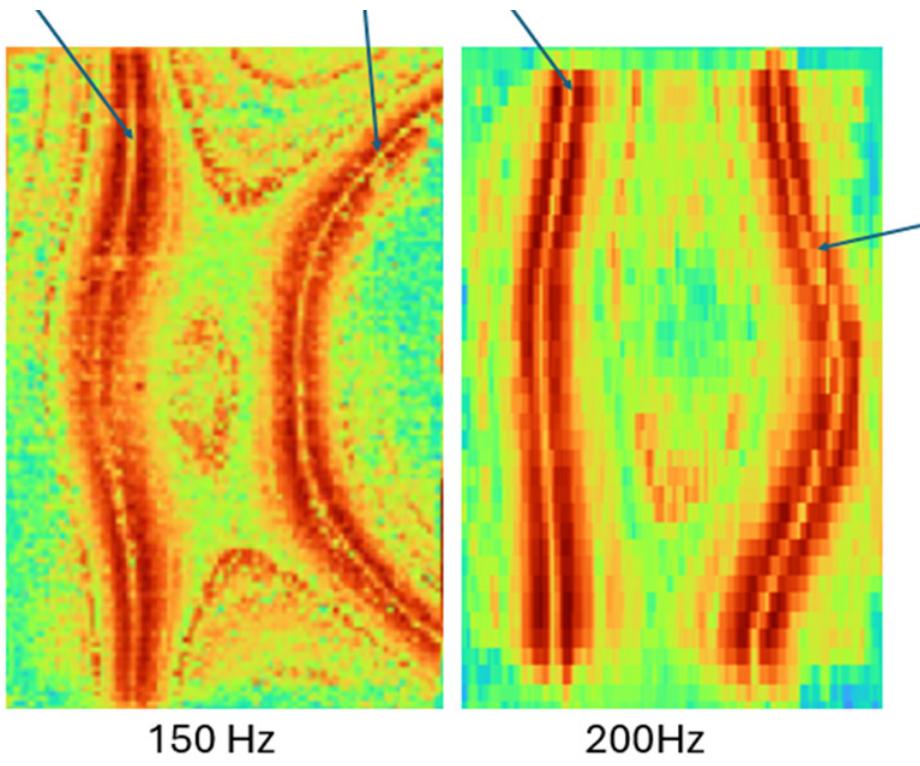

Understanding how PCBs deform and vibrate under load is essential to achieving reliability goals. Laser doppler vibrometry enables simultaneous measurement at dozens of points across populated PCBs, revealing component-level failure risks that accelerometers miss.

by ELADIO MONTOYA, PH.D. and ÓSCAR R. ENRÍQUEZ, PH.D.

## ON PCB CHAT (PCBCHAT.COM)

## PCB Chat

## BECOMING A DESIGNER

with MARGARET FRACHIONI

## DISPENSING DONE RIGHT

with JON URQUHART

## ECAD MARKET PULSE

with WALLY RHINES

## ACCURACY VALIDATION AND FORCE MEASUREMENT

with MICHAEL SIVIGNY

# SIEMENS

See us at APEX

Booth #3644

Start where you need.

Scale when you're ready.

**The Xpedition family

grows with you.**

**PADS Pro

Essentials**

ACCESSIBILITY

**Xpedition

Standard**

SCALABILITY

**Xpedition

Enterprise**

PERFORMANCE

FROM INDIVIDUALS TO ENTERPRISES

Printed Circuit Engineering Association

PCEA

PO BOX 237

PORTSMOUTH, NH 03802

#### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN

Susy Webb, VICE CHAIRMAN

Justin Fleming, SECRETARY

Anaya Vardya, TREASURER

#### MEMBERS

Jim Barnes

Michael Buetow

Tomas Chester

Douglas Dixon

Juan Frias

Richard Hartley

Matthew Leary

Charlene McCauley

Eriko Yamato

PCEA.NET

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

##### PUBLICATION

PCD&F/Circuits Assembly ..... digital.pcea.net

##### WEBSITES

PCD&F ..... pcdandf.com

Circuits Assembly ..... circuitsassembly.com

##### NEWSLETTER

PCB Update ..... pcbupdate.com

##### PODCASTS

PCB Chat ..... pcbchat.com

##### EVENTS

PCB West ..... pcbwest.com

PCB East ..... pcbeast.com

PCB Detroit ..... pcea.net/pcb-detroit

##### EDUCATION

PCB2Day ..... pcb2day.com

PCEA Training ..... pceatraining.net

Printed Circuit University ..... printedcircuituniversity.com

##### AWARDS PROGRAMS

Service Excellence Awards ..... circuitsassembly.com

NPI Awards ..... pcea.net/npi-award

PRINTED CIRCUIT

DESIGN & FAB

CIRCUITS

ASSEMBLY

CIRCUITS ASSEMBLY'S

SERVICE EXCELLENCE

AWARDS

PCB Update

PCEA

TRAINING

PCB Chat

PRINTED CIRCUIT

DESIGN & FAB

CIRCUITS

ASSEMBLY

pcdandf.com

circuitsassembly.com

#### MANAGEMENT

##### PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net

##### VICE PRESIDENT, SALES & MARKETING

Frances Stewart 770-361-7826 | frances@pcea.net

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

##### MANAGING EDITOR

Ryann Howard 912-803-9780 | ryann@pcea.net

##### CONTENT ARCHITECT

Andy Shaughnessy 770-315-9901 | andy@pcea.net

#### COLUMNISTS AND ADVISORS

Jeffrey Beauchamp, Dan Beaulieu, Peter Bigelow, Robert Boguski, John Burkhardt, Jr., Stephen Chavez, Mark Finstad, Geoffrey Hazelett, Nick Koop, Jake Kulp, Alun Morgan, Susan Mucha, Greg Papandrew, Hemant Shah, Chrys Shea, Jan Vardaman, Gene Weiner

#### PRODUCTION

##### ART DIRECTOR & PRODUCTION

blueprint4MARKETING, Inc. | production@pcea.net

Nathan Hoeller | nathan@pcea.net

#### SALES

##### VICE PRESIDENT, SALES & MARKETING

Frances Stewart 770-361-7826 | frances@pcea.net

##### SENIOR SALES EXECUTIVE

Will Bruwer 404-313-1539 | will@pcea.net

#### EVENTS/TRADE SHOWS

##### EXHIBIT SALES

Frances Stewart 770-361-7826 | frances@pcea.net

##### TECHNICAL CONFERENCE

Mike Buetow 617-327-4702 | mike@pcea.net

##### WEBINARS

Andy Shaughnessy, 770-315-9901 | andy@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly.com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 237, Portsmouth, NH 03802. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2026, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is forbidden without written permission.

See us at APEX

Booth #3932

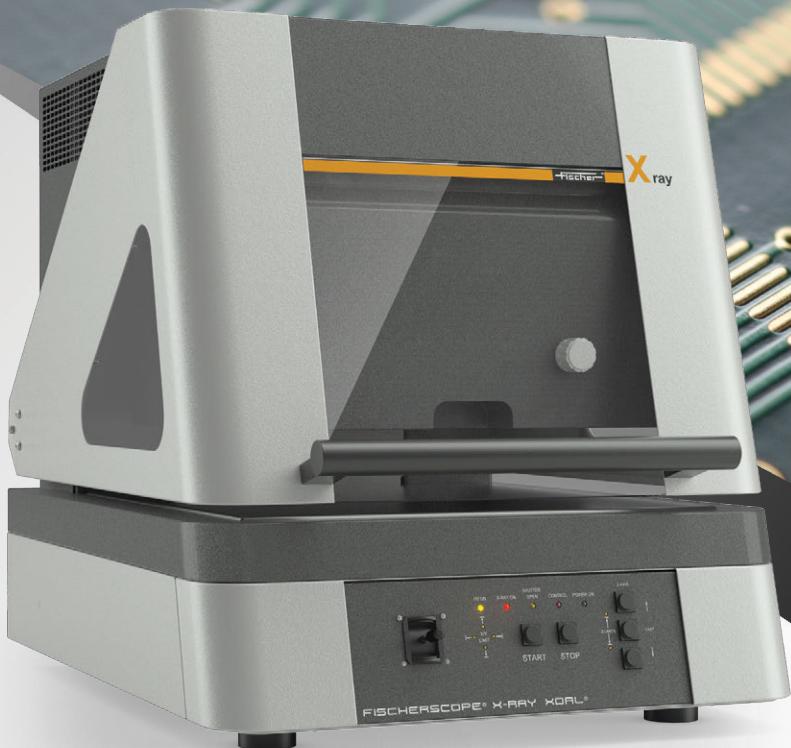

## Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

Measuring Made Easy®

[www.fischer-technology.com](http://www.fischer-technology.com) | [info@fischer-technology.com](mailto:info@fischer-technology.com) | 860.683.0781

**fischer**®

# The Hidden Cost of AI: When Data Centers Devour Your Supply Chain

**ANALYSIS OF ARTIFICIAL** intelligence's place in the world is as ubiquitous (and occasionally, insufferable) as those chatbots cluttering up many businesses' websites. Not unironically, then, am I adding to the din.

More than [5,400 data centers operate in the US alone](#) today, including more than 50% of the world's hyperscale AI facilities. Last year alone, global spending on data centers reached an estimated \$580 billion and is expected to continue to grow at a 28% clip per year through 2030, with AI investments alone reaching \$200 billion by 2030. Assuming much of that investment is financed, interest charges from that capex could exceed \$1.5 trillion.

Much of the impact – realized or projected – has focused on energy consumption and location, and for good reason. While local folks might want access to AI so they can make quick work of otherwise time-intensive projects, they tend not to want to see their energy bills spike to underwrite the data center across town.

The [average data center holds 2,000 to 5,000 servers](#), with smaller ones ranging from 500 to 2,000. According to the International Energy Agency, [worldwide electricity consumption for data centers](#) is projected to double by 2030 to around 945TWh, which translates to about 3% of total global electricity consumption. Given how much developed economies rely on computing power, that doesn't seem too bad.

However ... during that span, data center electricity consumption is expected to grow around 15% per year, which is more than four times faster than the growth of total electricity consumption from all other sectors. And in areas with high numbers of these server farms, consumer [pushback is already being felt](#).

Then there's the comparisons to the dot-com bubble, when high demand for the nascent Internet industry spurred mass overbuying of – that's right – servers, culminating in Cisco, then (and now) the largest network infrastructure OEM, taking a \$2.25 billion inventory write-down in a single quarter. (In layman's terms, that meant Cisco determined the market value of the finished goods it had on hand was over \$2 billion less than what they originally paid. Ouch.)

Amid the hue and cry, less recognized are the downstream material shortages threatening to jack up prices on all kinds of products. And for those of us who recall the material shortages of the 1990s, forgive us if we think the potential financial reckoning might already be at hand.

[AI datacenters will use some 70% of all high-end DRAM production in 2026. Component suppliers are changing up their processes](#), cutting lower-margin product to free capacity to feed AI demand. DDR4 memory is falling victim, as

major component makers sunset those parts. Memory prices shot up about 50% in the fourth quarter, and [TrendForce](#) sees prices rising by another 70% in 2026 due to persisting shortages.

Hope you bought that new computer ahead of the Windows 11 switch, because it is probably about to become a whole lot more expensive. “Memory shortages are affecting the entire industry, and the impact will likely reshape market dynamics over the next two years,” said Jitesh Ubrani, research manager, IDC, in the research firm’s quarterly [PC industry forecast](#).

The surge has laminate vendors and their suppliers on edge, too. Supplies of BT resin and T-glass, used in materials for much of the AI chip substrates and boards, are already strained. Nittobo, the Japanese company that holds most of the patents and manufacturing expertise for T-glass, and Mitsubishi Gas Chemical, the largest supplier of BT substrate raw materials, [are both warning of sold-out conditions](#) into the second half of 2027.

The knock-on effect is not just that PCB designers must adjust their component BoMs, but fabricators need to consider different glass fabric styles. A lot of conversations need to take place, in short order.

As AI effects are throughout the supply chain, whether humanity is unlocking the doors to its own replacement might be the least of our concerns.

[mike@pcea.net](mailto:mike@pcea.net)

[@mikebuetow](https://twitter.com/mikebuetow)

P.S. A warm welcome back to [Andy Shaughnessy](#), our former editor who is returning to become our first content architect! Be sure to say hi to him at [PCB East](#) this year. The annual conference (registration is open) and exhibition takes place April 28-May 1, at the [DCU Center](#) in Worcester, MA. Sign up now!

MIKE BUETOW is president of PCEA ([pcea.net](http://pcea.net)); [mike@pcea.net](mailto:mike@pcea.net).

# REDUCE PROGRAMMING TIME AND DEFECTS WITH YAMAHA'S AI ENHANCED AOI

**YRF-V**

Yamaha can meet the challenges of almost any product that is on the market today.

**DON'T MISS THE OPPORTUNITIES FOR THESE NEW TECHNOLOGIES!**

Learn more at [www.yamaha-motor-im.com](http://www.yamaha-motor-im.com)

For inquiries: [y-sales@yamaha-motor.com](mailto:y-sales@yamaha-motor.com)

See us at APEX

Booth #1842

- + Fastest 3D Automated optical inspection on the market today!

- + Resolution for narrow pitch 0201mm devices.

- + New co-axial lighting system for finding defects on reflective surfaces.

- + AI Automatic Secondary Inspection reduces false call rates and operator interaction

- + AI Based **Automatic Data Generation and Auto Component Programming** dramatically reduces the time to create new inspection tasks.

SCAN THE QR CODE®

FOR MORE INFO

Messaging and data rates may apply.

**YAMAHA**

*Rev's Your Heart*

# Siemens Acquires Aster Technologies to Expand PCB Test Engineering Capabilities

PLANO, TX – Siemens has acquired Aster Technologies, a provider of printed circuit board assembly test verification and engineering software, expanding its capabilities in design for test and manufacturing readiness for complex electronic systems. Financial terms of the transaction were not disclosed.

The acquisition brings Aster's shift-left DfT and test coverage analysis into Siemens' Xpedition and Valor software portfolios, part of the Siemens Xcelerator platform. The integration is intended to help electronics manufacturers identify test coverage gaps earlier in the PCB design process.

By combining Aster's test engineering tools with Siemens' existing design for manufacturing capabilities in Valor and PCB design workflows in Xpedition, Siemens aims to strengthen the digital connection between PCB design, assembly and test.

Siemens said the move addresses increasing test challenges driven by higher electronics complexity, including advanced automotive systems, 5G integration and denser PCB assemblies.

# Unitech PCB Establishes First Thailand Manufacturing Base in Thailand

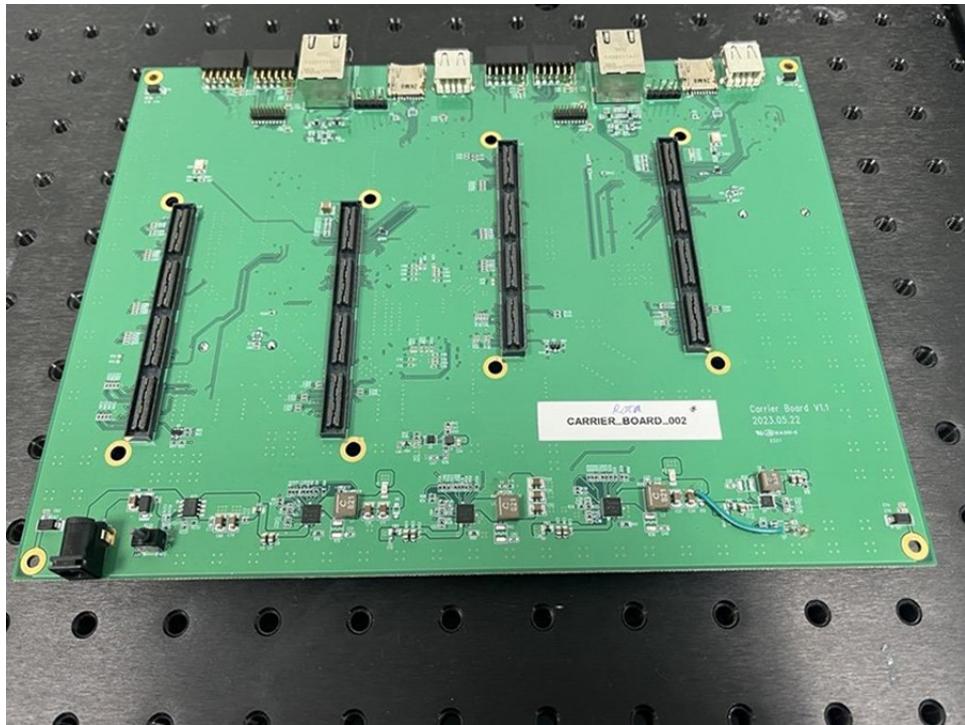

BANGKOK – Unitech PCB has opened its first manufacturing facility in Thailand, establishing a new production base at the S Ang Thong Industrial Estate.

The facility spans approximately 8.4 hectares and will support production of HDI printed circuit boards for export markets. The site is intended to serve as a regional manufacturing hub as Thailand continues to expand its role in the global PCB supply chain.

Unitech PCB's new manufacturing facility in Thailand.

Thailand is currently the largest PCB manufacturing base in ASEAN and ranks fifth globally, supported by established electronics infrastructure, an experienced workforce, and export-oriented industrial policies. The addition of Unitech's facility increases regional capacity for advanced PCB fabrication as manufacturers continue to diversify production across Southeast Asia.

## Defu Abandons Circuit Foil Luxembourg Deal

WILTZ, LUXEMBOURG – Chinese copper-foil manufacturer Jiujiang Defu Technology has abandoned its planned acquisition of Circuit Foil Luxembourg after Luxembourg authorities imposed conditions that would have prevented Defu from obtaining operational control of the company.

The transaction, announced in July and valued at approximately \$190 million, was subject to foreign investment screening due to Circuit Foil Luxembourg's strategic role in Europe's electronics supply chain. Defu said regulators would only approve a minority ownership structure, with limited voting rights and no authority over management decisions.

According to Defu, the imposed conditions also restricted influence over corporate governance, intellectual property, trade secrets, and other sensitive operational areas, fundamentally altering the scope of the deal. As a result, the company opted to terminate the agreement.

The acquisition was reviewed under Luxembourg and European Union foreign investment regulations. Luxembourg's Ministry of the Economy confirmed that it issued a conditional authorization on Jan. 8, but declined to disclose further details, citing confidentiality requirements related to critical industries.

Following the termination, Defu said it plans to refocus its expansion efforts within China. The company announced its intention to pursue a 51% stake in Huiru Technology, a domestic producer of electrolytic copper foil with annual capacity of approximately 20,000 tons. Transaction pricing will be determined following completion of due diligence.

## Zhen Ding Technology to Launch Thailand JV, Add to PCB Fab Capacity

**BANGKOK** – Zhen Ding Technology plans to expand its printed circuit board manufacturing presence in Thailand through a joint venture with Saha Pattana Interholding following government approval of more than \$2 billion in new PCB fabrication investments.

According to Thai authorities, the approved projects will add PCB fabrication capacity tied to Zhen Ding's existing Thailand campus, which began operations last fall. The new investment is expected to support large-scale production expansion as global PCB manufacturers continue to diversify manufacturing footprints in Southeast Asia.

Zhen Ding Technology is partnering with Saha Pattana Interholding, a publicly traded Thai investor and industrial park developer, on the project. The specific location of the new facilities was not disclosed.

The Thai government said the investment is expected to create approximately 5,600 jobs.

## Hanza to Acquire EMS Provider BMK Group

**GERMANY** – Hanza in January completed its previously announced acquisition of BMK Group in a share-for-share transaction, expanding its European EMS footprint and adding scale in complex, high-reliability electronics manufacturing.

The transaction values BMK at approximately \$193 million, based on Hanza's share price at signing. Under the agreement, BMK's three founders are expected to own about 27% of the combined company following completion.

The joint company has annual revenues of about SEK 10 billion (\$1.05 billion) and 5,000 employees.

BMK is a European electronics manufacturing services provider focused on high-reliability and complex electronics, with operations in Germany, Israel, the Czech Republic, and China. The company was expected to generate revenue of approximately SEK 3.3 billion (\$350 million) in 2025, with an operating margin of about 7.3%. Its services include engineering, prototyping, industrialization, manufacturing, testing and lifecycle support for industrial, medical and defense customers.

The acquisition significantly increases Hanza's presence in Germany, which is expected to become the group's largest operating cluster.

# Voltatron Acquires Komitec

FÜRTH, GERMANY – Voltatron AG has acquired 100% of Komitec Electronics, expanding its electronics manufacturing services capabilities and adding capacity as part of its acquisition-led growth strategy. The transaction closed on Jan. 1.

The merged company will have 2026 revenue in the range of €47 million to €51 million (\$55 million to \$60 million) and an adjusted EBITDA margin between 7% and 10%.

Voltatron said the acquisition extends its value chain by adding electronics research and development capabilities alongside medium- and large-scale production capacity for electronic assemblies, devices, and systems. The deal also broadens the company's customer base and more than doubles available production space, increasing operational flexibility and redundancy.

The transaction includes a cash component as well as the issuance of new shares through a capital increase against contribution in kind. As part of the agreement, Komitec managing director Jochen Schmitt-Ruenhorst will remain in his role and become a long-term shareholder in Voltatron to support continuity and integration.

## Foxconn Acquires Belkin and Subsidiary Brands for \$866M

TAIPEI – Foxconn Interconnect Technology Limited (FIT), an affiliate of Foxconn, has agreed to acquire Belkin International for \$866 million. The deal brings Belkin and its subsidiary brands, Linksys, Wemo and Phyn, under FIT's ownership.

The acquisition represents the first major move by FIT into operating established consumer brands, following a history focused on manufacturing and interconnect solutions. While the agreement has been signed, the transaction remains subject to approval by the US Committee on Foreign Investment, a process that has drawn heightened scrutiny following the US government's prior intervention in high-profile semiconductor and technology mergers.

Belkin founder and CEO Chet Pipkin will continue to lead the company, which will operate as a subsidiary of FIT following the transaction. "This move will accelerate our vision of delivering technology that makes the lives of people around the world better, more convenient and more fulfilling," Pipkin said. He added that the transaction provides access to additional manufacturing resources and capital to support operational efficiency and future investment.

## Inventec Commits \$136M to Expand Thailand Footprint

TAIPEI – Inventec plans to invest approximately \$136 million to expand production capacity at its Thailand operations, reflecting accelerating demand from US customers shifting notebook manufacturing from China.

The investment will fund a combination of plant renovations, equipment upgrades, and the construction of a new factory and supporting infrastructure. Roughly \$54 million is allocated for facility improvements and equipment, while about \$82 million will be used to build the new production site.

The Thailand expansion is designed to support both notebook and server manufacturing. Demand from US clients has increasingly driven notebook production outside China, prompting higher utilization at both leased and company-owned facilities in Thailand.

While China remains the largest manufacturing base, Thailand now represents a low double-digit share of total notebook shipments, signaling a growing role in the company's global supply chain diversification strategy.

In the artificial intelligence server segment, most production continues to be based in Taiwan. A US manufacturing facility in Texas is scheduled to begin operations by the end of the first quarter, with mass production expected in the second quarter, positioning the company closer to North American customers.

## Mycronic Acquires German PCB Test Probe Supplier ETZ

STOCKHOLM – Mycronic's Global Technologies division has acquired ETZ, a German manufacturer of test probes used in electrical testing of bare printed circuit boards.

ETZ supplies the majority of test probes used by the PCB test business line within Global Technologies, making probe development and production a core strategic capability. The company employs 34 staff and operates its manufacturing facility in Seesen, Germany.

In 2025, ETZ reported net sales of about \$4.3 million, with roughly 85% of revenue generated from sales to Mycronic. Prior to the transaction, Mycronic held a 15% ownership stake in ETZ.

Following the acquisition, ETZ will be fully integrated into the PCB test business line within Global Technologies.

## PCD&F

**American Standard Circuits** and **Sunstone Circuits** unified under the **ASC** brand family, introducing a refreshed corporate identity. The fabrication also added a high-precision via fill machine to its Oregon facility.

**Amazon** entered a partnership with **Rio Tinto** to source copper for data center components.

**Dynamic Electronics** said it will double its investment in its Thailand PCB manufacturing plant.

**Pinnacle Technology Group** rebranded as **PTG Electronics**, introducing a new name and visual identity.

**Schweizer Electronic** completed the sale of a 15% stake in its Jiangsu subsidiary to **Wus Printed Circuit**.

**Taiyo Nippon Sanso** plans to build an Advanced Electronics Materials Development Building, scheduled for completion in March 2027.

**TSMC** is accelerating its Arizona expansion, with 3nm mass production now expected to begin as early as 2027.

**Wus Printed Circuit** said it will invest \$300 million to develop and mass-produce high-density optoelectronic integrated circuit boards for AI computing and autonomous driving.

## CA

**Absolute EMS** formed a strategic partnership with **SIIIX USA** to provide production support within SIIIX's global manufacturing network.

**Amber Enterprises India** completed the acquisition of a majority stake in Pune-based **Shogini Technoarts**.

**Axos Designs** acquired a 30,000-sq. ft. manufacturing facility in Long Island City, NY.

**Distron** became the first US electronics manufacturer to deploy **Keiron's** HF2 LIFT-based precision solder paste printing technology.

**EDAC** registered with **PEZA** to establish an export-oriented electronics manufacturing hub in New Clark City, Philippines.

Mozambique broke ground on its first dedicated electronics assembly factory.

**Rohde & Schwarz** opened a larger Osaki office to expand automotive test, calibration, and local engineering support in Japan.

**SRC Technologies Group** secured a \$1 million grant from **Missouri State University's** Jordan Valley Innovation Center to build a low-volume, high-mix electronics assembly line.

**VDL Groep** acquired **Sintecs** to strengthen its electronics manufacturing capabilities.

**Yamaha Robotics** integrated its German liaison office into **Yamaha Motor Europe's** robotics business.

# Move Beyond the Fixture – ....To Greater Flexibility and Cost Savings with TAKAYA!

Eliminate slow, costly test fixturing for PCBAs with the automated flexibility of TAKAYA Flying Probe testing.

It's the best choice for high-mix assembly. No high costs and needless delays. ECOs?

No problem - no new fixture is needed, just a simple programming change.

Plus, TAKAYA has the full path to complete flying probe test automation with 4.0 level line integration, communications, and near-zero operator assistance.

- Ultimate Flexibility for High Mix, Medium Volume Assembly

- No High-Cost Fixturing

- Fast ROI

- Single or Double-sided PCBAs

- Shipped from/serviced in the U.S. by TEXMAC USA.

## PCDF

Don Cantow

Panos Angelopoulos

Sarmad Khemmoro

Altium appointed **Don Cantow** general manager.

Anduril named **Steve Mueller** printed circuit board designer.

Optical Gaging Products appointed **Panos Angelopoulos** president of global sales.

EIPC elected **Rico Schlüter** president and elected as vice presidents **Emma Hudson** of EHTC and **Thomas Michels** of Ilfa.

Siemens promoted **Sarmad Khemmoro** to senior director of product strategy for Electronics & Semiconductor.

## CA

Angel Lopez

Ray Whittier

Josh Hollin

Jan Janick

Jonathan Molina

Casey Cooper

Tony Jepson

Greg Rowell

Barbara Koczera

AIM Solder appointed **Angel Lopez** technical support engineer for North America.

BAE Systems promoted **Ray Whittier** to operations affordability lead.

Benchmark named **Josh Hollin** senior vice president and chief technology officer.

Benchmark Electronics chief technology officer **Jan Janick** retired in January.

Jabil named **Jonathan Molina** engineering manager.

Koda Technologies named **Casey Cooper** director of digital engineering.

Libra Industries appointed **Tony Jepson** general manager of its Dallas, TX, electronics manufacturing facility.

Libra Industries named **Greg Rowell** global director of continuous improvement.

Microboard promoted **David Kleffman** to vice president, Engineering Solutions & Technology.

Texmac-Takaya Group named **Barb Koczera** Western regional sales manager.

Z-Axis promoted **Danielle Sklepik** to design engineering manager at its Phelps, NY, facility.

See us at APEX

Booth #1831

# Small. Powerful. Efficient.

Reduce selective soldering floor space usage by up to 60% with SELECT Synchro and scale your production floor's potential.

**What will you do with

all that floor space?**

**Nordson** *Electronics Solutions*

# Conference Registration Opens for PCB East 2026

PEACHTREE CITY, GA – PCEA has opened registration for the technical program for [PCB East 2026](#), featuring more than 80 hours of in-depth electronics engineering training on circuit board design and assembly.

Rick Hartley, Susy Webb, Stephen Chavez, Karen Burnham and Tomas Chester are among the headliners of this year's conference. It will be held Apr. 28 to May 1 at the [DCU Center](#) in Worcester, MA. It features classes for every level of experience, from novice to expert.

The scope of classes ranges from the basics of design engineering, libraries and circuit grounding to more advanced fare such as power distribution, EMC, stackups, thermal management and DDR memory routing.

More than two-thirds of the presentations are new to the conference, including ones on DfM for ultra high-density interconnects (UHDI), designing in 3-D, advanced dielectrics for thermal PCBs, AI and time budgets for new projects.

New this year are two days of assembly tracks, offering in-depth circuit assembly basics and advanced assembly, including an all-day hand soldering workshop, plus a full day of supply chain and business management sessions.

The all-day Executive Management Forum on Apr. 28 will cover executive strategies for AI adoption, meeting workforce challenges and new PCB process selection for advanced electronics packaging.

“PCB East is the largest technical conference and exhibition for the electronics design, fabrication and assembly industry on the East Coast,” said Mike Buetow, conference director, PCB East. “This year’s event offers an array of experts in printed circuit design engineering and manufacturing, and a new emphasis on assembly.”

Registration for both the technical conference and the exhibition takes place at [pcbeast.com](#). Those who sign up by Mar. 27 can take advantage of the early bird special discounts for the conference.

## PCEA Names Andy Shaughnessy Content Architect

PEACHTREE CITY, GA – PCEA in January named Andy Shaughnessy its first content architect. Shaughnessy, a veteran industry journalist and media personality, will be responsible for creating and overseeing PCEA's technical publications and media communications, including podcasts and video.

Shaughnessy has been a writer, editor and journalist for 30 years. He has been covering PCB design and the EDA market since 1999, serving as associate editor and editor-in-chief of PCD&F Magazine from 1999-2007, prior to its acquisition by PCEA.

From 2007-2025, he was editor of I-Connect007's Design007 Magazine and the Design Newsletter, as well as an on-camera interviewer for the *Real Time* video program.

"Once we realized Andy was available, a reunion was obvious," said Mike Buetow, president, PCEA. "Our vice president of sales and marketing, Frances Stewart, and I worked with Andy years ago and have always been impressed with his passion, knowledge, and ability to connect with people of all backgrounds and responsibilities. We are thrilled to have him as a colleague again."

"I'm excited to be back working with Mike and Frances," Shaughnessy said. "Although some of the team is different, I know everyone in the company. How often do you get to start a new job at a company where you've known everyone for decades?"

Andy Shaughnessy

## Spring PCB Design Training Classes Scheduled

PEACHTREE CITY, GA – Registration is open for the PCEA Training Certified Professional Circuit Designer (CPCD) training and certification classes this spring.

Class dates are May 15, 22, 29, Jun. 5 and 12. Registration closes Apr. 16.

The 40-hour instructor-led course is designed for printed circuit engineers, layout professionals and other individuals currently serving in the design engineering industry or seeking to get into it.

The classes cover the gamut of printed circuit design engineering, from layout, place and route to specifications and materials to manufacturing methods. Schematic capture, signal integrity and EMI/EMC are also part of the comprehensive program.

Each class includes a copy of *Printed Circuit Engineering Professional*, a 400-page handbook on circuit board design, and the optional certification exam recognized by PCEA.

There are no prerequisites to enroll. Classes are held online and led by experienced instructors.

To enroll, visit [pceatraining.net/registration](http://pceatraining.net/registration).

## PCB East Show Floor 95% Sold Out

PEACHTREE CITY, GA – The exhibition hall floor space for [PCB East](#) 2026 is more than 95% sold out.

The annual one-day exhibition will be held April 29, 2026, at the DCU Center in Worcester, MA. The exhibition is part of the [PCB East](#) conference, which takes place April 28 – May 1.

“We have seen tremendous interest this year, owing in part to our past history of turnout coupled with the move to the DCU Center, which is a high-end facility and offers big-city advantages at a more affordable cost to attendees,” said Frances Stewart, vice president of sales and marketing at PCEA.

“Several major semiconductor companies such as AMD, Lattice Semiconductor, Microchip and Samtec are joining our traditional group of leading software developers and manufacturers as we build on our industry-leading events for electronics design and manufacturing,” she added.

Companies interested in exhibiting should contact Frances Stewart at [frances@pcea.net](mailto:frances@pcea.net) for details.

For more information about [PCB East](#), visit [pcbeast.com](http://pcbeast.com)

### PCEA CURRENT EVENTS

### ASSOCIATION NEWS

**Certification.** The following recently passed the PCEA [Certified Printed Circuit Designer](#) exam:

- Dr. Amar Basu

- Ernesto Esparza

### New Corporate Members

- [Polyonics](#)

**Conferences.** PCB Detroit will return to the campus of Wayne State University on Jun. 15-16, 2026. More details will be forthcoming at [pcea.net/events](http://pcea.net/events).

**Networking.** The PCEA Discord server brings together engineers and designers from around the world on a private channel to discuss technical questions and career opportunities. To join, contact [PCEA](#). Recent conversations covered high voltage boards, reflowing through-hole components, and differential signals.

## CHAPTER NEWS

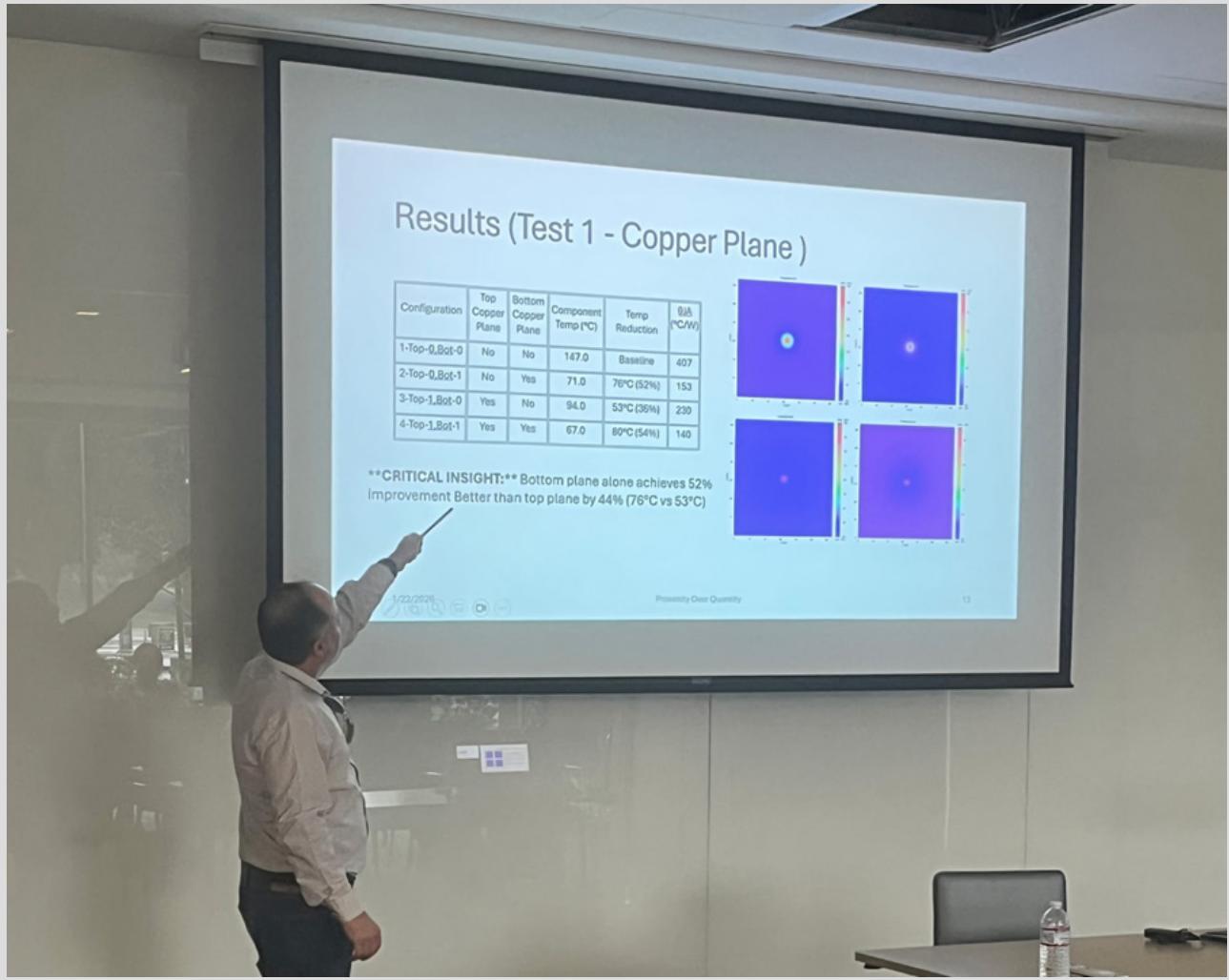

**Orange County.** Our January meeting featured design guru Ulisses Castro on the topic “Proximity Over Quantity: How Copper Plane Placement Outperforms Thermal Via Count in QFN Package Thermal Management.” Thanks to Siemens for hosting.

Ulisses Castro describes copper plane test results at the Orange County chapter meeting.

**Portland, OR.** Our January meeting featured Anaya Vardya, president and CEO of American Standard Circuits, presenting on Thermal Management of PCBs, offering a unique perspective from a leading PCB fabricator. This session was the latest in our ongoing discussions about thermal management, providing valuable insights into real-world fabrication challenges and solutions that can enhance your designs. Our next meeting is Feb. 19 at 12 p.m. Pacific.

**Richmond, VA.** Our Feb. 12 meeting will be a Community Hardware Night, focused on connection, conversation, and real-world projects. Guests are welcome to bring a circuit board or hardware project they've worked on, or any other examples of the design or production of electronics. This informal gathering is designed to connect people who are involved in, or curious about, circuit board design and production. That includes designers, manufacturers, distributors, students, educators, and individuals or organizations interested in exploring how electronics design fits into their work or future plans. The time is 6-8 p.m. and the location is 1717 E. Cary St., Richmond. Come with a friend, classmate or coworker who may be interested.

Pizza will be provided by [Mobius Materials](#); RSVP on [LinkedIn](#) or [email Mike Burns](#).

# WHEN IT HAS TO WORK, THINK AXIOM ELECTRONICS

**Quality isn't just a metric at Axiom Electronics.** For many of the complex PCBAs and subassemblies we work on, failure is not an option. We provide customers with a complete electronics manufacturing services solution which includes:

- Robust NPI process ensuring all requirements are identified before project start

- DFX recommendations

- Support for prototype, pilot and production builds

- In-house automated conformal coating

- Supply chain management

- Automated traceability

- Industry-leading process control

- Comprehensive inspection and test

We are able to build to virtually any standards and specifications you choose. From Earth to Mars, our manufacturing expertise is helping our customers deploy mission critical products.

If you are looking for an EMS supplier expert in supporting the rigorous quality and device history recordkeeping requirements found in medical device manufacturing, give us a call at **503-643-6600** or visit our website at [www.axiomelectronics.com](http://www.axiomelectronics.com).

To learn more about our manufacturing processes download our latest whitepaper, "Key Areas to Audit When Selecting a Contract Manufacturer" at [www.axiomelectronics.com/ads](http://www.axiomelectronics.com/ads).

# PCB Design Software Sales Up 3.4% YoY in Q3, ESD Alliance Says

MILPITAS, CA – Printed circuit board (PCB) and multichip module (MCM) design software revenue rose 3.4% in the September quarter, reaching \$466 million, the ESD Alliance announced today.

The four-quarter moving average, which compares the most recent four quarters to the prior four, rose 8.1%.

Electronic system design (ESD) industry revenue increased 8.8% to \$5.6 billion in the third quarter, from \$5.1 billion in 2024. The four-quarter moving average rose 10.4%.

“The electronic design automation (EDA) industry continues to report strong year-over-year revenue growth in Q3 2025,” said Walden C. Rhines, spokesperson for the ESD Alliance. “All product categories reported increases, with semiconductor IP and services showing double-digit gains. Geographic regions, including Americas, EMEA and APAC reported growth in Q3, with a double-digit increase in APAC.”

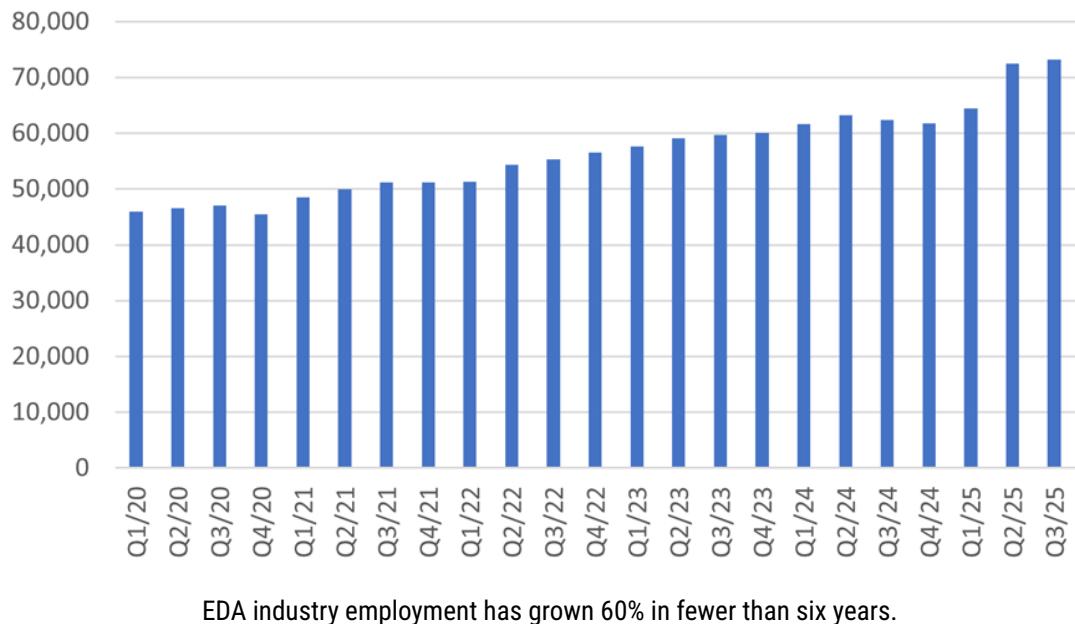

The companies tracked in the report employed 73,185 people globally in Q3, up 17.3% over 2024 and up 0.9% sequentially. It brings the sector’s total employment growth to 60% since Q1 2020 (**Figure 1**).

EDA Employment, 2020-25

Computer-aided engineering (CAE) revenue increased 9.1% to \$2.1 billion. The four-quarter CAE moving average increased 11.6%. IC physical design and verification revenue increased 1.3% to \$865 million. The four-quarter moving average for the category decreased 1.2%.

Semiconductor intellectual property (SIP) revenue increased 13.6% to \$1.92 billion. The four-quarter SIP moving average rose 14.8%.

Services revenue increased 10.2% to \$221.4 million. The four-quarter moving average rose 13.7%.

The Americas, the largest reporting region by revenue, procured \$2.4 billion of electronic system design products and services in Q3 2025, a 3.4% increase. The four-quarter moving average for the Americas rose 10.3%. Europe, Middle East and Africa (EMEA) procured \$675 million of electronic system design products and services, a 4.6% increase. The four-quarter moving average for EMEA grew 7.6%.

Japan's revenues decreased 11.5% to \$264 million in Q3. The four-quarter moving average for Japan increased 2.4%. Asia Pacific (APAC) procured \$2.2 billion, up 20.5%. The four-quarter moving average for APAC grew 12.8%.

| Computers Adding Up                                            |          |                    |                   |      |

|----------------------------------------------------------------|----------|--------------------|-------------------|------|

| Trends in the US electronics equipment market (shipments only) |          |                    |                   |      |

|                                                                | % CHANGE |                    |                   |      |

|                                                                | AUG.     | SEPT. <sup>1</sup> | OCT. <sup>P</sup> | YTD  |

| Computers and electronics products                             | -0.2     | -0.1               | 0.5               | 4.8  |

| Computers                                                      | -1.0     | 0.7                | 1.7               | 14.8 |

| Storage devices                                                | -0.2     | -5.4               | 2.4               | 9.2  |

| Other peripheral equipment                                     | -7.6     | -8.2               | 3.0               | 11.7 |

| Nondefense communications equipment                            | 2.5      | 1.7                | -1.9              | 7.6  |

| Defense communications equipment                               | -1.9     | -2.4               | 2.4               | -1.1 |

| A/V equipment                                                  | -4.5     | -3.9               | -3.3              | -4.0 |

| Components <sup>1</sup>                                        | -0.1     | -0.2               | 0.1               | 4.7  |

| Nondefense search and navigation equipment                     | -0.6     | 1.1                | 0.0               | 2.2  |

| Defense search and navigation equipment                        | 0.6      | 0.3                | 0.8               | 4.2  |

| Electromedical, measurement and control                        | 0.1      | 0.5                | 0.0               | 4.3  |

<sup>1</sup>Revised. <sup>P</sup>Preliminary. <sup>1</sup>Includes semiconductors. Seasonally adjusted.

Source: US Department of Commerce Census Bureau, Jan. 4, 2026

| Key Components                         |        |        |        |        |        |

|----------------------------------------|--------|--------|--------|--------|--------|

|                                        | AUG.   | SEPT.  | OCT.   | NOV.   | DEC.   |

| EMS book-to-bill <sup>1,3</sup>        | 1.26   | 1.31   | 1.26   | 1.17   | TBA    |

| Semiconductors <sup>2,3</sup>          | 21.7%  | 15.3%  | 27.2%  | 15.3%  | TBA    |

| PCB book-to-bill <sup>1,3</sup>        | 0.98   | 0.92   | 1.00   | 1.12   | TBA    |

| Component sales sentiment <sup>4</sup> | 113.2% | 121.6% | 122.2% | 120.1% | 134.0% |

Sources: <sup>1</sup>IPC (N. America), <sup>2</sup>SIA, <sup>3</sup>3-month moving average, <sup>4</sup>ECIA

## Hot Takes

**Worldwide shipments of desktops, notebooks and workstations** reached 279.5 million units in 2025, up 9.2% year-over-year, supported by replacement demand and a stronger second half. Q4 shipments totaled 75 million units, up 10% compared to 2024. Tightening memory and storage supply is expected to weigh on growth this year. (Omdia)

Several major memory makers are **preparing to exit DDR4** in 2026, with Samsung reportedly standing firm on its end-of-life schedule. (TrendForce)

Global **semiconductor sales** climbed 29.8% year-over-year to a record \$75.3 billion in November, with month-to-month growth of 3.5%. (SIA)

A shortage of high-quality glass cloth used in BT substrates is threatening supply stability for advanced chips. (Nikkei)

North American EMS shipments declined 0.7% year-over-year in November and fell 3.6% compared with October. Year-to-date shipments were down 0.9%. Bookings dropped 4.1% year-over-year and 9.7% sequentially. Year-to-date bookings were 0.5%. (GEA)

The global DRAM market is experiencing a rare price spike. Tight supply, rapid AI expansion, and expectation-driven buying have pushed memory prices higher since the second half of 2025. (DigiTimes)

Global PC shipments grew 9.6% year-over-year in the fourth quarter, reaching 76.4 million units. Average selling prices (ASPs) are expected to rise in 2026 as vendors prioritize midrange and premium systems to offset higher component costs, especially memory. (IDC)

India approved \$4.6 billion in subsidized electronic component manufacturing projects across eight states,

aiming to boost local supply chains, generate \$28.6 billion in output and employ about 34,000 workers. (India IT Ministry)

**Taiwan's combined onshore and offshore PCB manufacturing output** reached NT\$244 billion (\$7.73 billion) in the third quarter, a year-on-year increase of 7.2%. Cumulative output for the first three quarters totaled NT\$667 billion (\$21.1 billion), up 11.3% year-over-year. (TPCA)

**Total North American PCB shipments** increased 21.1% year-over-year in November, though volumes declined 4% sequentially. Year-to-date shipments were up 12.6% compared with the same period a year earlier. Bookings rose 23.3% from the previous year and slipped 0.7% sequentially, with year-to-date bookings increasing 16.6%. (GEA)

**India is targeting PCB self-reliance** with \$2.4 billion in investment, aiming to attract 10 to 12 major producers, cut import reliance from 88%, and support a threefold industry expansion. (Elcina)

**Delays and cancellations tied to Europe's Chips Act** are casting doubt on the EU's goal of reaching 20% of global semiconductor production by value by 2030, exposing gaps in its industrial strategy. (EUToday)

China has mandated that **chipmakers source at least 50% of equipment** domestically for new capacity. (Reuters)

**Global smartphone shipments** increased 2.3% year-over-year to 336.3 million units in the fourth quarter, raising the total number of smartphones shipped in 2025 to 1.26 billion units. (IDC)

# LEADER TAPE EXTENDERS

Boost Efficiency with TapeSplice®

Leader Tape Extenders

500 pieces per box

TapeSplice® Leader Tape Extenders provide a strong, gap-free connection between feeder and carrier tape for smooth, reliable, and continuous production.

**Strong, Reliable Bond:**

Prevents tape jams and misfeeds

**Time-Saving:**

Reduces feeder setup interruptions

**Color Options:**

Easy line organization

# The Next Great Technology Challenge: Designing without Rare Earths

As demand for AI and advanced electronics grows, the industry faces mounting pressure to reduce its reliance on scarce rare earth materials.

**MUCH HAS BEEN** written and said in all areas of the world and in all walks of life about the challenges facing the world of technology. Whether it is developing and harnessing AI (artificial intelligence), utilizing electric vehicles, reducing pollution to leave a smaller carbon footprint, or training the next generation of employees to fill the multitude of jobs required to manufacture the advanced technologies that all the above will require, the number and magnitude of all these challenges is staggering. It is nothing, however, compared to the granddaddy of them all: creating the next generations of technology without depleting rare earth minerals.

Rare earths are front-page news today, but regrettably the focus is more toward geopolitical wrangling among countries that have them and those that do not. But all the saber-rattling among competitors fails to address the root challenge: how can new technologies be developed that perform the functions we want while using far less – or no – rare earths?

First, what are rare earth minerals? They include minerals that most people have heard of, such as cobalt, lithium, manganese, graphite, and silicon derived from quartz. There are far more than those, however, most with names that are hardly household: neodymium, praseodymium, dysprosium, terbium and samarium, to name a few, are among the ones used to form industrial-quality magnets, sometimes for high-heat applications. These can be found in the battery of just about any hybrid or electric vehicle.

And then there are rare earth elements, such as yttrium, europium, cerium, lanthanum and gadolinium among them, each used in different applications ranging from LED television and smartphone screens to MRI displays. Besides these rare earth minerals/elements, there is ever-increasing demand for other critical metals such as copper, silver, gold, indium and nickel.

By leveraging the above, advanced technologies have been developed and refined into highly manufacturable devices. As the name indicates, however, “rare” earth minerals, elements and metals are limited in supply and require a disproportional effort to extract and refine. When “rare” is combined with “disproportional effort,” and then “geopolitics” is added, the mix is a problematic combination that at some point will warrant a full-court press to meet the challenge of developing new technologies that do not deplete rare earths, are easier to extract, and reduce geopolitical saber-rattling for all concerned.

While replacing rare earth minerals in electronics and technology is an increasing challenge, it by no means will be a quick or easy process, especially if Big Tech is less concerned than it should be. This challenge, to me, is eerily similar to the late 1990s when the European Union (EU), via edict, banned lead in most electronics. Industry screamed it could not be done, but then the R&D commenced, and within a decade, lead was virtually eliminated from electronics. The only difference between then and now is that there is no entity like the EU to decree it shall be done.

Another similarity to the lead-free electronics initiative is the number of end-applications and industries – from critical high-reliability aerospace and military systems to consumer-oriented fare – competing for rare earths. Back in the 1990s, aircraft and autos were beginning to become electronics-rich. The demand for personal computers and cellphones was exploding, and telecommunications and server growth were exponential. Today, electronic vehicles of all types and sizes, home and garden tools powered by batteries, and server farms to support AI are all growing leaps and bounds, growth that looks to continue in the foreseeable future. All of this puts more demand for rare earths.

Possibly, the current geopolitical environment will result in a gauntlet being thrown down. Too often in contemporary politics, it is “ready, shoot, aim,” and if that approach results in rare earths being accessible to only a few countries, technologies that do not require them will then need to be developed. With hope, it will not come to that, and entrepreneurial technologists will see benefits that warrant the herculean effort to design out rare earth minerals.

However, as we all think about the challenges we have and the resulting opportunities they may create, replacing rare earth minerals in electronics and technology in general should be high on the list. High on the list of challenges and needs, but equally, it should be high on the list of opportunities that will create future profitability and the well-being of the planet.

**PETER BIGELOW** has more than 30 years' experience as a PCB executive, most recently as president of FTG Circuits Haverhill; [peterbigelow@msn.com](mailto:peterbigelow@msn.com). He is vice chair of the PCEA PCB Management Symposium, taking place April 28 at [PCB East](#).

# A Total PCB Solution from a Single Manufacturing Partner

Rigid. Flex. Rigid-Flex. HDI. RF. Assembly.

Aerospace &

Defense

Consumer

Electronics

Quantum

Computing

Space

Automotive

Semiconductor

Medical

Summit Interconnect is the largest, privately held PCB manufacturer in North America offering a broad range of advanced technology PCBs.

We work alongside customers to push the boundaries of what is possible, helping to create inventive and transformative electronic products.

Quote Your Project Today

[www.summitinterconnect.com](http://www.summitinterconnect.com)

877-264-0343

Elevate

Your PCBs

# Do You Have a 2026 PCB Buying Strategy?

A PCB buying strategy shifts focus from unit price to total cost, design discipline and supplier governance.

**THIS IS *NOT*** the year for buyers to accept PCB price increases blindly. This is the year to buy PCBs like a professional who understands the job isn't just about placing orders; it's about controlling total cost of ownership while protecting delivery, quality and continuity.

Here's how I believe board buyers should approach 2026, including what to change in your quoting process, how to structure your supplier base and how to use logistics and design to reduce costs. These are concrete buyer moves you can implement immediately.

**Stop comparing PCB quotes and start comparing total cost of ownership.** Most buyers still shop boards like it's 2019; i.e., comparing unit prices, choosing a vendor and putting off dealing with shipping and tariffs until later. In 2026, that approach will have your company bleeding money.

Assuming the quality and delivery are the same with every vendor, the total cost of ownership (TCO) for PCBs is

$$\text{Board price} + \text{Freight to deliver} + \text{Tariff impact} = \text{TCO}$$

Then buyers should require every PCB quote to clearly spell out three things: board price, logistics and tariff assumptions.

Board pricing should be quoted Ex-Works or FOB origin and include unit pricing at the requested volume, two to three realistic volume breaks, and separate line items for NRE and electrical test.

Logistics should be quoted across multiple scenarios – standard air (three to five days), air cargo (five to 10 days) and, where timing allows, sea freight (five to eight weeks).

Finally, tariff and duty assumptions must be explicit, including the country of origin and the value basis being used to calculate any applicable tariffs.

Why should you insist on this? Because some board suppliers will get creative as they may try to win a quote by shifting money between a low unit price that has a high freight cost, a lesser tooling charge with an inflated production price or tariff costs applied to the wrong incoterm, costing you more unnecessarily. This detailed comparison among your vendors will make pricing fair and transparent.

**Your biggest cost lever in 2026 is design discipline, not negotiation.** You can negotiate a few percentage

points off PCB pricing, but a design change can remove 10–25% from the right boards, especially when metal and laminate prices are climbing.

I'm not advocating mass redesigns. I'm telling you to create a targeted, buyer-led cost-takedown program with engineering on the small set of part numbers that drive most of your annual spend.

How? Build a “top 10 cost takedown” list. Start by identifying your top 10 PCB part numbers by annual spend or margin sensitivity, then run a structured review with engineering and your primary fabricator. The sooner this happens, the more leverage you have.

Copper is usually the first place to look. Too many designs carry extra copper simply because they always have. Challenge whether heavier copper is required everywhere, or whether localized thermal performance can be achieved through stitching vias or layout changes. It's also worth revisiting hole wall copper requirements; many are legacy specs that haven't been questioned in years.

Surface finish is another quiet cost driver. ENIG should not be the default. In many cases, OSP or HASL will meet assembly requirements just fine, and hard gold fingers often get specified out of habit rather than necessity. Buying premium finishes because “that's what we've always done” is one of the most expensive mistakes buyers make, especially when gold prices move, as they inevitably do.

Layer count deserves equal scrutiny. If you have repeatable six-layer designs that could realistically be engineered into four-layer versions, 2026 is the year to explore it. Reducing layer count lowers laminate and copper usage and can improve yields. Not every design will qualify, but even one or two high-volume parts can produce meaningful savings.

Quotes should also include the panel drawing and utilization percentage. Excessive rail width, inefficient panelization, or a fabricator that doesn't volunteer a better layout can quietly inflate cost. In those cases, you're paying for air and scrap rather than boards.

Finally, be deliberate about where X-outs are acceptable. For certain products, permitting controlled X-outs can unlock price relief during yield-challenged periods. This must be governed by part number and policy, not chaos, but it's a real lever when used correctly.

These are the distinctions between routine board buying and professional procurement. Experienced buyers don't just negotiate price; they use design discipline and acceptance policy to control cost.

Figure 1. Effective PCB procurement in 2026 depends on total cost visibility, supplier discipline and structured buying strategy.

**Build a vendor bench and use it, even if you don't want to switch.** Let me be blunt: if you only quote your incumbents, you are training them to raise prices with confidence. (Buyers: repeat this line again to yourself out loud.)

In 2026, every serious PCB buyer needs to maintain two qualified production sources for each core technology bucket that accounts for 60% of your business, and two quote-ready challengers to keep warm with the 40% balance of your spend.

Quoting is not betrayal. Quoting is governance.

**Quoting "for fun" is a 2026 survival tactic.** Even if you're happy with your vendor, quote competitors. Why?

- It validates your current pricing (best case).

- It forces your incumbent to stay sharp (most common).

- And sometimes you discover a better fit – price, lead time, service – without even trying.

**Visit key suppliers and make sure they know you're watching.** Supplier visits aren't just about relationship building. They are more about operational oversight. The greater the annual spend with a vendor, the more likely you are to see them, *even if* they are halfway around the world.

The worst thing a buyer can say is "I didn't know you could build that." Knowing what a vendor can and cannot do will save you money, along with the associated headaches that come with supplier ignorance.

This is how you go into 2026 with a plan instead of a prayer. By carrying out these steps, 2026 becomes an opportunity, a year when disciplined PCB buyers separate themselves from mere order placers. And your company will be one of those with a real buying strategy, protecting your margins while everyone else complains about price increases.

**GREG PAPANDREW** has more than 25 years' experience selling PCBs directly for various fabricators and as the founder of a leading distributor. He is cofounder of DirectPCB ([directpcb.com](http://directpcb.com)); [greg@directpcb.com](mailto:greg@directpcb.com).

We are committed to advancing technology

through shared knowledge

and collective excellence.

# Thank You!

PCEA CORPORATE MEMBERS

**Collaborate** across the electronics industry,

**Educate** future innovators, and

**Inspire** a global community of professionals.

*Join Us!*

# Dashboards and Controlled Chaos

In an EMS environment built on controlled chaos, dashboards help program managers catch problems early and keep accounts on track.

THE ELECTRONICS MANUFACTURING services (EMS) industry is controlled chaos by design. The basic EMS value proposition is that outsourcing relieves original equipment manufacturers (OEMs) of manufacturing challenges. The EMS provider covers fixed costs during manufacturing and carries the associated inventory costs on its balance sheet. Market slowing down? Revise your EMS provider's forecast. Market improving? Tell your EMS provider to pull some production in. Engineering challenges? Send your EMS provider a set of engineering change orders (ECOs) as the team determines what needs to change. The OEM side of the equation has the chaos part of the business model down. Even when things are running smoothly, the number of unplanned emails and calls in keeping projects on track is a significant part of the program management team's daily activities. When more of the day gets consumed than planned, activities designed to control the chaos may not get done.

This underscores the importance of having a control system that makes sense for managing that chaos. Walk a production floor, and you'll see control limits established for critical processes such as solder paste deposition and reflow. If a process exceeds those limits, either the monitoring software in that equipment or the inspection equipment immediately following that process tells the operator a problem has developed so that the operator can identify the root cause and bring it back within control limits before significant amounts of defective products are built. Program managers need to create control systems that provide that intelligence as well. A dashboard is an effective way to highlight developing issues when they are small.

The basics of a good dashboard include:

- **It educates.** You can't expect customers to change behavior if you can't show them why that behavior is costing them unnecessary money. Dashboards need to be data-driven, and those data need to be able to support the program manager's business case.

- **It needs to highlight exceptions.** We have the power to automate more real-time data than we can comprehend, especially in a chaotic environment. Consequently, the dashboard's control system must prioritize data requiring immediate attention.

- **It provides automated snapshots of critical account metrics.** The right dashboard template may vary by business size or even by business type, but typically it includes quality and on-time delivery metrics, contribution margin or some other form of profitability measurement, sales to forecast, inventory trends, PPV trends and accounts receivable status. For accounts involving dedicated lines, utilization metrics may also be

included.

- **It is graphical, so trends are easy to see.** We have become a very visual society, and program management time is at a premium. A bar graph is far more meaningful than a report in showing trends. Consequently, dashboards should be visual enough that metrics can be evaluated almost immediately.

That said, a dashboard is just part of a program manager's toolkit. EMS providers don't build superior quality products by just inspecting quality in. They develop efficient processes, define inspection points within those processes where issues may be likely to occur, and adjust the process if defect opportunities or inefficiencies are developing. Program managers should envision account strategy before the dashboard and underlying control system is designed, and over time, existing dashboards should be evaluated for relevancy. What common problems are occurring in accounts? What customer behaviors are creating unnecessary costs? What issues tend to slip under the radar until they create big problems? What goals are being set for the account by either the customer or the EMS provider? How will dashboard metrics be used in changing that dynamic? How frequently do those metrics need to be measured? Which timeline view is most effective for understanding trends in each metric? In short, design the tool with the end-users in mind. Automate the data collection process so it occurs at an appropriate frequency and then use the data to drive actions within the account.

As we begin a new year, take the time to evaluate whether the dashboard currently used or the lack of a dashboard is making it difficult to control chaos. Technology improves daily. AI adds significant options for fast trends analysis and exception reporting. Most importantly, consider whether account control activities are based on an issues-driven, reactive approach or on a clear strategy to help the customer understand the elements of an optimal relationship. The time invested in developing a partnership strategy for each account, along with the tools needed to track when the relationship is trending out of control, pays for itself in less chaos.

---

**SUSAN MUCHA** is president of Powell-Mucha Consulting Inc. ([powell-muchaconsulting.com](http://powell-muchaconsulting.com)), a consulting firm providing strategic planning, training and market positioning support to EMS companies and author of *Find It. Book It. Grow It. A Robust Process for Account Acquisition in Electronics Manufacturing Services*. She can be reached at [smucha@powell-muchaconsulting.com](mailto:smucha@powell-muchaconsulting.com).

The Electronics Industry's East Coast Conference and Exhibition

# PCB EAST 2026

Conference & Exhibition

*Conference: April 28 – May 1*

Design Track: April 28 - May 1

FPGA Track: April 29 - 30

Assembly Track: April 30 - May 1

*Exhibition: Wednesday, April 29*

DCU Convention Center, Worcester, MA

colocated with

F P G A

H O R I Z O N S

BEYOND GATE ARRAYS

REGISTRATION IS *Live*

Register Today!

Brought to you by

**PCEA**<sup>®</sup>

PRINTED CIRCUIT ENGINEERING ASSOCIATION

[pcbeast.com](http://pcbeast.com)

The Electronics Industry's East Coast Conference and Exhibition

*Exhibition: Wednesday, April 29*

*Conference: April 28 – May 1*

DCU Convention Center

Worcester, MA

## WHO'S EXHIBITING (to date)

Accurate Circuit Engineering

Adiuvo Engineering

Aldec, Inc.

All Flex Solutions, Inc.

Allspice.io

Altera

AMD

American Computer

Development, Inc. (ACDi)

ASC Sunstone Circuits

AutoPCB

BittWare

Blue Pearl Solutions, Inc.

Bowman Analytics, Inc.

Breadboard

Certiqo Ltd.

Chester Electronic Design, Inc.

Cofactr

Colonial Electronic Manufacturers, Inc.

Component Dynamics, LLC

DirectPCB

Efinix

Electronic Interconnect

Eleprint S.R.L.

EMA Design Automation

EMX US Inc.

Enclustra

ESPEC North America Inc

Fidus Systems

Fineline Global

Flexible Circuit Technologies

Freedom CAD Services, Inc.

Glory Faith Electronics Co., Ltd.

GS Swiss PCB

InstaDeep

Isola Group

JBC Tools USA Inc.

JS Circuit

K2 Engineering Services

Kayaku Advanced Materials

Lattice Semiconductor

MFG Innovations Inc.

Microchip Technology Inc.

Millenium Circuits Limited

NCAB Group

Newgrange Design

OKI Circuit Technology Co., Ltd.

PalPilot International Corp.

Panasonic Industry – Electronic Materials

PCB Technologies USA, Inc.

PCBWay

Photonics Systems USA Inc.

Polar Instruments, Inc.

Polyonics Inc.

Precision Circuit Technologies

Printed Circuit Engineering Assoc. (PCEA)

Quantic Ohmega-Ticer

RBB

Samtec

Screaming Circuits

Setanta Holdings Ltd.

Sierra Circuits

Suntech Circuits

TCLAD, Inc.

The Test Connection, Inc.

Trylene Inc.

T-Tech, Inc.

Xiphera

XJTAG

Zenode

# Rebuilding America's Electronics Backbone, One Member at a Time

The PCBAA is on a mission to ensure domestic security via a revitalized American manufacturing base.

**ACROSS THE UNITED** States, a quiet but urgent realization has been taking shape – one that echoes through defense briefings, aerospace reviews, medical device evaluations and critical infrastructure planning sessions. The nation that once led the world in electronics manufacturing now faces a stark truth: the ability to design and manufacture advanced electronics on domestic soil has diminished to dangerous levels.

This isn't speculation. It's not a theory. It's a matter of national security.

Again and again, leaders across government and industry have expressed the same concern: A country that cannot build its own electronics cannot secure its own future.

That fundamental truth fueled the creation and mission of the Printed Circuit Board Association of America (PCBAA) in 2021. The organization exists because the stakes are no longer academic – they are strategic, economic and deeply tied to national security and resilience.

## How America Lost Its Electronics Backbone

Time was, North America's electronics factories hummed with activity. Printed circuit boards flowed off production lines. Assemblers placed components with precision. Engineers developed new materials, architectures and processes. The region was a global leader in capability, innovation and capacity.

Over several decades, however, production gradually migrated offshore. First small projects, then major programs, then entire product lines. Lower costs dictated decisions, and lower-wage regions absorbed capability at an accelerating speed. The shift was slow enough to ignore in the moment, and large enough to reshape the entire global landscape.

Today, the numbers tell the story clearly:

- The US once produced over 30% of the value of the world's PCBs.

- Now it produces approximately 4%.

- Advanced substrates and packaging – key to defense and high-performance electronics – are almost entirely absent domestically.

This erosion has left critical sectors dependent on foreign sources for the technologies that power missiles, fighter jets, space systems, medical devices, energy grids, telecommunications networks and more.

In a world where electronics are the nervous system and backbone of every modern system, losing domestic capability means losing control over reliability, quality, lead time, security and strategic independence.

## The Strategic Risk of Outsourcing Electronics

Consider what it means when a nation no longer manufactures the vital circuitry behind:

- Missile guidance

- Radar systems

- Secure communications

- Power management for spacecraft

- Implantable medical equipment

- Transportation safety systems

- Intelligence platforms

- Energy grid monitoring.

These aren't consumer gadgets. They are the pillars of national power, public safety and economic stability.

Relying on overseas production introduces unacceptable risks:

- Supply chain disruption

- Intellectual property theft

- Counterfeit component infiltration

- Geopolitical leverage

- Production delays during global crises

- Loss of technical expertise

- Reduced innovation capacity.

National security is not just tanks and aircraft. It is the ability to manufacture the electronics that makes those systems function. Without secure, domestic technology manufacturing, even the most advanced military platform is

compromised before it leaves the ground.

This reality is what drives the mission of PCBAA.

## Why PCBAA Emerged and Why it Matters

PCBAA was created at a time when the consequences of decades of offshoring had become undeniable. The nation needed a unified voice that could:

- Advocate for restoring domestic electronics manufacturing

- Educate policymakers about supply chain vulnerabilities

- Elevate the importance of PCBs and PCB assemblies

- Strengthen the infrastructure required for advanced technology production

- Support investment in US-based capability

- Connect industry leaders in a shared movement to rebuild.

The organization was not formed to maintain the status quo. It was built to change it.

PCBAA represents designers, PCB fabricators, assemblers, materials companies and equipment and testing suppliers – every essential link in the electronics manufacturing ecosystem. Its mission is to create a coordinated front capable of influencing policy, shaping national priorities, and driving real industrial resurgence.

## Membership is Momentum

In most associations, membership benefits the individual company. With PCBAA, membership strengthens the entire sector.

- Each member adds weight to national advocacy efforts.

- Each member amplifies the case for investment and reshoring.

- Each member contributes to a unified message to Congress, defense agencies and OEMs.

- North America is committed to rebuilding its electronics manufacturing capability.

This collective voice is how industries change course. It is how legislation gets written, how incentives get created, how reshoring gains traction and how new capacity becomes commercially viable.

The message becomes stronger with every company that joins.

Membership directly fuels:

1. **National security advocacy.** Educating policymakers on the risks of foreign dependence for critical electronics and pushing for incentive structures that rebuild US capability.

2. **Industry visibility and influence.** Increasing awareness among defense and commercial OEMs about the importance of choosing domestic partners.

3. **Reshoring initiatives.** Driving policies and funding that encourage manufacturers to expand U.S.-based operations.

4. **A unified industry platform.** Creating a collaborative space where manufacturers, designers, suppliers and assemblers can align on shared national priorities.

These are not abstract goals; they are foundational to America's technological future.

That is how America's electronics backbone is restored, and I encourage you to engage with the PCBA team to learn more about how to become a member today and be part of the mission. For more info, visit [pcbaa.org](http://pcbaa.org).

---

DAN BEAULIEU is a longtime management consultant to the printed circuit industry and a member of the PCBA; [danbeaulieu@aol.com](mailto:danbeaulieu@aol.com).

# Inspecting Printed Circuit Boards and Assemblies

How do inspection discipline and sampling plans decide whether a shipment ships or gets torn apart?

**BEFORE GOING INTO** PCB design, my employer was in the telecom business. I started out putting PCBs into antistatic bags, then into individual boxes with appropriate labels. A group of eight distinct boards was placed in a larger box to form a die group. The big box labeling reflected the part-dash number and revision for each board. This was called “final prep” and was the last step prior to shipping.

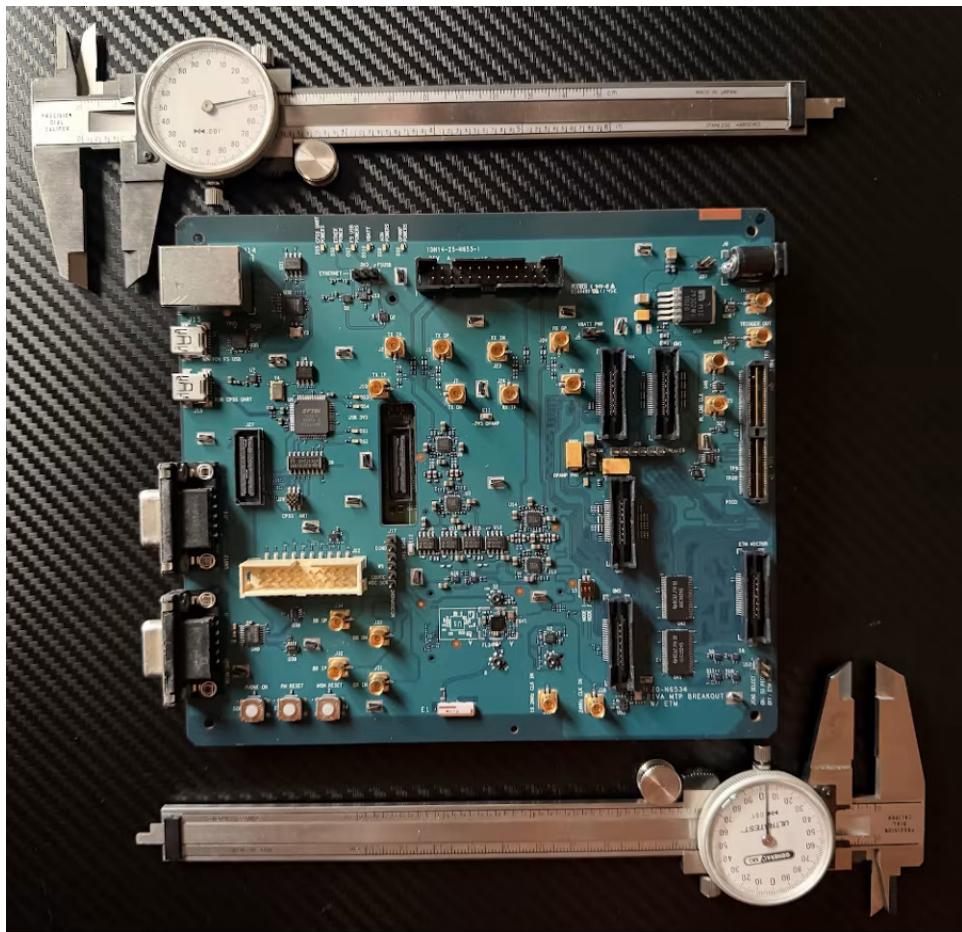

Figure 1. Dial calipers are essential for accurately measuring features on a PCB. Measuring outer or inner edges including hole sizes is possible using one end of the jaws or the other. Depth measurements use the other end of the calipers. (Source: Author)

**A few selected to represent the whole shipment.** Someone would audit the shipping boxes, looking for incorrect information on the labels and any other obvious defects. If they found a problem with the ones sampled, the entire lot would be re-examined by final prep. A missing antistatic awareness label could jeopardize the whole shipment. It could happen, especially toward the end of the quarter when we were sprinting to make our quotas.

The QC inspector and QA auditor were the last line of defense before submitting the die group to AT&T or one of the Baby Bells that came out of the antitrust settlement of 1984 that broke the phone company into several regional companies. After a few months, I transitioned to assembling card shelves and heat shields for telecom equipment racks.

Inspectors would check the card guides for burrs. They looked at everything from correct labeling to bent pins and even fingerprints. Each assembler had their own rubber stamp with their unique number. Mine was “ASSY68,” surrounded by a square in black ink. Traceability matters.

It wasn’t long before I moved to the Rack Wire and Test group, which assembled entire equipment racks. You’ve probably seen IT racks where the wiring looks like a plate of spaghetti and others that look so clean and orderly. I strove for cleanliness.

Eventually, I returned to a seated job assembling fuse/alarm panels installed at the top of the racks. The fuse panels had a 46-point wiring harness (23 wires) that wrapped around the inside of the two RU (rack-unit) enclosures. The wires were for signals, while busbars strapped all the fuses to power and ground.

I had my own way of dressing the wires into an S-turn so that the service loops to the fuses didn’t overlap. When they made me the lead assembler, I wanted all nine (plus temps) of us to take the time to form the 18-gauge wires just like mine so that it was easier to spot a mis-wire. Aside from the ASSY-number, there was no way to tell who built the fuse panel.

One day, my manager asked me if we were on “tightened inspection” – where the sample size was much higher than normal inspection. I stated that if the lot submitted to the AT&T source inspector passes, we would be eligible for reduced inspection. He shook his head and said, “You’re the only one” in the TransMUX department that is not on tightened inspection.