# PROCESSADORES PROGRAMÁVEIS

Introdução: A máquina de uso geral ou de propósito geral tem que a tarefa fica armazenada em memória e não no circuito digital. A diferença básica entre uma máquina de uso específico e uma máquina de uso geral está na unidade de controle. Uma máquina de uso específico onde o fluxo de dados é projetado de acordo com a aplicação e as microoperações são geradas pela unidade de controle de acordo com a operação a ser realizada e, portanto a máquina se torna específica para a aplicação. Para a máquina de uso geral o fluxo de dados e a unidade de controle não alteram com a aplicação e não é preciso projetar a unidade de controle. A diferença básica é que na máquina de uso geral a solução de uma aplicação é feita por instrução a instrução até que a máquina complete todo o programa da aplicação. O usuário transforma o quadro de instrução a qual ele monta para a máquina de uso específico em linhas de programa com instruções que serão executadas passo a passo pela unidade de controle no fluxo de dados.

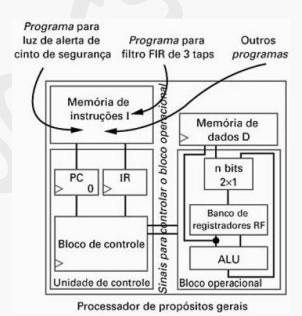

### Arquitetura da máquina de uso geral

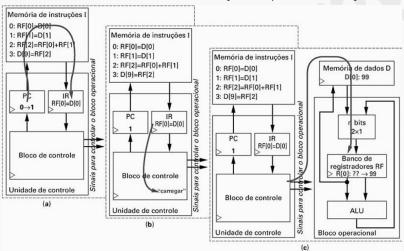

Uma máquina de uso geral é conhecida como processador cuja arquitetura interna é composta por uma unidade de controle e fluxo de dados. As instruções são colocadas na memória de instrução, onde o controlador realiza a busca para o controlador decodificar e executar. A seguir apresentamos o processador de uso geral.

#### ARQUITETURA BÁSICA:

- 1. Unidade de controle:

- 2. Fluxo de dados

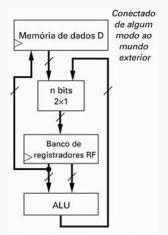

Bloco Operacional básico

- 1. Carga de dados:

- 2. Transformação de dados:

- 3. Armazenamento dos dados:

#### Memória de dados:

**Figura 8.2** Bloco operacional básico de um processador programável.

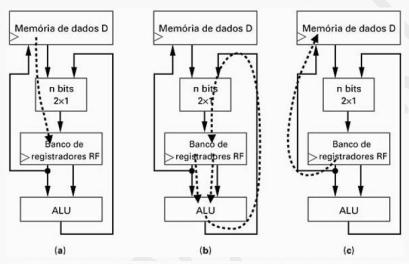

### Operações do bloco operacional -

- 1. Operação de carga:

- 2. Operação da ULA:

- 3. Operação de armazenamento:

# Arquitetura de carga e armazenamento

**Figura 8.3** Operações básicas do bloco operacional: (a) carga (leitura), (b) operações (transformações) de ALU e (c) armazenamento (escrita).

# Quais operações no bloco operacional que consomem somente 01 ciclo de relógio?

- Copiar dados de uma posição de memória, colocando-os em uma posição de um banco de registradores.

- Ler dados de duas posições de uma memória de dados, colocando-os em duas posições de um banco de registradores.

- Somar dados de duas posições de uma memória de dados e armazenar o resultado em uma posição de um banco de registradores.

- Copiar dados de uma posição de um banco de registradores, colocando-os em outra posição do banco de registradores.

- 5. Subtrair os dados, que em uma posição de um banco de registradores, de uma posição de uma memória de dados. O resultado será armazenado em uma posição do banco de registradores.

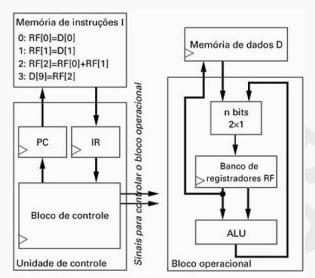

#### Unidade de controle básica:

**Exemplo:** Realizar a operação a seguir: D[9] = D[0] + D[1], no bloco operacional indicando os sinais a serem ativos nas operações realizadas. Os dados se encontram armazenados na memória de dados em determinada posição ou endereço de memória e o registrador de arquivos contém pelo menos 3 registradores internos.

#### Instruções executadas no bloco operacional

- 1.

- 2.

- 3.

- 4.

Figura 8.4 A unidade de controle de um processador programável.

### ARQUITETURA DA UNIDADE DE CONTROLE

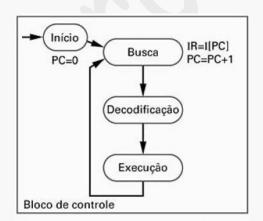

Conforme o diagrama a seguir a U.C. é responsável pela busca da instrução e a geração dos sinais de controle do fluxo de dados. São dois ciclos que a U.C. executa.

- 1) Ciclo de Busca;

- 2) Ciclo de Execução.

**1.a) CICLO DE BUSCA –** O ciclo de busca de uma instrução alocada na memória externa é realizado através do registrador contador de instruções denominado de PC. O conteúdo do PC é o endereço da instrução. O ciclo de busca é dividido em 03 microoperações a saber:

- 1) O PC endereça a instrução na memória Drive do endereço = (PC)

- 2) O PC é incrementado para a próxima busca PC= PC +1

- 3) A instrução é carregada no registrador de instrução **RI = Instrução**

**1.b) CICLO DE EXECUÇÃO -** O ciclo de execução da instrução, segue arquitetura RISC (Reduzido , onde cada execução é realizada por uma única microoperação. Cada instrução se torna desta forma uma microoperação.

A seqüência de operações realizadas pela unidade de controle para executar o ciclo de busca da primeira instrução requerem 3 ciclos de relógio a saber:

- 1. Busca:

- 2. Decodificação:

- 3. Execução:

Estágios para o processamento do ciclo de busca e execução da primeira instrução

Figura 8.5 Três estágios do processamento de *uma* instrução (a) busca, (b) decodificação e (c) execução.

Total de ciclos de relógio para a execução do programa.

# Representação por uma F.S.M. do ciclo de busca e execução.

Figura 8.6 Estados básicos do bloco de controle.

# Operação da unidade de controle:

- 1. PC = 0:

- 2. IR = I[PC]; PC = PC + 1;

- 3. RF[0] = D[0].

Ciclos de relógio = 03

Exercício: Calcular o número de ciclos de relógio para a execução do programa a seguir o qual realiza a operação: D[3] = D[2] + D[1] + D[0].

# 1. Montagem da instrução

| instrução | opcode | ra   | ra rb |      | d         | Operação              |  |

|-----------|--------|------|-------|------|-----------|-----------------------|--|

| Carga     | 0000   | 0000 | 0000  | 0000 | 0000 0000 | RF[0] = D[0]          |  |

| Carga     | 0000   | 0001 | 0000  | 0001 | 0000 0001 | RF[1] = D[1]          |  |

| Carga     | 0000   | 0010 | 0000  | 0010 | 0000 0010 | RF[2] = D[2]          |  |

| Soma      | 0010   | 0000 | 0000  | 0001 | 0000 0001 | RF[0] = RF[0] + RF[1] |  |

| Soma      | 0010   | 0000 | 0000  | 0010 | 0000 0010 | RF[0] = RF[0] + RF[2] |  |

| Armazena  | 0001   | 000  | 0000  | 0011 | 0000 0011 | D[3] = RF[0]          |  |

Sinais gerados pela U.C. na execução do programa.

| Instrução | Out_D_rd | Out_D_wr | Out_RF_s | Out_RF_w_wr | Out_RF_Rp_rd | RF_Rp_addr | Out_RF_Rq_rd | RF_Rq_addr | RF_w_addr | D_addr | ALU |

|-----------|----------|----------|----------|-------------|--------------|------------|--------------|------------|-----------|--------|-----|

| Carga     | 1        | 0        | 1        | 1           | 0            | xxxx       | 0            | xxxx       | ra        | d      | 000 |

| Soma      | 0        | 0        | 0        | 1           | 0            | rb         | 0            | rc         | ra        | d      | 100 |

| Armazena  | 0        | 1        | Х        | 0           | 1            | ra         | 0            | xxxx       | -         | d      | 000 |