# RISC-V "V" Vector Extension

Version 1.0-rc2

# **Table of Contents**

Changes from v1.0-rc1

| Various clarifications to text, and added rationale for design choices.                                                                                                         |                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Renamed vpopc.m to vcpop.m for consistency with scalar instruction. Keeping old assembler name                                                                                  | e as alias.       |

| For mask-logical instructions, and vmsbf.m, vmsif.m, vmsof.m mask-manipulation instructions, all                                                                                | <u>.low</u>       |

| implementations to write entire mask register with result (always tail-agnostic)                                                                                                |                   |

| Added vector length extensions "Zvl*".                                                                                                                                          |                   |

| Added clarification of operation of mstatus. VS field and interaction with mstatus. SD.                                                                                         |                   |

| Added definition of behavior under hypervisor.                                                                                                                                  |                   |

| <u>Clarified checking of illegal values in vtype.</u>                                                                                                                           |                   |

| Made clear that calling convention appendix here is only a placeholder to help understand the exam RISC-V psABI being expanded to contain the authoritative calling convention. | <u>ples, with</u> |

| Clarified the vxsat is in bit 0 of the CSR and that upper bits should be written as zeros.                                                                                      |                   |

| Clarified that vxrm field is in low two bits of the CSR and that upper bits should be written as zeros.                                                                         |                   |

| <u>Simplified explanations by removing text refering to option to have one element span multiple vecto</u> (ELEN > VLEN), as this is not being proposed at this time.           | _                 |

| <u>Clarified that implementations must raise illegal instruction exception for standard loads and stores</u> <u>EEWs that are not supported by the implementation.</u>          | <u>with</u>       |

| Removed Zvlsseg extension name as segment load/stores are required in all standard vector extension                                                                             | ons.              |

| Made clear that nf is encoded same as NFIELDS when used in whole register load/store instructions                                                                               | <u>).</u>         |

| Clarified that instructions with register specifiers that violate register overlap constraints are reserved                                                                     | <u>:d.</u>        |

| Added note to explain how floating-point scalar values would be handled when adding vectors to the Zfinx/Zdinx/Zhinx extensions.                                                | <u> </u>          |

| The previous assembler mnemonics vmandnot and vmornot have been changed to vmandn and vm                                                                                        |                   |

| consistent with the equivalent scalar instructions. The old vmandnot and vmornot mnemonics will                                                                                 | <u>be</u>         |

| retained as aliases in assembler.                                                                                                                                               |                   |

| Stated that misa.v is set for implementations supporting the standard V extension.                                                                                              | 0                 |

| 1. Introduction 2. Implementation-defined Constant Parameters                                                                                                                   | 8<br>9            |

| 3. Vector Extension Programmer's Model                                                                                                                                          | 10                |

| 3.1. Vector Registers                                                                                                                                                           | 10                |

| 3.2. Vector Context Status in mstatus                                                                                                                                           |                   |

| 3.3. Vector Context Status in vsstatus                                                                                                                                          |                   |

| 3.4. Vector type register, vtype                                                                                                                                                |                   |

| 3.5. Vector Length Register v1                                                                                                                                                  |                   |

| 3.6. Vector Byte Length vlenb                                                                                                                                                   |                   |

| 3.7. Vector Start Index CSR vstart                                                                                                                                              |                   |

| 3.8. Vector Fixed-Point Rounding Mode Register vxrm                                                                                                                             |                   |

| 3.9. Vector Fixed-Point Saturation Flag vxsat                                                                                                                                   |                   |

| 3.10. Vector Control and Status Register vcsr                                                                                                                                   |                   |

| 3.11. State of Vector Extension at Reset                                                                                                                                        |                   |

| 4. Mapping of Vector Elements to Vector Register State                                                                                                                          | 18                |

| 4.1.  Mapping for LMUL = 1                                                                                                                                                      | 10                |

| 4.2. Mapping for LMUL < 1                                                                                                                                                       |                   |

| 4.3. Mapping for LMUL > 1                                                                                                                                                       |                   |

| 4.4. Mapping across Mixed-Width Operations                                                                                                                                      |                   |

| 4.5. Mask Register Layout                                                                                                                                                       |                   |

| 5. Vector Instruction Formats                                                                                                                                                   | 22                |

| 5.1. Scalar Operands                                                                                                                                                            |                   |

| 5.2. Vector Operands                                                                                                                                                            |                   |

| <u></u>                                                                                                                                                                         |                   |

7

| 5.3. Vector Masking                                                        |    |

|----------------------------------------------------------------------------|----|

| 5.4. Prestart, Active, Inactive, Body, and Tail Element Definitions        |    |

| 6. Configuration-Setting Instructions (vsetvli/vsetivli/vsetvl)            | 26 |

| 6.1. vtype encoding                                                        |    |

| 6.2. AVL encoding                                                          |    |

| 6.3. Constraints on Setting v1                                             |    |

| 6.4. Example of stripmining and changes to SEW                             |    |

| 7. Vector Loads and Stores                                                 | 26 |

| 7.1. Vector Load/Store Instruction Encoding                                |    |

| 7.2. Vector Load/Store Addressing Modes                                    |    |

| 7.3. Vector Load/Store Width Encoding                                      |    |

| 7.4. Vector Unit-Stride Instructions                                       |    |

| 7.5. Vector Strided Instructions                                           |    |

| 7.6. Vector Indexed Instructions                                           |    |

| 7.7. Unit-stride Fault-Only-First Loads                                    |    |

| 7.8. Vector Load/Store Segment Instructions                                |    |

| 7.9. Vector Load/Store Whole Register Instructions                         |    |

| 8. Vector Memory Alignment Constraints                                     | 26 |

| 9. Vector Memory Consistency Model                                         | 26 |

| 10. Vector Arithmetic Instruction Formats                                  | 26 |

| 10.1. Vector Arithmetic Instruction encoding                               |    |

| 10.2. Widening Vector Arithmetic Instructions                              |    |

| 10.3. Narrowing Vector Arithmetic Instructions                             |    |

| 11. Vector Integer Arithmetic Instructions                                 | 26 |

| 11.1. Vector Single-Width Integer Add and Subtract                         |    |

| 11.2. Vector Widening Integer Add/Subtract                                 |    |

| 11.3. Vector Integer Extension                                             |    |

| 11.4. Vector Integer Add-with-Carry / Subtract-with-Borrow Instructions    |    |

| 11.5. Vector Bitwise Logical Instructions                                  |    |

| 11.6. Vector Single-Width Shift Instructions                               |    |

| 11.7. Vector Narrowing Integer Right Shift Instructions                    |    |

| 11.8. Vector Integer Compare Instructions                                  |    |

| 11.9. Vector Integer Min/Max Instructions                                  |    |

| 11.10. Vector Single-Width Integer Multiply Instructions                   |    |

| 11.11. Vector Integer Divide Instructions                                  |    |

| 11.12. Vector Widening Integer Multiply Instructions                       |    |

| 11.13. Vector Single-Width Integer Multiply-Add Instructions               |    |

| 11.14. Vector Widening Integer Multiply-Add Instructions                   |    |

| 11.15. Vector Integer Merge Instructions                                   |    |

| 11.16. Vector Integer Move Instructions                                    |    |

| 12. Vector Fixed-Point Arithmetic Instructions                             | 26 |

| 12.1. Vector Single-Width Saturating Add and Subtract                      |    |

| 12.2. Vector Single-Width Averaging Add and Subtract                       |    |

| 12.3. Vector Single-Width Fractional Multiply with Rounding and Saturation |    |

| 12.4. Vector Single-Width Scaling Shift Instructions                       |    |

| 12.5. Vector Narrowing Fixed-Point Clip Instructions                       |    |

| 13. Vector Floating-Point Instructions                                     | 30 |

| 13.1. Vector Floating-Point Exception Flags                                |    |

| 13.2. Vector Single-Width Floating-Point Add/Subtract Instructions         |    |

| 13.3. Vector Widening Floating-Point Add/Subtract Instructions             |    |

|              | 13.4. Vector Single-Width Floating-Point Multiply/Divide Instructions    |    |

|--------------|--------------------------------------------------------------------------|----|

|              | 13.5. Vector Widening Floating-Point Multiply                            |    |

|              | 13.6. Vector Single-Width Floating-Point Fused Multiply-Add Instructions |    |

|              | 13.7. Vector Widening Floating-Point Fused Multiply-Add Instructions     |    |

|              | 13.8. Vector Floating-Point Square-Root Instruction                      |    |

|              | 13.9. Vector Floating-Point Reciprocal Square-Root Estimate Instruction  |    |

|              | 13.10. Vector Floating-Point Reciprocal Estimate Instruction             |    |

|              | 13.11. Vector Floating-Point MIN/MAX Instructions                        |    |

|              | 13.12. Vector Floating-Point Sign-Injection Instructions                 |    |

|              | 13.13. Vector Floating-Point Compare Instructions                        |    |

|              | 13.14. Vector Floating-Point Classify Instruction                        |    |

|              | 13.15. Vector Floating-Point Merge Instruction                           |    |

|              | 13.16. Vector Floating-Point Move Instruction                            |    |

|              | 13.17. Single-Width Floating-Point/Integer Type-Convert Instructions     |    |

|              | 13.18. Widening Floating-Point/Integer Type-Convert Instructions         |    |

|              | 13.19. Narrowing Floating-Point/Integer Type-Convert Instructions        |    |

| <u> 14.</u>  | <u>Vector Reduction Operations</u>                                       | 41 |

|              | 14.1. Vector Single-Width Integer Reduction Instructions                 |    |

|              | 14.2. Vector Widening Integer Reduction Instructions                     |    |

|              | 14.3. Vector Single-Width Floating-Point Reduction Instructions          |    |

|              | 14.4. Vector Widening Floating-Point Reduction Instructions              |    |

| <u> 15.</u>  | <u>Vector Mask Instructions</u>                                          | 42 |

|              | 15.1. Vector Mask-Register Logical Instructions                          |    |

|              | 15.2. Vector count population in mask vcpop.m                            |    |

|              | 15.3. vfirst find-first-set mask bit                                     |    |

|              | 15.4. vmsbf.mset-before-first mask bit                                   |    |

|              | 15.5. vmsif.mset-including-first mask bit                                |    |

|              | 15.6. vmsof.mset-only-first mask bit                                     |    |

|              | 15.7. Example using vector mask instructions                             |    |

|              | 15.8. Vector Iota Instruction                                            |    |

|              | 15.9. Vector Element Index Instruction                                   |    |

| <u>16.</u>   | Vector Permutation Instructions                                          | 43 |

|              | 16.1. Integer Scalar Move Instructions                                   |    |

|              | 16.2. Floating-Point Scalar Move Instructions                            |    |

|              | 16.3. Vector Slide Instructions                                          |    |

|              | 16.4. Vector Register Gather Instructions                                |    |

|              | 16.5. Vector Compress Instruction                                        |    |

|              | 16.6. Whole Vector Register Move                                         |    |

| <u>17.</u>   | Exception Handling                                                       | 46 |

|              | 17.1. Precise vector traps                                               |    |

|              | 17.2. Imprecise vector traps                                             |    |

|              | 17.3. Selectable precise/imprecise traps                                 |    |

|              | 17.4. Swappable traps                                                    |    |

| <u>18.</u>   | Standard Vector Extensions                                               | 57 |

|              | 18.1. Zvl*: Minimum Vector Length Standard Extensions                    |    |

|              | 18.2. Zve*: Vector Extensions for Embedded Processors                    |    |

|              | 18.3. V: Vector Extension for Application Processors                     |    |

| <u> 19</u> . | Vector Instruction Listing                                               | 60 |

|              | pendix A: Vector Assembly Code Examples                                  | 75 |

|              | A.1. Vector-vector add example                                           |    |

| A.3. Memcpy example                                                          |    |

|------------------------------------------------------------------------------|----|

| A.4. Conditional example                                                     |    |

| A.5. SAXPY example                                                           |    |

| A.6. SGEMM example                                                           |    |

| A.7. Division approximation example                                          |    |

| A.8. Square root approximation example                                       |    |

| A.9. C standard library strcmp example                                       |    |

| <u>Appendix B: Calling Convention (Not authoritative - Placeholder Only)</u> | 78 |

| Appendix C: Fractional Lmul example                                          | 85 |

A.2. Example with mixed-width mask and compute.

Contributors include: Alon Amid, Krste Asanovic, Allen Baum, Alex Bradbury, Tony Brewer, Chris Celio, Aliaksei Chapyzhenka, Silviu Chiricescu, Ken Dockser, Bob Dreyer, Roger Espasa, Sean Halle, John Hauser, David Horner, Bruce Hoult, Bill Huffman, Nicholas Knight, Constantine Korikov, Ben Korpan, Hanna Kruppe, Yunsup Lee, Guy Lemieux, Grigorios Magklis, Filip Moc, Rich Newell, Albert Ou, David Patterson, Colin Schmidt, Alex Solomatnikov, Steve Wallach, Andrew Waterman, Jim Wilson.

# Changes from v1.0-rc1

Various clarifications to text, and added rationale for design choices.

Renamed vpopc.m to vcpop.m for consistency with scalar instruction. Keeping old assembler name as alias.

For mask-logical instructions, and vmsbf.m, vmsof.m mask-manipulation instructions, allow implementations to write entire mask register with result (always tail-agnostic)

Added vector length extensions "Zvl\*".

Added clarification of operation of mstatus. VS field and interaction with mstatus. SD.

Added definition of behavior under hypervisor.

Clarified checking of illegal values in vtype.

Made clear that calling convention appendix here is only a placeholder to help understand the examples, with RISC-V psABI being expanded to contain the authoritative calling convention.

Clarified the vxsat is in bit 0 of the CSR and that upper bits should be written as zeros.

Clarified that vxrm field is in low two bits of the CSR and that upper bits should be written as zeros.

Simplified explanations by removing text refering to option to have one element span multiple vector registers (ELEN > VLEN), as this is not being proposed at this time.

Clarified that implementations must raise illegal instruction exception for standard loads and stores with EEWs that are not supported by the implementation.

Removed Zvlsseg extension name as segment load/stores are required in all standard vector extensions.

Made clear that nf is encoded same as NFIELDS when used in whole register load/store instructions.

Clarified that instructions with register specifiers that violate register overlap constraints are reserved.

Added note to explain how floating-point scalar values would be handled when adding vectors to the Zfinx/Zdinx/Zhinx extensions.

The previous assembler mnemonics vmandnot and vmornot have been changed to vmandn and vmorn to be consistent with the equivalent scalar instructions. The old vmandnot and vmornot mnemonics will be retained as aliases in assembler.

Stated that misa.v is set for implementations supporting the standard V extension.

# 1. Introduction

This document is a draft of the second release candidate for version 1.0 of the RISC-V vector extension for public review.

#### This is not the frozen version of 1.0 for public review.

Note

When finally approved and the release candidate tag is removed, version 1.0 is intended to be sent out for public review as part of the RISC-V International ratification process. Version 1.0 will also then be considered stable enough to begin developing toolchains, functional simulators, and initial implementations, including in upstream software projects, and is not expected to have major functionality changes except if serious issues are discovered during ratification. Once ratified, the spec will be given version 2.0.

This draft spec includes the complete set of currently defined vector instructions. Section <u>Standard Vector Extensions</u> lists the standard vector extensions and which instructions and element widths are supported by each extension.

# 2. Implementation-defined Constant Parameters

Each hart supporting a vector extension defines two parameters:

- 1. The maximum size in bits of a vector element that any operation can produce or consume, *ELEN* ≥ 8, which must be a power of 2.

- 2. The number of bits in a single vector register, VLEN≥ ELEN, which must be a power of 2, and must be no greater than 2<sup>16</sup>

Standard vector extensions (Section <u>Standard Vector Extensions</u>) and architecture profiles may set further constraints on *ELEN* and *VLEN*.

Note Future extensions may allow ELEN > VLEN by holding one element using bits from multiple vector registers, but this current proposal does not include this option.

Note SEW=8 with VLEN=65,536). Any future extension beyond 64Kib per vector register will require new configuration instructions such that software using the old configuration instructions does not see greater vector lengths.

The vector extension supports writing binary code that under certain constraints will execute portably on harts with different values for the VLEN parameter, provided the harts support the required element types and instructions.

Note Code can be written that will expose differences in implementation parameters.

In general, thread contexts with active vector state cannot be migrated during execution between harts that have any difference in VLEN or ELEN parameters.

# 3. Vector Extension Programmer's Model

The vector extension adds 32 vector registers, and seven unprivileged CSRs (vstart, vxsat, vxrm, vcsr, vtype, vl, vlenb) to a base scalar RISC-V ISA.

Table 1. New vector CSRs

| Address | Privilege | Name   | Description                              |

|---------|-----------|--------|------------------------------------------|

| 0x008   | URW       | vstart | Vector start position                    |

| 0x009   | URW       | vxsat  | Fixed-Point Saturate Flag                |

| 0x00A   | URW       | vxrm   | Fixed-Point Rounding Mode                |

| 0x00F   | URW       | vcsr   | Vector control and status register       |

| 0xC20   | URO       | vl     | Vector length                            |

| 0xC21   | URO       | vtype  | Vector data type register                |

| 0xC22   | URO       | vlenb  | VLEN/8 (vector register length in bytes) |

Note The four CSR numbers 0x00B-0x00E are tentatively reserved for future vector CSRs, some of which may be mirrored into vcsr.

## 3.1. Vector Registers

The vector extension adds 32 architectural vector registers, v0-v31 to the base scalar RISC-V ISA.

Each vector register has a fixed VLEN bits of state.

#### 3.2. Vector Context Status in mstatus

A vector context status field, VS, is added to mstatus[10:9] and shadowed in sstatus[10:9]. It is defined analogously to the floating-point context status field, FS.

Attempts to execute any vector instruction, or to access the vector CSRs, raise an illegal-instruction exception when mstatus.VS is set to Off.

When mstatus. VS is set to Initial or Clean, executing any instruction that changes vector state, including the vector CSRs, will change mstatus. VS to Dirty. Implementations may also change mstatus. VS from Initial or Clean to Dirty at any time, even when there is no change in vector state.

Note Accurate setting of mstatus. VS is an optimization. Software will typically use VS to reduce context-swap overhead.

If mstatus. VS is Dirty, mstatus. SD is 1; otherwise, mstatus. SD is set in accordance with existing specifications.

Implementations may have a writable misa. V field. Analogous to the way in which the floating-point unit is handled, the mstatus. VS field may exist even if misa. V is clear.

Allowing mstatus.VS to exist when misa.V is clear, enables vector emulation and simplifies handling of mstatus.VS in systems

Note with writable misa.V.

## 3.3. Vector Context Status in vsstatus

When the hypervisor extension is present, a vector context status field, VS, is added to vsstatus[10:9]. It is defined analogously to the floating-point context status field, FS.

When V=1, both vsstatus. VS and mstatus. VS are in effect: attempts to execute any vector instruction, or to access the vector CSRs, raise an illegal-instruction exception when either field is set to Off.

When V=1 and neither vsstatus.VS nor mstatus.VS is set to Off, executing any instruction that changes vector state, including the vector CSRs, will change both mstatus.VS and vsstatus.VS to Dirty. Implementations may also change mstatus.VS or vsstatus.VS from Initial or Clean to Dirty at any time, even when there is no change in vector state.

If vsstatus. VS is Dirty, vsstatus. SD is 1; otherwise, vsstatus. SD is set in accordance with existing specifications.

If mstatus. VS is Dirty, mstatus. SD is 1; otherwise, mstatus. SD is set in accordance with existing specifications.

For implementations with a writable misa. V field, the vsstatus. VS field may exist even if misa. V is clear.

#### 3.4. Vector type register, vtype

The read-only XLEN-wide *vector type* CSR, vtype provides the default type used to interpret the contents of the vector register file, and can only be updated by vset{i}vl{i} instructions. The vector type determines the organization of elements in each vector register, and how multiple vector registers are grouped. The vtype register also indicates how masked-off elements and elements past the current vector length in a vector result are handled.

Note Allowing updates only via the vset{i}vl{i} instructions simplifies maintenance of the vtype register state.

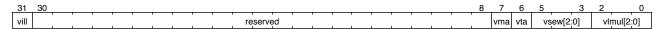

The vtype register has five fields, vill, vma, vta, vsew[2:0], and vlmul[2:0]. Bits vtype[XLEN-2:8] should be written with zero, and non-zero values in this field are reserved.

Note This diagram shows the layout for RV32 systems, whereas in general vill should be at bit XLEN-1.

Table 2. vtype register layout

| Bits     | Name       | Description                                     |

|----------|------------|-------------------------------------------------|

| XLEN-1   | vill       | Illegal value if set                            |

| XLEN-2:8 | 0          | Reserved if non-zero                            |

| 7        | vma        | Vector mask agnostic                            |

| 6        | vta        | Vector tail agnostic                            |

| 5:3      | vsew[2:0]  | Selected element width (SEW) setting            |

| 2:0      | vlmul[2:0] | Vector register group multiplier (LMUL) setting |

A small implementation supporting ELEN=32 requires only seven bits of state in vtype: two bits for ma and ta, two bits for vsew[1:0] and three bits for vlmul[2:0]. The illegal value represented by vill can be internally encoded using the illegal 64-bit combination in vsew[1:0] without requiring an additional storage bit to hold vill.

Note | Further standard and custom vector extensions may extend these fields to support a greater variety of data types.

The primary motivation for the vtype CSR is to allow the vector instruction set to fit into a 32-bit instruction encoding space. A separate vset{i}vl{i} instruction can be used to set vl and/or vtype fields before execution of a vector instruction, and implementations may choose to fuse these two instructions into a single internal vector microop. In many cases, the vl and vtype values can be reused across multiple instructions, reducing the static and dynamic instruction overhead from the vset{i}vl{i} instructions. It is anticipated that a future extended 64-bit instruction encoding would allow these fields to be specified statically in the instruction encoding.

#### 3.4.1. Vector selected element width vsew[2:0]

Note

The value in vsew sets the dynamic *selected element width* (SEW). By default, a vector register is viewed as being divided into VLEN/SEW elements.

Table 3. vsew[2:0] (selected element width) encoding

| vsew[2:0] |   |   | SEW      |  |

|-----------|---|---|----------|--|

| 0         | 0 | 0 | 8        |  |

| 0         | 0 | 1 | 16       |  |

| 0         | 1 | 0 | 32       |  |

| 0         | 1 | 1 | 64       |  |

| 1         | X | X | Reserved |  |

While it is anticipated the larger vsew[2:0] encodings (100-111) will be used to encode larger SEW, the encodings are formally reserved at this point.

Table 4. Example VLEN = 128 bits

| SEW | Elements per vector register |

|-----|------------------------------|

| 64  | 2                            |

| 32  | 4                            |

| 16  | 8                            |

| 8   | 16                           |

The supported element width may vary with LMUL.

Note

The current set of standard vector extensions do not vary supported element width with LMUL. Some future extensions may support larger SEWs only when bits from multiple vector registers are combined using LMUL. In this case, software that relies on large SEW should attempt to use the largest LMUL, and hence the fewest vector register groups, to increase the number of implementations on which the code will run. The vill bit in vtype should be checked after setting vtype to see if the configuration is supported, and an alternate code path should be provided if it is not. Alternatively, a profile can mandate the minimum SEW at each LMUL setting.

#### 3.4.2. Vector Register Grouping (vlmul[2:0])

Multiple vector registers can be grouped together, so that a single vector instruction can operate on multiple vector registers. The term *vector register group* is used herein to refer to one or more vector registers used as a single operand to a vector instruction. Vector register groups can be used to provide greater execution efficiency for longer application vectors, but the main reason for their inclusion is to allow double-width or larger elements to be operated on with the same vector length as single-width elements. The vector length multiplier, *LMUL*, when greater than 1, represents the default number of vector registers that are combined to form a vector register group. Implementations must support LMUL integer values of 1, 2, 4, and 8.

Note

The vector architecture includes instructions that take multiple source and destination vector operands with different element widths, but the same number of elements. The effective LMUL (EMUL) of each vector operand is determined by the number of registers required to hold the elements. For example, for a widening add operation, such as add 32-bit values to produce 64-bit results, a double-width result requires twice the LMUL of the single-width inputs.

LMUL can also be a fractional value, reducing the number of bits used in a single vector register. Fractional LMUL is used to increase the number of effective usable vector register groups when operating on mixed-width values.

NI - 4

With only integer LMUL values, a loop operating on a range of sizes would have to allocate at least one whole vector register (LMUL=1) for the narrowest data type and then would consume multiple vector registers (LMUL>1) to form a vector register group for each wider vector operand. This can limit the number of vector register groups available. With fractional LMUL, the widest values need occupy only a single vector register while narrower values can occupy a fraction of a single vector register, allowing all 32 architectural vector register names to be used for different values in a vector loop even when handling mixed-width values. Fractional LMUL implies portions of vector registers are unused, but in some cases, having more shorter register-resident vectors improves efficiency relative to fewer longer register-resident vectors.

Implementations must provide fractional LMUL settings that allow the narrowest supported type to occupy a fraction of a vector register corresponding to the ratio of the narrowest supported type's width to that of the largest supported type's width. In general, the requirement is to support LMUL  $\geq$  SEW<sub>MIN</sub>/ELEN, where SEW<sub>MIN</sub> is the narrowest supported SEW value and ELEN is the widest supported SEW value. In the standard extensions, SEW<sub>MIN</sub>=8. For standard vector extensions with ELEN=32, fractional LMULs of 1/2 and 1/4 must be supported. For standard vector extensions with ELEN=64, fractional LMULs of 1/2, 1/4, and 1/8 must be supported.

Note

When LMUL < SEW<sub>MIN</sub>/ELEN, there is no guarantee an implementation would have enough bits in the fractional vector register to store at least one element, as VLEN=ELEN is a valid implementation choice. For example, with VLEN=ELEN=32, and SEW<sub>MIN</sub>=8, an LMUL of 1/8 would only provide four bits of storage in a vector register.

For a given supported fractional LMUL setting, implementations must support SEW settings between SEW<sub>MIN</sub> and LMUL \* ELEN, inclusive.

An attempt to set an unsupported SEW and LMUL configuration sets the vill bit in vtype.

The use of vtype encodings with LMUL < SEW<sub>MIN</sub>/ELEN is *reserved*, but implementations can set vill if they do not support these configurations.

Requiring all implementations to set vill in this case would prohibit future use of this case in an extension, so to allow for a future definition of LMUL<SEW<sub>MIN</sub>/ELEN behavior, we consider the use of this case to be *reserved*.

It is recommended that assemblers provide a warning (not an error) if a vsetvli instruction attempts to write an LMUL < Note | SEW<sub>MIN</sub>/ELEN.

LMUL is set by the signed vlmul field in vtype (i.e., LMUL =  $2^{vlmul[2:0]}$ ).

The derived value VLMAX = LMUL\*VLEN/SEW represents the maximum number of elements that can be operated on with a single vector instruction given the current SEW and LMUL settings as shown in the table below.

| vlmu | vlmul[2:0] |   | /lmul[2:0] LMUL |    | LMUL       | #groups                               | VLMAX | Registers grouped with register n |

|------|------------|---|-----------------|----|------------|---------------------------------------|-------|-----------------------------------|

| 1    | 0          | 0 | -               | -  | -          | reserved                              |       |                                   |

| 1    | 0          | 1 | 1/8             | 32 | VLEN/SEW/8 | v n (single register in group)        |       |                                   |

| 1    | 1          | 0 | 1/4             | 32 | VLEN/SEW/4 | v n (single register in group)        |       |                                   |

| 1    | 1          | 1 | 1/2             | 32 | VLEN/SEW/2 | v <i>n</i> (single register in group) |       |                                   |

| 0    | 0          | 0 | 1               | 32 | VLEN/SEW   | v n (single register in group)        |       |                                   |

| 0    | 0          | 1 | 2               | 16 | 2*VLEN/SEW | v n, v n+1                            |       |                                   |

| 0    | 1          | 0 | 4               | 8  | 4*VLEN/SEW | v n,, v n+3                           |       |                                   |

| 0    | 1          | 1 | 8               | 4  | 8*VLEN/SEW | v n,, v n+7                           |       |                                   |

When LMUL=2, the vector register group contains vector register v n and vector register v n+1, providing twice the vector length in bits. Instructions specifying an LMUL=2 vector register group with an odd-numbered vector register are reserved.

When LMUL=4, the vector register group contains four vector registers, and instructions specifying an LMUL=4 vector register group using vector register numbers that are not multiples of four are reserved.

When LMUL=8, the vector register group contains eight vector registers, and instructions specifying an LMUL=8 vector register group using register numbers that are not multiples of eight are reserved.

Mask registers are always contained in a single vector register, regardless of LMUL.

### 3.4.3. Vector Tail Agnostic and Vector Mask Agnostic vta and vma

These two bits modify the behavior of destination tail elements and destination inactive masked-off elements respectively during the execution of vector instructions. The tail and inactive sets contain element positions that are not receiving new results during a vector operation, as defined in Section <u>Prestart, Active, Inactive, Body, and Tail Element Definitions</u>.

All systems must support all four options:

| vta | vma           | Tail Elements | Inactive Elements |

|-----|---------------|---------------|-------------------|

| 0   | 0 undisturbed |               | undisturbed       |

| 0   | 1             | undisturbed   | agnostic          |

| 1   | 0             | agnostic      | undisturbed       |

| 1   | 1             | agnostic      | agnostic          |

Mask destination tail elements are always treated as tail-agnostic, regardless of the setting of vta.

When a set is marked undisturbed, the corresponding set of destination elements in a vector register group retain the value they previously held.

When a set is marked agnostic, the corresponding set of destination elements in any vector destination operand can either retain the value they previously held, or are overwritten with 1s. Within a single vector instruction, each destination element can be either left undisturbed or overwritten with 1s, in any combination, and the pattern of undisturbed or overwritten with 1s is not required to be deterministic when the instruction is executed with the same inputs.

The agnostic policy was added to accommodate machines with vector register renaming. With an undisturbed policy, all elements would have to be read from the old physical destination vector register to be copied into the new physical destination vector register. This causes an inefficiency when these inactive or tail values are not required for subsequent calculations.

The value of all 1s instead of all 0s was chosen for the overwrite value to discourage software developers from depending on the value written.

A simple in-order implementation can ignore the settings and simply execute all vector instructions using the undisturbed policy. The vta and vma state bits must still be provided in vtype for compatibility and to support thread migration.

An out-of-order implementation can choose to implement tail-agnostic + mask-agnostic using tail-agnostic + mask-undisturbed to reduce implementation complexity.

The definition of agnostic result policy is left loose to accommodate migrating application threads between harts on a small in-order core (which probably leaves agnostic regions undisturbed) and harts on a larger out-of-order core with register renaming (which probably overwrites agnostic elements with 1s). As it might be necessary to restart in the middle, we allow arbitrary mixing of agnostic policies within a single vector instruction. This allowed mixing of policies also enables implementations that might change policies for different granules of a vector register, for example, using undisturbed within a granule that is actively operated on but renaming to all 1s for granules in the tail.

In addition, except for mask load instructions, any element in the tail of a mask result can also be written with the value the mask-producing operation would have calculated with vl=VLMAX. Furthermore, for mask-logical instructions and vmsbf.m, vmsif.m, vmsof.m mask-manipulation instructions, any element in the tail of the result can be written with the value the mask-producing operation would have calculated with vl=VLEN, SEW=8, and LMUL=8 (i.e., all bits of the mask register can be overwritten).

Mask tails are always treated as agnostic to reduce complexity of managing mask data, which can be written at bit granularity. There appears to be little software need to support tail-undisturbed for mask register values. Allowing mask-generating instructions to write back the result of the instruction avoids the need for logic to mask out the tail, except mask loads cannot write memory values to destination mask tails as this would imply accessing memory past software intent.

The assembly syntax adds two mandatory flags to the vsetvli instruction:

```

ta # Tail agnostic

tu # Tail undisturbed

ma # Mask agnostic

mu # Mask undisturbed

vsetvli t0, a0, e32, m4, ta, ma # Tail agnostic, mask agnostic

vsetvli t0, a0, e32, m4, tu, ma # Tail undisturbed, mask agnostic

vsetvli t0, a0, e32, m4, ta, mu # Tail agnostic, mask undisturbed

vsetvli t0, a0, e32, m4, tu, mu # Tail undisturbed, mask undisturbed

vsetvli t0, a0, e32, m4, tu, mu # Tail undisturbed, mask undisturbed

```

Prior to v0.9, when these flags were not specified on a vsetvli, they defaulted to mask-undisturbed/tail-undisturbed. The use of vsetvli without these flags is deprecated, however, and specifying a flag setting is now mandatory. The default should perhaps be tail-agnostic/mask-agnostic, so software has to specify when it cares about the non-participating elements, but given the historical meaning of the instruction prior to introduction of these flags, it was decided to always require them in future assembly code.

## 3.4.4. Vector Type Illegal vill

The vill bit is used to encode that a previous  $vset\{i\}vl\{i\}$  instruction attempted to write an unsupported value to vtype.

Note The vill bit is held in bit XLEN-1 of the CSR to support checking for illegal values with a branch on the sign bit.

All bits of the vtype argument must be considered in determining if the value is supported by the implementation.

All bits must be checked to ensure that new code assuming unsupported vector features in vtype traps instead of executing incorrectly on an older implementation.

A vtype value with the vill bit set is an unsupported value.

If the vill bit is set, then any attempt to execute a vector instruction that depends upon vtype will raise an illegal-instruction exception.

$Note \begin{tabular}{l} \textbf{Vset} \{i\} \textbf{vl} \{i\} \ and \ whole-register loads, stores, and moves do not depend upon vtype. \end{tabular}$

When the vill bit is set, the other XLEN-1 bits in vtype shall be zero.

## 3.5. Vector Length Register v1

The XLEN-bit-wide read-only v1 CSR can only be updated by the vset{i}v1{i} instructions, and the fault-only-first vector load instruction variants.

The v1 register holds an unsigned integer specifying the number of elements to be updated with results from a vector instruction, as further detailed in Section Prestart, Active, Inactive, Body, and Tail Element Definitions.

The number of bits implemented in v1 depends on the implementation's maximum vector length of the smallest supported type. The smallest vector implementation with VLEN=32 and supporting SEW=8 would need at least six bits in v1 to hold the values 0-32 (VLEN=32, with LMUL=8 and SEW=8, yields VLMAX=32).

#### 3.6. Vector Byte Length vlenb

The XLEN-bit-wide read-only CSR vlenb holds the value VLEN/8, i.e., the vector register length in bytes.

Note The value in vlenb is a design-time constant in any implementation.

Without this CSR, several instructions are needed to calculate VLEN in bytes, and the code has to disturb current v1 and vtype settings which require them to be saved and restored.

#### 3.7. Vector Start Index CSR vstart

The vstart read-write CSR specifies the index of the first element to be executed by a vector instruction, as described in Section <u>Prestart</u>, <u>Active</u>, <u>Inactive</u>, <u>Body</u>, <u>and Tail Element Definitions</u>.

Normally, vstart is only written by hardware on a trap on a vector instruction, with the vstart value representing the element on which the trap was taken (either a synchronous exception or an asynchronous interrupt), and at which execution should resume after a resumable trap is handled.

All vector instructions are defined to begin execution with the element number given in the vstart CSR, leaving earlier elements in the destination vector undisturbed, and to reset the vstart CSR to zero at the end of execution.

Note All vector instructions, including  $vset\{i\}vl\{i\}$ , reset the vstart CSR to zero.

vstart is not modified by vector instructions that raise illegal-instruction exceptions.

The vstart CSR is defined to have only enough writable bits to hold the largest element index (one less than the maximum VLMAX).

The maximum vector length is obtained with the largest LMUL setting (8) and the smallest SEW setting (8), so VLMAX\_max = Note 8\*VLEN/8 = VLEN. For example, for VLEN=256, vstart would have 8 bits to represent indices from 0 through 255.

The use of vstart values greater than the largest element index for the current SEW setting is reserved.

It is recommended that implementations trap if vstart is out of bounds. It is not required to trap, as a possible future use of upper vstart bits is to store imprecise trap information.

The vstart CSR is writable by unprivileged code, but non-zero vstart values may cause vector instructions to run substantially slower on some implementations, so vstart should not be used by application programmers. A few vector instructions cannot be executed with a non-zero vstart value and will raise an illegal instruction exception as defined below.

Note Making vstart visible to unprivileged code supports user-level threading libraries.

Implementations are permitted to raise illegal instruction exceptions when attempting to execute a vector instruction with a value of vstart that the implementation can never produce when executing that same instruction with the same vtype setting.

For example, some implementations will never take interrupts during execution of a vector arithmetic instruction, instead waiting until the instruction completes to take the interrupt. Such implementations are permitted to raise an illegal instruction exception when attempting to execute a vector arithmetic instruction when vstart is nonzero.

Note

When migrating a software thread between two harts with different microarchitectures, the vstart value might not be supported by the new hart microarchitecture. The runtime on the receiving hart might then have to emulate instruction execution up to the next supported vstart element position. Alternatively, migration events can be constrained to only occur at mutually supported vstart locations.

## 3.8. Vector Fixed-Point Rounding Mode Register vxrm

The vector fixed-point rounding-mode register holds a two-bit read-write rounding-mode field in the least-significant bits (vxrm[1:0]). The upper bits, vxrm[XLEN-1:2], should be written as zeros.

The vector fixed-point rounding-mode is given a separate CSR address to allow independent access, but is also reflected as a field in vcsr.

Note A new rounding mode can be set while saving the original rounding mode using a single csrwi instruction.

The fixed-point rounding algorithm is specified as follows. Suppose the pre-rounding result is v, and d bits of that result are to be rounded off. Then the rounded result is v > d + r, where r depends on the rounding mode as specified in the following table.

Table 5. vxrm encoding

| vxrm[1:0] Abbreviation Rounding Mode |   | Abbreviation | Rounding Mode                              | Rounding increment, r        |

|--------------------------------------|---|--------------|--------------------------------------------|------------------------------|

| 0                                    | 0 | rnu          | round-to-nearest-up (add +0.5 LSB)         | v[d-1]                       |

| 0                                    | 1 | rne          | round-to-nearest-even                      | v[d-1] & (v[d-2:0]≠0   v[d]) |

| 1                                    | 0 | rdn          | round-down (truncate)                      | 0                            |

| 1                                    | 1 | rod          | round-to-odd (OR bits into LSB, aka "jam") | !v[d] & v[d-1:0]≠0           |

The rounding functions:

```

roundoff\_unsigned(v, d) = (unsigned(v) >> d) + r

roundoff\_signed(v, d) = (signed(v) >> d) + r

```

are used to represent this operation in the instruction descriptions below.

#### 3.9. Vector Fixed-Point Saturation Flag vxsat

The vxsat CSR has a single read-write least-significant bit (vxsat[0]) that indicates if a fixed-point instruction has had to saturate an output value to fit into a destination format. Bits vxsat[XLEN-1:1] should be written as zeros.

The vxsat bit is mirrored in vcsr.

### 3.10. Vector Control and Status Register vcsr

The vxrm and vxsat separate CSRs can also be accessed via fields in the vector control and status CSR, vcsr.

Table 6. vcsr layout

|                                    | Bits Name |           | Description                         |

|------------------------------------|-----------|-----------|-------------------------------------|

| 2:1 vxrm[1:0] Fixed-point rounding |           | vxrm[1:0] | Fixed-point rounding mode           |

|                                    | 0         | vxsat     | Fixed-point accrued saturation flag |

#### 3.11. State of Vector Extension at Reset

The vector extension must have a consistent state at reset. In particular, vtype and v1 must have values that can be read and then restored with a single vsetv1 instruction.

Note It is recommended that at reset, vtype.vill is set, the remaining bits in vtype are zero, and vl is set to zero.

The vstart, vxrm, vxsat CSRs can have arbitrary values at reset.

Most uses of the vector unit will require an initial vset{i}vl{i}, which will reset vstart. The vxrm and vxsat fields should be reset explicitly in software before use.

The vector registers can have arbitrary values at reset.

# 4. Mapping of Vector Elements to Vector Register State

The following diagrams illustrate how different width elements are packed into the bytes of a vector register depending on the current SEW and LMUL settings, as well as implementation VLEN. Elements are packed into each vector register with the least-significant byte in the lowest-numbered bits.

The mapping was chosen to provide the simplest and most portable model for software, but might appear to incur large wiring cost for wider vector datapaths on certain operations. The vector instruction set was expressly designed to support implementations that internally rearrange vector data for different SEW to reduce datapath wiring costs, while externally preserving the simple software model.

For example, microarchitectures can track the EEW with which a vector register was written, and then insert additional scrambling operations to rearrange data if the register is accessed with a different EEW.

## 4.1. Mapping for LMUL = 1

When LMUL=1, elements are simply packed in order from the least-significant to most-significant bits of the vector register.

Note To increase readability, vector register layouts are drawn with bytes ordered from right to left with increasing byte address. Bits within an element are numbered in a little-endian format with increasing bit index from right to left corresponding to increasing magnitude.

LMUL=1 examples.

The element index is given in hexadecimal and is shown placed at the least-significant byte of the stored element.

| VLEN=32b                                |                                                                                                                                                                                      |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte                                    | 3 2 1 0                                                                                                                                                                              |

| SEW=8b<br>SEW=16b<br>SEW=32b            | 3 2 1 0<br>1 0<br>0                                                                                                                                                                  |

| VLEN=64b                                |                                                                                                                                                                                      |

| Byte                                    | 7 6 5 4 3 2 1 0                                                                                                                                                                      |

| SEW=8b<br>SEW=16b<br>SEW=32b<br>SEW=64b | 7 6 5 4 3 2 1 0<br>3 2 1 0<br>1 0<br>0                                                                                                                                               |

| VLEN=128                                | b                                                                                                                                                                                    |

| Byte                                    | F E D C B A 9 8 7 6 5 4 3 2 1 0                                                                                                                                                      |

| SEW=8b<br>SEW=16b<br>SEW=32b<br>SEW=64b | F E D C B A 9 8 7 6 5 4 3 2 1 0<br>7 6 5 4 3 2 1 0<br>3 2 1 0<br>1 0                                                                                                                 |

| VLEN=256                                | b                                                                                                                                                                                    |

| Byte                                    | 1F1E1D1C1B1A19181716151413121110 F E D C B A 9 8 7 6 5 4 3 2 1 0                                                                                                                     |

| SEW=8b<br>SEW=16b<br>SEW=32b<br>SEW=64b | 1F1E1D1C1B1A19181716151413121110 F E D C B A 9 8 7 6 5 4 3 2 1 0 F E D C B A 9 8 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 0 7 0 7 0 7 0 7 0 7 0 7 0 7 0 7 0 |

## 4.2. Mapping for LMUL < 1

When LMUL < 1, only the first LMUL\*VLEN/SEW elements in the vector register are used. The remaining space in the vector register is treated as part of the tail, and hence must obey the vta setting.

## 4.3. Mapping for LMUL > 1

When vector registers are grouped, the elements of the vector register group are packed contiguously in element order beginning with the lowest-numbered vector register and moving to the next-highest-numbered vector register in the group once each vector register is filled.

```

LMUL > 1 examples

VLEN=32b, SEW=8b, LMUL=2

Byte

3 2 1 0

v2*n

3 2 1 0

v2*n+1

7 6 5 4

VLEN=32b, SEW=16b, LMUL=2

3 2 1 0

Byte

v2*n

1

0

2

v2*n+1

3

VLEN=32b, SEW=16b, LMUL=4

Byte

3 2 1 0

v4*n

0

1

2

v4*n+1

3

4

v4*n+2

5

v4*n+3

7

6

VLEN=32b, SEW=32b, LMUL=4

Byte

3 2 1 0

0

v4*n

v4*n+1

1

v4*n+2

2

v4*n+3

3

VLEN=64b, SEW=32b, LMUL=2

7 6 5 4 3 2 1 0

Byte

v2*n

1

0

v2*n+1

3

2

VLEN=64b, SEW=32b, LMUL=4

Byte

7 6 5 4 3 2 1 0

v4*n

1

v4*n+1

3

2

v4*n+2

5

4

v4*n+3

7

6

VLEN=128b, SEW=32b, LMUL=2

Byte

F E D C B A 9 8 7 6 5 4 3 2 1 0

v2*n

3

2

1

7

v2*n+1

6

5

4

VLEN=128b, SEW=32b, LMUL=4

F E D C B A 9 8 7 6 5 4 3 2 1 0

Byte

v4*n

3

2

1

0

v4*n+1

7

6

5

4

v4*n+2

9

В

Α

8

Ε

v4*n+3

F

D

С

```

## 4.4. Mapping across Mixed-Width Operations

The vector ISA is designed to support mixed-width operations without requiring additional explicit rearrangement instructions. The recommended software strategy when operating on multiple vectors with different precision values is to

modify vtype dynamically to keep SEW/LMUL constant (and hence VLMAX constant).

The following example shows four different packed element widths (8b, 16b, 32b, 64b) in a VLEN=128b implementation. The vector register grouping factor (LMUL) is increased by the relative element size such that each group can hold the same number of vector elements (VLMAX=8 in this example) to simplify stripmining code.

Example VLEN=128b, with SEW/LMUL=16 Byte F E D C B A 9 8 7 6 5 4 3 2 1 0 - - 7 6 5 4 3 2 1 0 SEW=8b, LMUL=1/2 vn 2 SEW=16b, LMUL=1 vn v2\*n 1 SEW=32b, LMUL=2 v2\*n+1 7 5 4 v4\*n 1 0 SEW=64b, LMUL=4 v4\*n+1 3 2 4 v4\*n+2 5 7

The following table shows each possible constant SEW/LMUL operating point for loops with mixed-width operations. Each column represents a constant SEW/LMUL operating point. Entries in table are the LMUL values that yield that column's SEW/LMUL value for the datawidth on that row. In each column, an LMUL setting for a datawidth indicates that it can be aligned with the other datawidths in the same column that also have an LMUL setting, such that all have the same VLMAX.

6

|         | SEW/LMUL |   |   |   |     |     |     |  |  |  |  |

|---------|----------|---|---|---|-----|-----|-----|--|--|--|--|

|         | 1        | 2 | 4 | 8 | 16  | 32  | 64  |  |  |  |  |

| SEW= 8  | 8        | 4 | 2 | 1 | 1/2 | 1/4 | 1/8 |  |  |  |  |

| SEW= 16 |          | 8 | 4 | 2 | 1   | 1/2 | 1/4 |  |  |  |  |

| SEW= 32 |          |   | 8 | 4 | 2   | 1   | 1/2 |  |  |  |  |

| SEW= 64 |          |   |   | 8 | 4   | 2   | 1   |  |  |  |  |

Larger LMUL settings can also used to simply increase vector length to reduce instruction fetch and dispatch overheads in cases where fewer vector register groups are needed.

## 4.5. Mask Register Layout

v4\*n+3

A vector mask occupies only one vector register regardless of SEW and LMUL.

Each element is allocated a single mask bit in a mask vector register. The mask bit for element i is located in bit i of the mask register, independent of SEW or LMUL.

## 5. Vector Instruction Formats

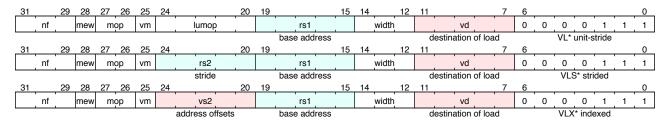

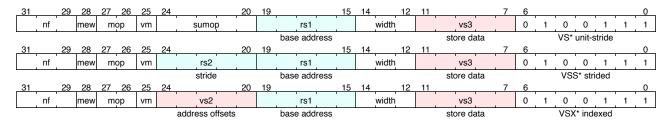

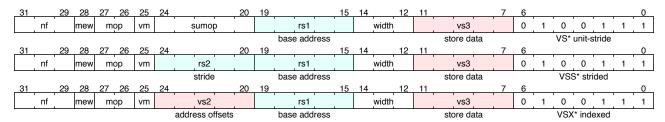

The instructions in the vector extension fit under two existing major opcodes (LOAD-FP and STORE-FP) and one new major opcode (OP-V).

Vector loads and stores are encoded within the scalar floating-point load and store major opcodes (LOAD-FP/STORE-FP). The vector load and store encodings repurpose a portion of the standard scalar floating-point load/store 12-bit immediate field to provide further vector instruction encoding, with bit 25 holding the standard vector mask bit (see Mask Encoding).

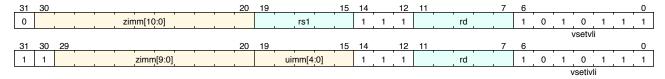

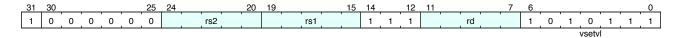

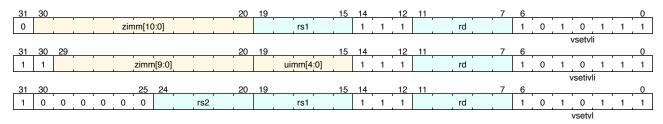

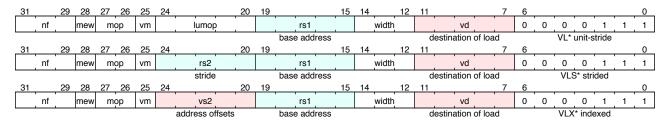

Format for Vector Load Instructions under LOAD-FP major opcode

Format for Vector Store Instructions under STORE-FP major opcode

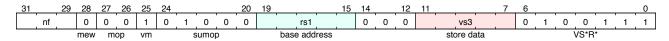

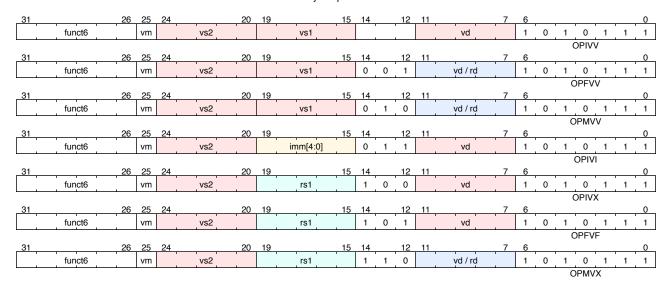

Formats for Vector Arithmetic Instructions under OP-V major opcode

Formats for Vector Configuration Instructions under OP-V major opcode

Vector instructions can have scalar or vector source operands and produce scalar or vector results, and most vector instructions can be performed either unconditionally or conditionally under a mask.

Vector loads and stores move bit patterns between vector register elements and memory. Vector arithmetic instructions operate on values held in vector register elements.

#### 5.1. Scalar Operands

Scalar operands can be immediates, or taken from the x registers, the f registers, or element 0 of a vector register. Scalar results are written to an x or f register or to element 0 of a vector register. Any vector register can be used to hold a scalar regardless of the current LMUL setting.

Note

Zfinx ("F in X") is a proposed new ISA extension where floating-point instructions take their arguments from the integer register file. The vector extension is also compatible with Zfinx, where the Zfinx vector extension has vector-scalar floating-point instructions taking their scalar argument from the x registers.

Note

We considered but did not pursue overlaying the f registers on v registers. The adopted approach reduces vector register pressure, avoids interactions with the standard calling convention, simplifies high-performance scalar floating-point design, and provides compatibility with the Zfinx ISA option. Overlaying f with v would provide the advantage of lowering the number of state bits in some implementations, but complicates high-performance designs and would prevent compatibility with the proposed Zfinx ISA option.

#### 5.2. Vector Operands

Each vector operand has an *effective element width* (EEW) and an *effective* LMUL (EMUL) that is used to determine the size and location of all the elements within a vector register group. By default, for most operands of most instructions, EEW=SEW and EMUL=LMUL.

Some vector instructions have source and destination vector operands with the same number of elements but different widths, so that EEW and EMUL differ from SEW and LMUL respectively but EEW/EMUL = SEW/LMUL. For example, most widening arithmetic instructions have a source group with EEW=SEW and EMUL=LMUL but have a destination group with EEW=2\*SEW and EMUL=2\*LMUL. Narrowing instructions have a source operand that has EEW=2\*SEW and EMUL=2\*LMUL but with a destination where EEW=SEW and EMUL=LMUL.

Vector operands or results may occupy one or more vector registers depending on EMUL, but are always specified using the lowest-numbered vector register in the group. Using other than the lowest-numbered vector register to specify a vector register group is a reserved encoding.

A destination vector register group can overlap a source vector register group only if one of the following holds:

- The destination EEW equals the source EEW.

- The destination EEW is smaller than the source EEW and the overlap is in the lowest-numbered part of the source register group (e.g., when LMUL=1, vnsrl.wi v0, v0, 3 is legal, but a destination of v1 is not).

- The destination EEW is greater than the source EEW, the source EMUL is at least 1, and the overlap is in the highest-numbered part of the destination register group (e.g., when LMUL=8, vzext.vf4 v0, v6 is legal, but a source of v0, v2, or v4 is not).

For the purpose of determining register group overlap constraints, mask elements have EEW=1.

Note The overlap constraints are designed to support resumable exceptions in machines without register renaming.

Any instruction encoding that violates the overlap constraints is reserved.

The largest vector register group used by an instruction can not be greater than 8 vector registers (i.e., EMUL≤8), and if a vector instruction would require greater than 8 vector registers in a group, the instruction encoding is reserved. For example, a widening operation that produces a widened vector register group result when LMUL=8 is reserved as this would imply a result EMUL=16.

Widened scalar values, e.g., input and output to a widening reduction operation, are held in the first element of a vector register and have EMUL=1.

#### 5.3. Vector Masking

Masking is supported on many vector instructions. Element operations that are masked off (inactive) never generate exceptions. The destination vector register elements corresponding to masked-off elements are handled with either a mask-undisturbed or mask-agnostic policy depending on the setting of the vma bit in vtype (Section <u>Vector Tail Agnostic and Vector Mask Agnostic vta and vma</u>).

The mask value used to control execution of a masked vector instruction is always supplied by vector register v0.

Note | Future vector extensions may provide longer instruction encodings with space for a full mask register specifier.

The destination vector register group for a masked vector instruction cannot overlap the source mask register (v0), unless the destination vector register is being written with a mask value (e.g., compares) or the scalar result of a reduction. These instruction encodings are reserved.

Note This constraint supports restart with a non-zero vstart value.

Other vector registers can be used to hold working mask values, and mask vector logical operations are provided to perform predicate calculations.

As specified in Section <u>Vector Tail Agnostic and Vector Mask Agnostic vta and vma</u>, mask destination values are always treated as tail-agnostic, regardless of the setting of vta.

#### 5.3.1. Mask Encoding

Where available, masking is encoded in a single-bit vm field in the instruction (inst[25]).

| vm | Description                              |

|----|------------------------------------------|

| 0  | vector result, only where v0.mask[i] = 1 |

| 1  | unmasked                                 |

Vector masking is represented in assembler code as another vector operand, with .t indicating that the operation occurs when v0.mask[i] is 1 (t for "true"). If no masking operand is specified, unmasked vector execution (vm=1) is assumed.

```

vop.v* v1, v2, v3, v0.t # enabled where v0.mask[i]=1, vm=0

vop.v* v1, v2, v3 # unmasked vector operation, vm=1

```

Note | Even though the current vector extensions only support one vector mask register v0 and only the true form of predication, the assembly syntax writes it out in full to be compatible with future extensions that might add a mask register specifier and support both true and complement mask values. The .t suffix on the masking operand also helps to visually encode the use of a mask.

The .mask suffix is not part of the assembly syntax. We only append it in contexts where a mask vector is subscripted, e.g., v0.mask[i].

#### 5.4. Prestart, Active, Inactive, Body, and Tail Element Definitions

The destination element indices operated on during a vector instruction's execution can be divided into three disjoint subsets.

- The *prestart* elements are those whose element index is less than the initial value in the vstart register. The prestart elements do not raise exceptions and do not update the destination vector register.

- The *body* elements are those whose element index is greater than or equal to the initial value in the vstart register, and less than the current vector length setting in v1. The body can be split into two disjoint subsets:

- The *active* elements during a vector instruction's execution are the elements within the body and where the current mask is enabled at that element position. The active elements can raise exceptions and update the

destination vector register group.

- The *inactive* elements are the elements within the body but where the current mask is disabled at that element position. The inactive elements do not raise exceptions and do not update any destination vector register group unless masked agnostic is specified (vtype.vma=1), in which case inactive elements may be overwritten with 1s.

- The *tail* elements during a vector instruction's execution are the elements past the current vector length setting specified in v1. The tail elements do not raise exceptions, and do not update any destination vector register group unless tail agnostic is specified (vtype.vta=1), in which case tail elements may be overwritten with 1s, or with the result of the instruction in the case of mask-producing instructions except for mask loads. When LMUL < 1, the tail includes the elements past VLMAX that are held in the same vector register.

```

for element index x

prestart(x) = (0 <= x < vstart)

body(x) = (vstart <= x < v1)

tail(x) = (v1 <= x < max(VLMAX, VLEN/SEW))

mask(x) = unmasked || v0.mask[x] == 1

active(x) = body(x) && mask(x)

inactive(x) = body(x) && !mask(x)</pre>

```

When  $vstart \ge v1$ , there are no body elements, and no elements are updated in any destination vector register group, including that no tail elements are updated with agnostic values.

Note As a consequence, when v1=0, no elements, including agnostic elements, are updated in the destination vector register group regardless of vstart.

Instructions that write an x register or f register do so even when  $vstart \ge v1$ , including when v1=0.

Some instructions such as vslidedown and vrgather may read indices past vl or even VLMAX in source vector register groups. The general policy is to return the value 0 when the index is greater than VLMAX in the source vector register group.

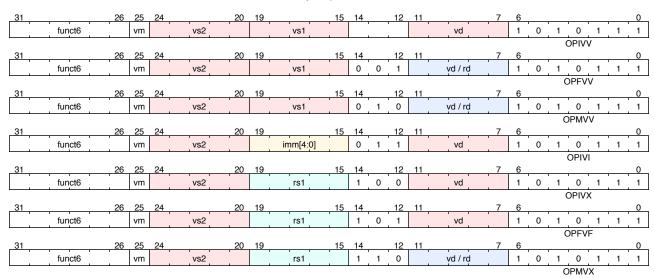

# 6. Configuration-Setting Instructions (vsetvli/vsetivli/vsetvl)

One of the common approaches to handling a large number of elements is "stripmining" where each iteration of a loop handles some number of elements, and the iterations continue until all elements have been processed. The RISC-V vector specification provides direct, portable support for this approach. The application specifies the total number of elements to be processed (the application vector length or AVL) as a candidate value for v1, and the hardware responds via a general-purpose register with the (frequently smaller) number of elements that the hardware will handle per iteration (stored in v1), based on the microarchitectural implementation and the vtype setting. A straightforward loop structure, shown in Example of stripmining and changes to SEW, depicts the ease with which the code keeps track of the remaining number of elements and the amount per iteration handled by hardware.

A set of instructions is provided to allow rapid configuration of the values in v1 and vtype to match application needs. The vset{i}v1{i} instructions set the vtype and v1 CSRs based on their arguments, and write the new value of v1 into rd.

```

vsetvli rd, rs1, vtypei # rd = new vl, rs1 = AVL, vtypei = new vtype setting

vsetivli rd, uimm, vtypei # rd = new vl, uimm = AVL, vtypei = new vtype setting

vsetvl rd, rs1, rs2 # rd = new vl, rs1 = AVL, rs2 = new vtype value

```

Formats for Vector Configuration Instructions under OP-V major opcode

## 6.1. vtype encoding

Note This diagram shows the layout for RV32 systems, whereas in general vill should be at bit XLEN-1.

Table 7. vtype register layout

| Bits     | Name       | Description                                     |

|----------|------------|-------------------------------------------------|

| XLEN-1   | vill       | Illegal value if set                            |

| XLEN-2:8 | 0          | Reserved if non-zero                            |

| 7        | vma        | Vector mask agnostic                            |

| 6        | vta        | Vector tail agnostic                            |

| 5:3      | vsew[2:0]  | Selected element width (SEW) setting            |

| 2:0      | vlmul[2:0] | Vector register group multiplier (LMUL) setting |

The new vtype setting is encoded in the immediate fields of vsetvli and vsetivli, and in the rs2 register for vsetvl.

Suggested assembler names used for vset{i}vli vtypei immediate

```

e8

# SEW=8b

e16

# SEW=16b

e32

# SEW=32b

e64

# SEW=64b

mf8 # LMUL=1/8

mf4 # LMUL=1/4

mf2 # LMUL=1/2

# LMUL=1, assumed if m setting absent

m1

m2

# LMUL=2

m4

# LMUL=4

# LMUL=8

m8

Examples:

# SEW= 8, LMUL=1

vsetvli t0, a0, e8

vsetvli t0, a0, e8, m2

# SEW= 8, LMUL=2

# SEW=32, LMUL=1/2

vsetvli t0, a0, e32, mf2

```

The vsetvl variant operates similarly to vsetvli except that it takes a vtype value from rs2 and can be used for context restore.

If the vtype setting is not supported by the implementation, then the vill bit is set in vtype, the remaining bits in vtype are set to zero, and the vl register is also set to zero.

Note

Earlier drafts required a trap when setting vtype to an illegal value. However, this would have added the first data-dependent trap on a CSR write to the ISA. Implementations could choose to trap when illegal values are written to vtype instead of setting vill, to allow emulation to support new configurations for forward-compatibility. The current scheme supports light-weight runtime interrogation of the supported vector unit configurations by checking if vill is clear for a given setting.

#### 6.2. AVL encoding

The new vector length setting is based on AVL, which for vsetvli and vsetvl is encoded in the rs1 and rd fields as follows:

| rd  | rs1 | AVL value            | Effect on v1                                   |

|-----|-----|----------------------|------------------------------------------------|

| -   | !x0 | Value in x[rs1]      | Normal stripmining                             |

| !x0 | x0  | ~0                   | Set v1 to VLMAX                                |

| x0  | x0  | Value in v1 register | Keep existing v1 (of course, vtype may change) |

Table 8. AVL used in vsetvli and vsetvl instructions

When rs1 is not x0, the AVL is an unsigned integer held in the x register specified by rs1, and the new v1 value is also written to the x register specified by rd.

When rs1=x0 but rd!=x0, the maximum unsigned integer value ( $\sim0$ ) is used as the AVL, and the resulting VLMAX is written to v1 and also to the x register specified by rd.

When rs1=x0 and rd=x0, the instruction operates as if the current vector length in v1 is used as the AVL, and the resulting value is written to v1, but not to a destination register. This form can only be used when VLMAX and hence v1 is not actually changed by the new SEW/LMUL ratio. Use of the instruction with a new SEW/LMUL ratio that would result in a change of VLMAX is reserved. Implementations may set vill in this case.

NIate

This last form of the instructions allows the vtype register to be changed while maintaining the current v1, provided VLMAX is not reduced. This design was chosen to ensure v1 would always hold a legal value for current vtype setting. The current v1 value can be read from the v1 CSR. The v1 value could be reduced by this instruction if the new SEW/LMUL ratio causes VLMAX to shrink, and so this case has been reserved as it is not clear this is a generally useful operation, and implementations can otherwise assume v1 is not changed by this instruction to optimize their microarchitecture.