Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A . It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is.

from www.slideshare.net

Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. It reviews the measurements used to.

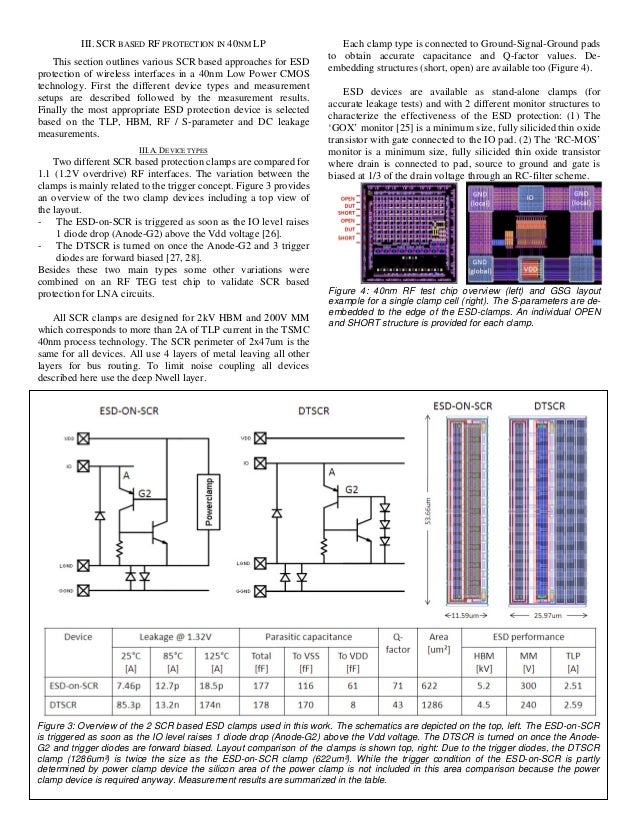

Onchip ESD protection for LNA

Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Leakage current id(vd = 1 v) is.

From www.semanticscholar.org

Figure 1 from COMPACT DEVICE MODELING USING VERILOGAMS AND ADMS Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

(PDF) Compact Models for Simulation of OnChip ESD Protection Networks Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From nanohub.org

Resources Introduction to Compact Models and Circuit Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

[PDF] A FullChip ESD Protection Circuit Simulation and Fast Dynamic Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. This article describes compact models that have been developed in the esd device research community. It reviews the measurements used to. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

[PDF] New Capabilities for VerilogA Implementations of Compact Device Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.slideshare.net

Onchip ESD protection for LNA Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.academia.edu

(PDF) Compact Device Modeling Using VerilogAms and Adms Wladyslaw Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 10 from Compact modeling of onchip ESD protection devices using Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 9 from Design of Compact ESD Protection Circuit for VBand RF Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 1 from Compact modeling of onchip ESD protection devices using Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 3 from A VerilogA compact model for ESD protection NMOSTs Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 1 from A VerilogA compact model for ESD protection NMOSTs Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 16 from Compact modeling of onchip ESD protection devices using Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. It reviews the measurements used to. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.astri.org

Onchip ESD Protection Design For Advanced Silicon Process ASTRI Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Leakage current id(vd = 1 v) is. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

(PDF) A unified approach to compact device modelling with the open Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 1 from A VerilogA compact model for ESD protection NMOSTs Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). This article describes compact models that have been developed in the esd device research community. It reviews the measurements used to. Leakage current id(vd = 1 v) is. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

(PDF) Advances in VerilogA compact semiconductor device modelling with Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Leakage current id(vd = 1 v) is. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From nanohub.org

Resources Introduction to Compact Models and Circuit Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

(PDF) Compact modeling of onchip ESD protection using standard MOS and Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.ednasia.com

Automate ESD protection verification for complex ICs EDN Asia Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 4 from Behavior modeling for wholechip HV ESD protection Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From monthly-pulse.com

Introduction about ESD protection basic concepts to advanced Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 1 from Scalable behavior modeling for nano crossbar ESD Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 1 from Scalable behavior modeling for nano crossbar ESD Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.intechopen.com

LowC ESD Protection Design in CMOS Technology IntechOpen Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.mdpi.com

Materials Free FullText πShape ESD Protection Design for Multi Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

Schematic diagram of the conventional twostage ESD protection circuit Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From ietresearch.onlinelibrary.wiley.com

Systematic transient characterisation of graphene NEMS switch for ESD Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

(PDF) A unified approach to compact device modelling with the open Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Leakage current id(vd = 1 v) is. It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 12 from Compact modeling of onchip ESD protection devices using Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From onlinelibrary.wiley.com

Design of SCR‐Based ESD Protection Circuit for 3.3 V I/O and 20 V Power Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. It reviews the measurements used to. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

(PDF) ESD Simulation using Compact Models from I/O Cell to Full Chip Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Leakage current id(vd = 1 v) is. This article describes compact models that have been developed in the esd device research community. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Compact modeling of onchip ESD protection devices using VerilogA Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.researchgate.net

Typical onchip ESD protection design for input/ output (I/O) pad and Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A It reviews the measurements used to. This article describes compact models that have been developed in the esd device research community. Leakage current id(vd = 1 v) is. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.

From www.semanticscholar.org

Figure 1 from Vertical SCR structure for onchip ESD protection in Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A Leakage current id(vd = 1 v) is. This article describes compact models that have been developed in the esd device research community. Pulsed i−v of a ggnmos (l = 0.25 µm and w = 20 µm). It reviews the measurements used to. Compact Modeling Of On-Chip Esd Protection Devices Using Verilog-A.