This file defines the ClusteredNetlist class in the ClusteredContext created during pre-placement stages of the VTR flow (packing & clustering), and used downstream. More...

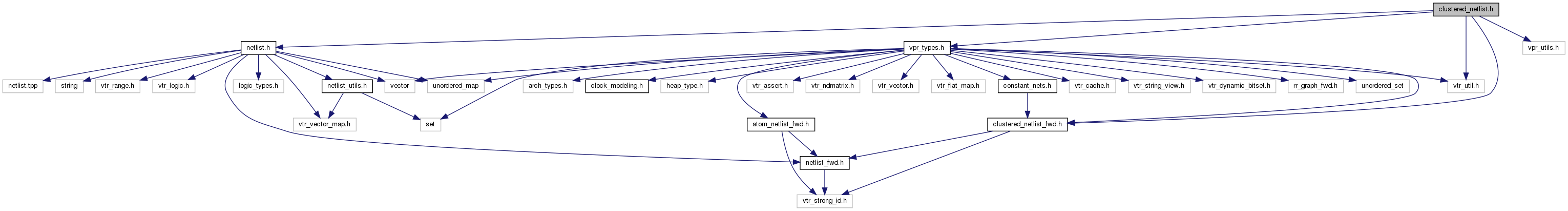

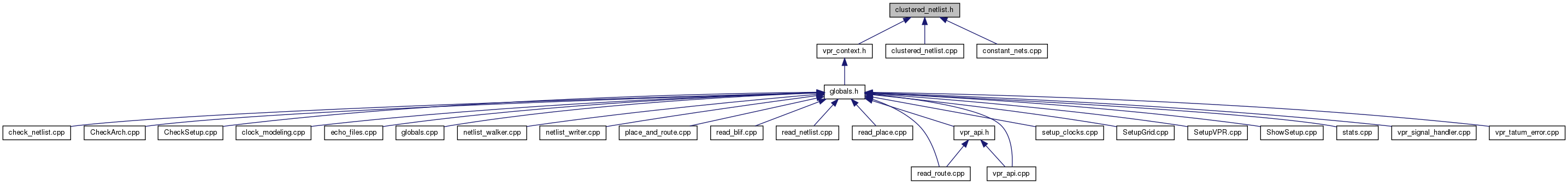

#include "vpr_types.h"#include "vpr_utils.h"#include "vtr_util.h"#include "netlist.h"#include "clustered_netlist_fwd.h"

Go to the source code of this file.

Data Structures | |

| class | ClusteredNetlist |

Detailed Description

This file defines the ClusteredNetlist class in the ClusteredContext created during pre-placement stages of the VTR flow (packing & clustering), and used downstream.

Overview

The ClusteredNetlist is derived from the Netlist class, and contains some separate information on Blocks, Pins, and Nets. It does not make use of Ports.

Blocks

The pieces of unique block information are: block_pbs_: Physical block describing the clustering and internal hierarchy structure of each CLB. block_types_: The type of physical block the block is mapped to, e.g. logic block, RAM, DSP (Can be user-defined types). block_nets_: Based on the block's pins (indexed from [0...num_pins - 1]), lists which pins are used/unused with the net using it. block_pin_nets_: Returns the index of a pin relative to the net, when given a block and a pin's index on that block (from the type descriptor). Differs from block_nets_.

Differences between block_nets_ & block_pin_nets_

block_nets_ tracks all pins on a block, and returns the ClusterNetId to which a pin is connected to. If the pin is unused/open, ClusterNetId::INVALID() is stored.

block_pin_nets_ tracks whether the nets connected to the block are drivers/receivers of that net. Driver/receiver nets are determined by the pin_class of the block's pin. A net connected to a driver pin in the block has a 0 is stored. A net connected to a receiver has a counter (from [1...num_sinks - 1]).

The net is connected to multiple blocks. Each block_pin_nets_ has a unique number in that net.

E.g.

In the example, Net A is driven by Block 1, and received by Blocks 2 & 3. For Block 1, block_pin_nets_ of pin 4 returns 0, as it is the driver. For Block 2, block_pin_nets_ of pin 1 returns 1 (or 2), non-zero as it is a receiver. For Block 3, block_pin_nets_ of pin 0 returns 2 (or 1), non-zero as it is also a receiver.

The block_pin_nets_ data structure exists for quick indexing, rather than using a linear search with the available functions from the base Netlist, into the net_delay_ structure in the PostClusterDelayCalculator of inter_cluster_delay(). net_delay_ is a 2D array, where the indexing scheme is [net_id] followed by [pin_index on net].

Pins

The only piece of unique pin information is: logical_pin_index_

Example of logical_pin_index_

Given a ClusterPinId, logical_pin_index_ will return the index of the pin within its block relative to the t_logical_block_type (logical description of the block).

The index skips over unused pins, e.g. CLB has 6 pins (3 in, 3 out, numbered [0...5]), where the first two ins, and last two outs are used. Indices [0,1] represent the ins, and [4,5] represent the outs. Indices [2,3] are unused. Therefore, logical_pin_index_[92] = 5.

Nets

The pieces of unique net information stored are: net_global_: Boolean mapping whether the net is global net_fixed_: Boolean mapping whether the net is fixed (i.e. constant)

Implementation

For all create_* functions, the ClusteredNetlist will wrap and call the Netlist's version as it contains additional information that the base Netlist does not know about.

All functions with suffix *_impl() follow the Non-Virtual Interface (NVI) idiom. They are called from the base Netlist class to simplify pre/post condition checks and prevent Fragile Base Class (FBC) problems.

Refer to netlist.h for more information.

1.8.13

1.8.13