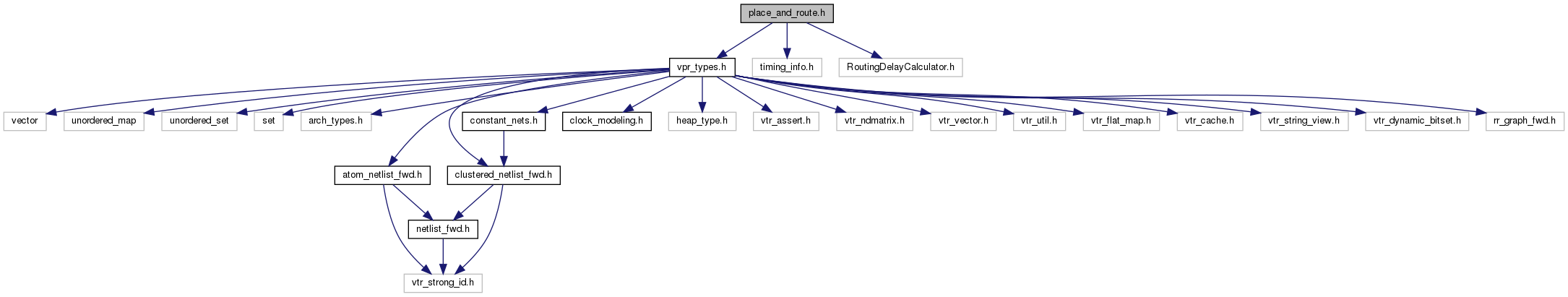

#include "vpr_types.h"

#include "timing_info.h"

#include "RoutingDelayCalculator.h"

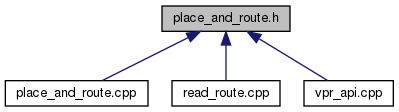

Go to the source code of this file.

|

| int | binary_search_place_and_route (const t_placer_opts &placer_opts_ref, const t_annealing_sched &annealing_sched, const t_router_opts &router_opts, const t_analysis_opts &analysis_opts, const t_file_name_opts &filename_opts, const t_arch *arch, bool verify_binary_search, int min_chan_width_hint, t_det_routing_arch *det_routing_arch, std::vector< t_segment_inf > &segment_inf, ClbNetPinsMatrix< float > &net_delay, std::shared_ptr< SetupHoldTimingInfo > timing_info, std::shared_ptr< RoutingDelayCalculator > delay_calc) |

| | This routine performs a binary search to find the minimum number of tracks per channel required to successfully route a circuit, and returns that minimum width_fac. More...

|

| |

| t_chan_width | init_chan (int cfactor, t_chan_width_dist chan_width_dist) |

| | Assigns widths to channels (in tracks). More...

|

| |

| void | post_place_sync () |

| | After placement, logical pins for blocks, and nets must be updated to correspond with physical pins of type. More...

|

| |

◆ INFINITE

◆ NOT_FOUND

◆ PROC_TIME

◆ WL

◆ WNEED

◆ binary_search_place_and_route()

| int binary_search_place_and_route |

( |

const t_placer_opts & |

placer_opts_ref, |

|

|

const t_annealing_sched & |

annealing_sched, |

|

|

const t_router_opts & |

router_opts, |

|

|

const t_analysis_opts & |

analysis_opts, |

|

|

const t_file_name_opts & |

filename_opts, |

|

|

const t_arch * |

arch, |

|

|

bool |

verify_binary_search, |

|

|

int |

min_chan_width_hint, |

|

|

t_det_routing_arch * |

det_routing_arch, |

|

|

std::vector< t_segment_inf > & |

segment_inf, |

|

|

ClbNetPinsMatrix< float > & |

net_delay, |

|

|

std::shared_ptr< SetupHoldTimingInfo > |

timing_info, |

|

|

std::shared_ptr< RoutingDelayCalculator > |

delay_calc |

|

) |

| |

This routine performs a binary search to find the minimum number of tracks per channel required to successfully route a circuit, and returns that minimum width_fac.

◆ init_chan()

| t_chan_width init_chan |

( |

int |

cfactor, |

|

|

t_chan_width_dist |

chan_width_dist |

|

) |

| |

Assigns widths to channels (in tracks).

Minimum one track per channel. The channel distributions read from the architecture file are scaled by cfactor.

◆ post_place_sync()

After placement, logical pins for blocks, and nets must be updated to correspond with physical pins of type.

This is required by blocks with capacity > 1 (e.g. typically IOs with multiple instaces in each placement gride location). Since they may be swapped around during placement, we need to update which pins the various nets use.

This updates both the external inter-block net connecitivity (i.e. the clustered netlist), and the intra-block connectivity (since the internal pins used also change).

This function should only be called once

1.8.13

1.8.13