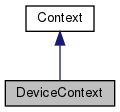

State relating the device. More...

#include <vpr_context.h>

Data Fields | |

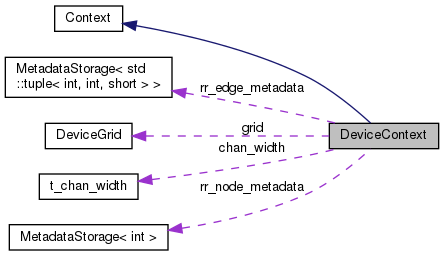

| DeviceGrid | grid |

| t_physical_tile_type_ptr | EMPTY_PHYSICAL_TILE_TYPE |

| t_logical_block_type_ptr | EMPTY_LOGICAL_BLOCK_TYPE |

| std::vector< t_physical_tile_type > | physical_tile_types |

| std::vector< t_logical_block_type > | logical_block_types |

| bool | has_multiple_equivalent_tiles |

| Boolean that indicates whether the architecture implements an N:M physical tiles to logical blocks mapping. More... | |

| t_chan_width | chan_width |

| chan_width is for x|y-directed channels; i.e. between rows More... | |

| t_rr_graph_storage | rr_nodes |

| std::vector< t_rr_indexed_data > | rr_indexed_data |

| std::vector< t_rr_rc_data > | rr_rc_data |

| Fly-weighted Resistance/Capacitance data for RR Nodes. More... | |

| std::vector< std::vector< int > > | rr_non_config_node_sets |

| Sets of non-configurably connected nodes. More... | |

| std::unordered_map< int, int > | rr_node_to_non_config_node_set |

| Reverse look-up from RR node to non-configurably connected node set (index into rr_nonconf_node_sets) More... | |

| t_rr_node_indices | rr_node_indices |

| The indicies of rr nodes of a given type at a specific x,y grid location. More... | |

| std::vector< t_rr_switch_inf > | rr_switch_inf |

| std::vector< t_segment_inf > | rr_segments |

| Wire segment types in RR graph. More... | |

| int | num_arch_switches |

| t_arch_switch_inf * | arch_switch_inf |

| std::vector< std::unique_ptr< ClockNetwork > > | clock_networks |

| std::vector< std::unique_ptr< ClockConnection > > | clock_connections |

| int | virtual_clock_network_root_idx |

| rr_node idx that connects to the input of all clock network wires More... | |

| MetadataStorage< int > | rr_node_metadata |

| Attributes for each rr_node. More... | |

| MetadataStorage< std::tuple< int, int, short > > | rr_edge_metadata |

| Attributes for each rr_edge. More... | |

| std::vector< std::map< int, int > > | switch_fanin_remap |

| switch_fanin_remap is only used for printing out switch fanin stats (the -switch_stats option) More... | |

| const t_arch * | arch |

| t_clock_arch * | clock_arch |

| std::string | read_rr_graph_filename |

| Name of rrgraph file read (if any). More... | |

Additional Inherited Members | |

Public Member Functions inherited from Context Public Member Functions inherited from Context | |

| Context ()=default | |

| Context (Context &)=delete | |

| Context & | operator= (Context &)=delete |

| virtual | ~Context ()=default |

Detailed Description

State relating the device.

This should contain only data structures describing the targeted device.

Field Documentation

◆ arch

| const t_arch* DeviceContext::arch |

◆ arch_switch_inf

| t_arch_switch_inf* DeviceContext::arch_switch_inf |

◆ chan_width

| t_chan_width DeviceContext::chan_width |

chan_width is for x|y-directed channels; i.e. between rows

◆ clock_arch

| t_clock_arch* DeviceContext::clock_arch |

◆ clock_connections

| std::vector<std::unique_ptr<ClockConnection> > DeviceContext::clock_connections |

◆ clock_networks

| std::vector<std::unique_ptr<ClockNetwork> > DeviceContext::clock_networks |

◆ EMPTY_LOGICAL_BLOCK_TYPE

| t_logical_block_type_ptr DeviceContext::EMPTY_LOGICAL_BLOCK_TYPE |

◆ EMPTY_PHYSICAL_TILE_TYPE

| t_physical_tile_type_ptr DeviceContext::EMPTY_PHYSICAL_TILE_TYPE |

◆ grid

| DeviceGrid DeviceContext::grid |

FPGA complex block grid [0 .. grid.width()-1][0 .. grid.height()-1]

◆ has_multiple_equivalent_tiles

| bool DeviceContext::has_multiple_equivalent_tiles |

Boolean that indicates whether the architecture implements an N:M physical tiles to logical blocks mapping.

◆ logical_block_types

| std::vector<t_logical_block_type> DeviceContext::logical_block_types |

◆ num_arch_switches

| int DeviceContext::num_arch_switches |

◆ physical_tile_types

| std::vector<t_physical_tile_type> DeviceContext::physical_tile_types |

◆ read_rr_graph_filename

| std::string DeviceContext::read_rr_graph_filename |

Name of rrgraph file read (if any).

Used to determine when reading rrgraph if file is already loaded.

◆ rr_edge_metadata

| MetadataStorage<std::tuple<int, int, short> > DeviceContext::rr_edge_metadata |

Attributes for each rr_edge.

key: <source rr_node_index, sink rr_node_index, iswitch> iswitch: Index of the switch type used to go from this rr_node to the next one in the routing. OPEN if there is no next node (i.e. this node is the last one (a SINK) in a branch of the net's routing). value: map of <attribute_name, attribute_value>

◆ rr_indexed_data

| std::vector<t_rr_indexed_data> DeviceContext::rr_indexed_data |

◆ rr_node_indices

| t_rr_node_indices DeviceContext::rr_node_indices |

The indicies of rr nodes of a given type at a specific x,y grid location.

◆ rr_node_metadata

| MetadataStorage<int> DeviceContext::rr_node_metadata |

Attributes for each rr_node.

key: rr_node index value: map of <attribute_name, attribute_value>

◆ rr_node_to_non_config_node_set

| std::unordered_map<int, int> DeviceContext::rr_node_to_non_config_node_set |

Reverse look-up from RR node to non-configurably connected node set (index into rr_nonconf_node_sets)

◆ rr_nodes

| t_rr_graph_storage DeviceContext::rr_nodes |

◆ rr_non_config_node_sets

| std::vector<std::vector<int> > DeviceContext::rr_non_config_node_sets |

Sets of non-configurably connected nodes.

◆ rr_rc_data

| std::vector<t_rr_rc_data> DeviceContext::rr_rc_data |

Fly-weighted Resistance/Capacitance data for RR Nodes.

◆ rr_segments

| std::vector<t_segment_inf> DeviceContext::rr_segments |

Wire segment types in RR graph.

◆ rr_switch_inf

| std::vector<t_rr_switch_inf> DeviceContext::rr_switch_inf |

◆ switch_fanin_remap

| std::vector<std::map<int, int> > DeviceContext::switch_fanin_remap |

switch_fanin_remap is only used for printing out switch fanin stats (the -switch_stats option)

array index: [0..(num_arch_switches-1)]; map key: num of all possible fanin of that type of switch on chip map value: remapped switch index (index in rr_switch_inf)

◆ virtual_clock_network_root_idx

| int DeviceContext::virtual_clock_network_root_idx |

rr_node idx that connects to the input of all clock network wires

Useful for two stage clock routing XXX: currently only one place to source the clock networks so only storing a single value

The documentation for this struct was generated from the following file:

1.8.13

1.8.13