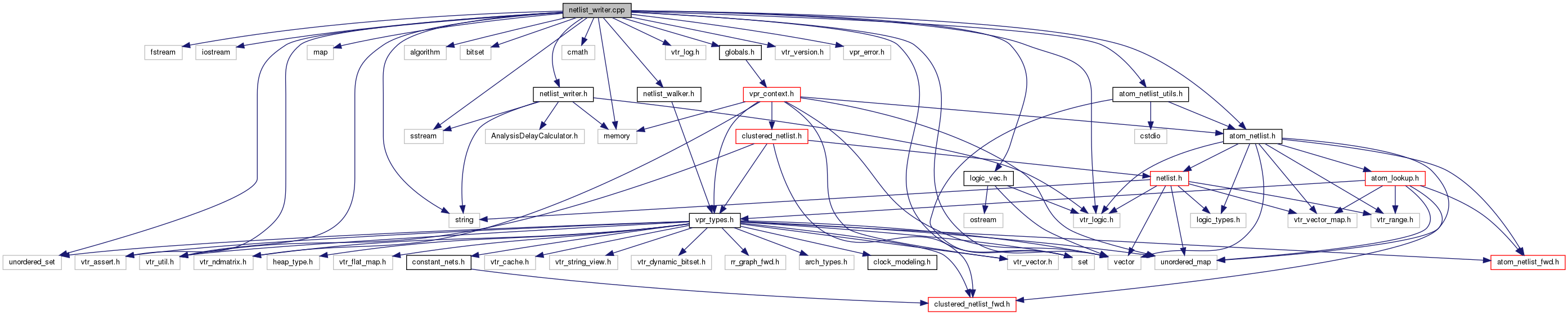

#include <fstream>#include <iostream>#include <sstream>#include <set>#include <map>#include <vector>#include <string>#include <algorithm>#include <bitset>#include <memory>#include <unordered_set>#include <cmath>#include "vtr_assert.h"#include "vtr_util.h"#include "vtr_log.h"#include "vtr_logic.h"#include "vtr_version.h"#include "vpr_error.h"#include "netlist_walker.h"#include "netlist_writer.h"#include "globals.h"#include "atom_netlist.h"#include "atom_netlist_utils.h"#include "logic_vec.h"

Data Structures | |

| class | Arc |

| class | Instance |

| Instance is an interface used to represent an element instantiated in a netlist. More... | |

| class | LutInst |

| An instance representing a Look-Up Table. More... | |

| class | LatchInst |

| class | BlackBoxInst |

| class | Assignment |

| Assignment represents the logical connection between two nets. More... | |

| class | NetlistWriterVisitor |

| A class which writes post-synthesis netlists (Verilog and BLIF) and the SDF. More... | |

Functions | |

| std::string | indent (size_t depth) |

| Returns a blank string for indenting the given depth. More... | |

| double | get_delay_ps (double delay_sec) |

| Returns the delay in pico-seconds from a floating point delay. More... | |

| void | print_blif_port (std::ostream &os, size_t &unconn_count, const std::string &port_name, const std::vector< std::string > &nets, int depth) |

| Pretty-Prints a blif port to the given output stream. More... | |

| void | print_verilog_port (std::ostream &os, const std::string &port_name, const std::vector< std::string > &nets, PortType type, int depth) |

| Pretty-Prints a verilog port to the given output stream. More... | |

| std::string | create_unconn_net (size_t &unconn_count) |

| Returns the name of a unique unconnected net. More... | |

| std::string | escape_verilog_identifier (const std::string identifier) |

| Escapes the given identifier to be safe for verilog. More... | |

| std::string | escape_sdf_identifier (const std::string identifier) |

| Escapes the given identifier to be safe for sdf. More... | |

| bool | is_special_sdf_char (char c) |

| Returns true if c is categorized as a special character in SDF. More... | |

| std::string | join_identifier (std::string lhs, std::string rhs) |

| Joins two identifier strings. More... | |

| void | netlist_writer (const std::string basename, std::shared_ptr< const AnalysisDelayCalculator > delay_calc) |

| Main routing for this file. See netlist_writer.h for details. More... | |

Detailed Description

This file implements the netlist writer which generates post-implementation (i.e. post-routing) netlists in BLIF and Verilog formats, along with an SDF file which can be used for timing back-annotation (e.g. for timing simulation).

The externally facing function from this module is netlist_writer() which will generate the netlist and SDF output files. netlist_writer() assumes that a post-routing implementation is available and that there is a valid timing graph with real delays annotated (these delays are used to create the SDF).

Implementation

The netlist writer is primarily driven by the NetlistWriterVisitor class, which walks the netlist using the NetlistWalker (see netlist_walker.h). The netlist walker calls NetlistWriterVisitor's visit_atom_impl() method for every atom (i.e. primitive circuit element) in VPR's internal data structures.

visit_atom_impl() then dispatches the atom to the appropriate NetlistWriterVisitor member function (e.g. LUTs to make_lut_instance(), Latches to make_latch_instance(), etc.). Each of the make_*_instance() functions records the external nets the atom connects to (see make_inst_wire()) and constructs a concrete 'Instance' object to represent the primitive. NetlistWriterVisitor saves these representations for later output.

'Instance' is an abstract class representing objects which know how to create thier own representation in BLIF, Verilog and SDF formats. Most primitives can be represented by the BlackBoxInst class, but special primitives like LUTs and Latchs have thier own implementations (LutInst, LatchInst) to handle some of their unique requirements.

Once the entire netlist has been traversed the netlist walker will call NetlistWriterVisitor's finish_impl() method which kicks off the generation of the actual netlists and SDF files. NetlistWriterVisitor's print_*() methods setting up file-level global information (I/Os, net declarations etc.) and then ask each Instance to print itself in the appropriate format to the appropriate file.

Name Escaping

One of the challenges in generating netlists is producing consistent naming of netlist elements. In particular valid BLIF names, Verilog names and SDF names are not neccessarily the same. As a result we must escape invalid characters/identifiers when producing some formats.

All name escaping is handled at the output stage (i.e. in the print_*() functions) since it is very format dependant.

VPR stores names internally generally following BLIF conventions. As a result these names need to be escaped when generating Verilog or SDF. This is handled with escape_verilog_identifier() and escape_sdf_identifier() functions.

Primitives

Verilog netlist generation assumes the existance of appropriate primitives for the various atom types (i.e. a LUT_K module, a DFF module etc.). These are currently defined the file <vtr>/vtr_flow/primitives.v, where <vtr> is the root of the VTR source tree.

You will typically need to link with this file when attempting to simulate a post-implementation netlist. Also see the comments in primitives.v for important notes related to performing SDF back-annotated timing simulation.

Function Documentation

◆ create_unconn_net()

| std::string create_unconn_net | ( | size_t & | unconn_count | ) |

Returns the name of a unique unconnected net.

◆ escape_sdf_identifier()

| std::string escape_sdf_identifier | ( | const std::string | id | ) |

Escapes the given identifier to be safe for sdf.

◆ escape_verilog_identifier()

| std::string escape_verilog_identifier | ( | const std::string | id | ) |

Escapes the given identifier to be safe for verilog.

◆ get_delay_ps()

| double get_delay_ps | ( | double | delay_sec | ) |

Returns the delay in pico-seconds from a floating point delay.

◆ indent()

| std::string indent | ( | size_t | depth | ) |

Returns a blank string for indenting the given depth.

◆ is_special_sdf_char()

| bool is_special_sdf_char | ( | char | c | ) |

Returns true if c is categorized as a special character in SDF.

◆ join_identifier()

| std::string join_identifier | ( | std::string | lhs, |

| std::string | rhs | ||

| ) |

Joins two identifier strings.

◆ netlist_writer()

| void netlist_writer | ( | const std::string | basename, |

| std::shared_ptr< const AnalysisDelayCalculator > | delay_calc | ||

| ) |

Main routing for this file. See netlist_writer.h for details.

Writes out the post-synthesis implementation netlists in BLIF and Verilog formats, along with an SDF for delay annotations.

◆ print_blif_port()

| void print_blif_port | ( | std::ostream & | os, |

| size_t & | unconn_count, | ||

| const std::string & | port_name, | ||

| const std::vector< std::string > & | nets, | ||

| int | depth | ||

| ) |

Pretty-Prints a blif port to the given output stream.

Handles special cases like multi-bit and disconnected ports

◆ print_verilog_port()

| void print_verilog_port | ( | std::ostream & | os, |

| const std::string & | port_name, | ||

| const std::vector< std::string > & | nets, | ||

| PortType | type, | ||

| int | depth | ||

| ) |

Pretty-Prints a verilog port to the given output stream.

Handles special cases like multi-bit and disconnected ports

1.8.13

1.8.13